Download Issue - Chip Scale Review

Download Issue - Chip Scale Review

Download Issue - Chip Scale Review

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

JF MICROTECHNOLOGY SDN BHDBring Possibilities .\WeExplore thesenew exciting andoutstanding solutions onour website or with our nearestsales channel partner today.Find out more at:Or e-mail us at:<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]5

MARKET TRENDSMemory Packages Adapt to Demand ShiftsBy Jim Handy [Objective Analysis]The ballooning bandwidthrequirements of today’sprocessors are beingdealt with by increasing the number ofbuses feeding the CPU. Two buses andeven three-bus systems are becomingincreasingly common. What is notobvious is that the size of the memory inPCs is limited by economics: The PC’smain memory doesn’t double or tripleevery time a new bus is added, it hasto remain at the same size to be pricecompetitivewith lower-bandwidth PCs.The system satisfies its bandwidth needby using a larger number of packageswith very low density (i.e., inexpensive)chips inside. This causes lower-densityDRAM chips to remain in the marketlonger than they have in the past. Asthe price of the lower-density chipsdecreases, the overall average sellingprice (ASP) of DRAMs slides (Figure1) putting phenomenal pressure on theprice of DRAM back-end processes(package and test) as these two elementscontribute to an increasing share of thetotal cost of the memory system.Meanwhile, the opposite has beenoccurring in the second-biggestmemory market – NAND flash. Theaverage memory size of NAND flashapplications has been increasing fasterthan the density of the chips in thesesystems, yet the form factor of thesystem (whether a phone handset orother mobile device) has been steadilyshrinking. Thanks to these twoconflicting trends, NAND flash makershave had to stack chips in increasingnumbers to satisfy consumer demandfor mushrooming flash capacities inshrinking product form factors. Twochipstacks, which were uncommon asrecently as 2000, have been supersededby 4-die and 8-die packages. Although16-die packages ship today, the 8-diestack is the tallest stack currentlyshipping in volume, but that mightchange over the next few years.Naturally, since these are consumerproducts, there is significant pressureto keep prices down. NAND makershave found a way to drive all of thecost out of these stacked parts, thanksto a lot of challenging work performedby packaging engineers. I find itamazing that an 8-highstack of 16Gb NANDdice commands no pricepremium over eightindividually-packaged16Gb NAND chips, orfour 2-die stacks, or eventwo four-chip stacks. Inflash cards, such stacksnow very commonlyinclude eight NAND chipsplus a controller.All this has been givena more pronounced impactby the fact that buyersappear to be putting offPC purchases in favor ofmobile devices such assmart phones and tablets.Mobile devices, in turn, are usuallyNAND rich and use only the smallestDRAM. The market is undergoingimportant changes that will create evengreater turmoil for chip makers thanthey have witnessed in the recent past.Today’s technologies have gone aboutas far as they can, though. SixteenlayerNAND stacks have low yieldsthat cannot reach price parity with8-chip stacks. Today’s DRAM packagescan’t support significant increases insignal frequencies and the addition ofbuses multiplies the capacitive loadingon the processor and drives up powerdissipation. The market will have toundergo a revolutionary conversion overthe next few years.The shifts the market has recentlyundergone pale in comparison withwhat’s coming up. Some excitingnew packaging technologies are beingdeveloped that will provide morebandwidth and denser products whileFigure 1:DRAM average selling price is steadily decreasing.the market for these chips will beundergoing very dramatic changes.Let’s see what is ahead in the world ofmemory packaging.What Does the Future Hold?Three important emerging trends willdrive even more extreme packagingover the longer term: 1) Through-siliconvias; 2) Hybrid Memory Cube; and 3)NAND adoption in PCs. Let’s examine6<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]7

each of these in turn.Through-Silicon Vias. Throughsiliconvias, or TSVs, hold the promiseof simplifying inter-chip bondingfor stacked dice. It’s not difficult tounderstand that the sheer complexity ofbonding a 16-die stack using bondingwires alone poses great manufacturingchallenges that lead to yield losses.By moving to TSVs, all wire bondingof the upper chips can be eliminated,and this is expected to significantlyimprove yields for die stacks ofincreasing heights.Although today TSV technologyis not widely used, and presents newchallenges of its own, the same was trueof the standard 2-die MCP (multichippackage) in the middle 1990s. This isa technology that should mature anddevelop to drive out all cost and yieldchallenges over time. It is unclear howhigh of a stack can be economicallymanufactured using TSV technology– we may see stacks of 100 chips ormore over the long term. Imagine theimpact this will have on the density of aNAND package.Hybrid Memory Cube. Since theTSVs mentioned above can be used forinter-chip signaling that doesn’t needto exit the package, chip designerscan design I/O pins that don’t have todrive a PC board trace or be handledduring board assembly. This meansthat high-speed drive transistors canuse low currents (making them muchsmaller than today’s I/O transistors),and that there does not need to bespace-consuming electrostatic discharge(ESD) protection on these I/O pins.In addition, the TSVs replace bulkybonding pads, further reducing the sizeof the chip’s I/O.The inventors of the hybrid memorycube (HMC) took this opportunity todrive an architecture that is likely to beadopted in all higher-end computingsystems over the longer term. TheHMC stacks a number of DRAM chipsatop a logic die; the logic die is the onlychip that communicates external to thepackage. This means that this is theonly device that must have high-currentdrive transistors with ESD protection.Furthermore, it is manufactured usinga logic, rather than a DRAM, process– DRAM processes aren’t good atdriving high currents, so high-currentDRAM transistors are much largerand more expensive than their logicprocesscounterparts.But there’s more to the story!Because the I/O drivers on the DRAMchip are now much smaller than thoseof a standard DRAM, there can be moreof them without penalizing die area.Without large high-current transistors,ESD protection, or bonding pads, theseI/Os are so small that today’s HMCprototypes use thousands of DRAMI/O pins to communicate between theDRAMs and the logic chip, increasingbandwidth substantially.The HMC uses a point-to-pointexternal signaling interface tocommunicate with the processor. Thisgives the system designer considerablymore control over bus capacitance thanexists in today’s DIMM-based systems,and this capacitance is also much lower.This allows the bus to be run at vastlyhigher frequencies than can be donein today’s systems, which should helpthe memory keep up with the everacceleratingprocessor bus. Over time,Objective Analysis anticipates that theHMC could be used for all DRAM inPCs and servers.NAND Adoption in PCsIn 2011, Objective Analysispublished a report: “How PC NANDwill Undermine DRAM.” Through aseries of nearly 300 benchmarks wefound that (after a certain minimumsize DRAM was achieved) one dollar’sworth of NAND flash improved a PC’sperformance more than one dollar’sworth of DRAM. This is somethingthat the IT community has known foryears. Data center managers routinelyuse solid-state drives (SSDs) as a wayof reducing their DRAM requirements,cutting both cost and energyconsumption at the same time.Although PCs have not yet adoptedthis trend, it will occur over time, withDRAM main memory sizes stagnatingand new NAND dual in-line memorymodules (DIMMs) replacing thesmaller SSDs now commonly seen inUltrabooks. Users who wish to improvetheir system’s performance will simplyupgrade their NAND DIMM. As thishappens, DRAM will migrate awayfrom a removable format and will besoldered down. The HMC is very likelyto become the standard way in whichDRAM is built into the PC. DRAMwill become a cache to the NANDmain memory.SummaryWe have seen important changes inmemory packaging technology, movingfrom single-die packages to multiple-diepackages in NAND while experiencinga shift from low package counts tohigh package counts in DRAMs.Both have put significant pressureon packaging costs that have led toimportant innovations.Although we are now approachingthe limits of today’s technologies,new approaches in the form of TSVsand the HMC, are on the horizon thatshould move us well past today’s limitsallowing packaging advances to propelthe two disparate goals of increasingbandwidth for DRAMs while increasingNAND flash package density faster thanMoore’s Law supports.AcknowledgmentUltrabook is a trademark of Intel.BiographyJim Handy received his Bachelor’s inElectrical Engineering from Georgia Techand an MBA from the U. of Phoenix; heis a Director at Objective Analysis; emailJim.Handy@Objective-Analysis.com.8<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

40 + years ofAnd now, the perfect nameTMQi•nex [kuh-nekts] 1. Over 40 years ofreliable burn-in and custom connections;2. Quality interconnects for nex-gen solutions.Introducing Qinex, thenew brand name forsuperior interconnectionsolutions from SensataTechnologies. Qinex, thenew word in perfectpitch.QUALITY. High-value interconnectionsolutions since 1970.• 24/7 global engineering• 24/7 global support teams• Local engineering and sales• Six Sigma quality management• Proven, reliable high-volumemanufacturing• Expert molding, design, andcustomizationINNOVATION. More I/O choices,smaller form factors, superiorperformance in less time.• Latest 3D design tools• On-site model shops• Rapid prototyping• Advanced thermal analysis• Design on demand• Broad range of innovativecontact designsPARTNERSHIP. In a fierce globalmarket, only Qinex reliably supportsthe innovation, reputation andcompetitiveness of your business.We’ll work with you to get it right,the first time.40+ years of perfect pitch.And now, the perfect name.WEB www.qinex.comEMAIL qinex@sensata.comCALL 1-508-236-1306<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]9

GUEST EDITORIALSystems Scaling for Smart Mobile SystemsRequiring a New Packaging PlatformBy Prof. Rao R. Tummala [3D Systems Packaging Research Center, Georgia Institute of Technology]Transistor scaling, startingwith the invention ofthe transistor in 1947,made electronics the largest single$1.5T global industry serving avariety of individual industries thatspan computing, communications,consumer, automotive, bioelectronicsand others. The basis for this industryis a result of singular focus in transistorscaling, leading to a 5B-transistor chip,involving dozens of semiconductorcompanies around the globe. But theelectronics landscape is changingdramatically, driven by a new industrythat integrates all these individualindustries into so-called “smart mobilesystems” and promises to perform everyimaginable function in the smallestsize and lowest cost that almost everyglobal person could afford. Sucha new frontier, however, requiresrevolutionary technologies referred to assystem scaling, in contrast to transistorscaling during the last 60 years. Smartmobile systems are expected to driveunparalleled electronics technologyparadigms in system miniaturization,functionality, and cost. These systemscaling technologies are many thatneed to be explored, developed,integrated, interconnected, tested andmanufactured. These include newelectrical, mechanical and thermaldesigns, new system substrate materialsand processes, integration of ultra-thinactives, ultra-thin passives, miniaturizedand innovative thermal structures, thinfilmpower storages such as batteries,and interconnections between all ofthese. Figure 1 illustrates the currentsize scale in millimeters, showing theFigure 1: System scaling gap from transistor scaling at 20nm node tosystem scaling to 100mm size.10 6 gap between transistor scaling andsystem component scaling.System Scaling Vision of SmartSystemsThe Georgia Tech PRC vision is toexplore system scaling technologiesfrom current milli- to- micro-scale in theshort term and to nano-scale in the longterm, thus providing a revolutionarypath to milli- to- mega-functional smartmobile systems, as implied in Figure 2.Figure 2: System scaling vision from milli-to mega-functional smart systems.Such advances will leadto unparalleled circuitand system functionsthat range from digital,analog, power, RF,wireless healthcare,bio, MEMS andnetwork sensors.Current hardwareapproaches involvepackaging of individualand stacked ICs thatrange from processors,memory, RF, MEMSand sensors as well aspassive components and batteries. Whilesome of these are packaged as twodimensionalMCMs and 3D wire bondand stacked packages, there is verylittle system scaling. As such, mobilesystem companies see an eventual limitto functionality driven by the thicknesslimit of about 6000µm, as shown inFigure 3. Such a limit doesn’t allowother functions requiring other ICsto be added. This limit can be largelyeliminated by changing the currenthardware platform thatinvolves packaging ofICs on flexible or rigidorganic packages andorganic system boards,which present fourmain limitations forsmart systems of thefuture: 1) I/O pitch toless than 50µm withlithographic groundrules below 5-10µmline lithography, 2)thermal performance, 3)mismatch in temperature10<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

Figure 3: Functionality limited by thickness of current system scalingtechnologies (Courtesy of Qualcomm).coefficient of expansion (TCE)-driven,and moisture-driven reliabilities, and4) warpage, as these organic packagesare miniaturized in thickness below100µm, as ultra-thin packages. TheI/O pitch and line lithography limitationstresses on both theinterconnectionsand the ultra-low-kon-chip dielectrics.The warpage is dueto many factorsincluding lowmodulus. Inorganicpackages madeout of glass orsilicon address allthese fundamentalproblems and thusextends I/O pitchmuch below 50µm toas much as 10µm. The new generationSummaryGeorgia Tech proposes to offer anindustry consortium, involving the entireglobal chain for R&D and manufacturing,with a focus on many system scalingtechnologies that include the electricaldesign of glass, silicon and organicinterposers for power, signal, noiseand bandwidth, mechanical design forwarpage and reliability, panel–basedlow cost glass, organic and polysiliconinterposers and packages, 2-5µm largearea lithography and wiring layers, 10-30µm pitch off-chip and low temperatureCu-Cu interconnections, silicon, organicand glass package-to-board level surfaceFigure 4: Area array I/O pitch of a) current organicpackages at 120µm pitch and b) low TCE organicsat 50µm pitch.is a result of via on top of via misregistrationfrom layer to layer due tothe visco-elastic nature of polymers asthese are processed at or above theirglass transition temperature and thus areexpected to be limited to about a 50µmarea array pitch, as shown in Figure 4.The thermal conductivity of polymersis about two-three orders of magnitudeless than silicon. The mismatch in TCEbetween Si and organic is huge, creatingFigure 5: I/O pitch need and organic vs. inorganic regimes for emerging 2.5D and 3D packages(Courtesyof Globalfoundries).of low TCE organic laminates, however,offer an opportunity to extend the I/Opitch from 225µm pitch in 1987 to theircurrent value at 120µm pitch and, in thenear future, to about 50µm pitch. Figure5 shows two regimes therefore, one withextending flip-chip with organics, andthe other with inorganic platforms inextending I/O pitch to new levels, muchbelow 50µm. These can be combinedappropriately and selectively with ultrathinand special component technologiesmade of polymers for dielectrics,liners and stress-relief members; nanomagneticsfor antennas and powercomponents and ultra-high surface areaelectrodes, along with high-permittivitydielectrics for capacitors.mount technology (SMT) assembly, 3Dglass photonics, 3D integrated passiveand active components, among others.Georgia Tech’s PRC involves about 20cross-disciplinary faculty and dozens ofgraduate students.BiographyRao R. Tummala received his PhDin Materials Science and Engineeringat the U. of Illinois and is the JosephM. Pettit Endowed Chair in Electricaland Computer Engineering and theDirector of the Packaging ResearchInstitute at the Georgia Instituteof Technology. He was an IBMFellow prior to Georgia Tech; emailrao.tummala@ece.gatech.edu<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]11

INDUSTRY NEWSSEMI Europe Networking Day toFocus on Embedded PackagingTechnologiesSEMI Europe announced a newNetworking Day focusing on embeddedpackaging to be held on June 27, 2013in Portugal. Hosted by Nanium, in Vilado Conde (Porto, Portugal), the eventwill feature speakers from companiesinvolved in fan-out wafer-levelpackaging (FO-WLP) and in embeddeddie in laminate substrate.Driven by consumer markets andmainly by smartphone products,embedded packaging solutions providethe best power, performance, and areasystem tradeoff by integrating morefunctionalities into a smaller and thinnerpackage. With annual growth forecast atmore than 25% by market analyst firmssuch as Yole Développement, thesetechnologies are already implementedin high-volume cellular phonesand are critical for enabling futureinnovative solutions, including 3Dpackaging solutions.The Networking Day will combinepresentations from companies thatinfluence the industry and offer uniqueadd-ons such as the visit of Nanium’sclean room, the largest FO-WLP300mm facility worldwide, and severalnetworking opportunities includingthe Speed Networking Session andsocial evening events. Speakersfrom ASE Group (Taiwan) andSTMicroelectronics (Switzerland) willkeynote and share the latest results oftheir work in embedded packaging andtheir respective strategies. ASE Groupwas a very early adopter of the firstgenerationof FO-WLP (licensed eWLBtechnology developed by Infineon),starting with 200mm capabilities, andnow very active in embedded die insubstrate. STMicroelectronics, one ofthe founding members with Infineon andSTATS <strong>Chip</strong>PAC, of an R&D alliancein Singapore to advance the eWLBplatform back in late 2009, developeda wide range of technology optionsaround FO-WLP to serve its variousproduct groups addressing multiplemarket segments.Presentations from TechSearch(USA) and Yole Développment(France) will describe the technologylandscape, market and main players.Additional speakers from Intel MobileCommunications, AT&S, and NXPare confirmed.“We are pleased that we developedsuch a strong lineup of speakersfrom the main players designing,manufacturing and selling embeddedpackages all over the world,” saidHeinz Kundert, SEMI Europe President.“We are still at an early stage, manyadditional business opportunities inembedded packaging are still upfrontfor equipment and materials companies.Embedded packages have the potentialto become the new packaging platformbeyond the BGA solution.”The full event program is online andregistration is open. Anyone involvedin advanced packaging is invited toregister. The Networking Days area SEMI Europe initiative to supportstart-ups, SMEs, laboratories and largecompanies and to get “up to date” onhot topics that appeal to people acrossthe semiconductor supply chain. SEMINetworking Days, held on a quarterlybasis in industrial sites, are primeevents to connect with the people whoinfluence the industry and to initiatepreliminary partnership and businessrelationships. The Networking Days areopen to anyone and free of charge forSEMI member companies. For moreinformation about the event, please visitwww.semi.org/eu/node/8481 or contactYann Guillou in the SEMI EuropeGrenoble Office (yguillou@semi.org).SEMI: Memory, Foundry, and LEDMarkets Drive Fab Spending inSoutheast AsiaIn early April, SEMI reported thatincreased spending in NAND andflash by Micron, LEDs by Philips andOsram, and continued investmentsby Globalfoundries, will create newopportunities for equipment andmaterials suppliers in Southeast Asia.The trade group noted that, for theSoutheast Asia region, capital equipmentinvestment will see some pickup inthe second half of 2013 followed bya strong recovery in 2014. Overall,front-end fab equipment spending isexpected to double next year from $810million in 2013 to $1.62 billion in 2014.Foundry and memory are the two majorsectors that invest most in the region.The Globalfoundries expansion plan atFab 7 will be completed by mid-2014,while UMC continues to upgrade itsFab 12i capacity to the 40nm process.The Southeast Asia region’s capacitygrowth for front-end fabs shows a 2%increase this year and an expectation ofhigher growth, 8%, in 2014, exceedingoverall global capacity growth of 5%according to the SEMI World FabForecast. The growth will mainly bedriven by memory sector, specificallyfrom NAND flash capacity as Microngears up for further expansion at itsSingapore NAND flash facility nextyear, plus ongoing capacity conversionfrom DRAM to NAND flash at Fab7 (Tech). Singapore is emerging tobecome the third largest NAND flashmanufacturing country in the world bythe end of 2014. The conversion andthe expansion projects will drive relatedsemiconductor investment in the regionin 2013 and 2014.For the assembly and test sector,Southeast Asia has long been thefocal point of the industry with a largeinstalled capacity from both IDMs and12<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

OSATs. This position contributes tothe region being the largest packagingmaterials consumption market in theworld, representing a market size of$6.6 billion in 2013 and $6.8 billion in2014. The region’s back-end equipmentinvestment remains significant withover $1 billion spending each yearthroughout 2012 to 2014, accountingfor about 17% of worldwide shareaccording to SEMI’s WWSEMS.Aside from manufacturing capacity,the Southeast Asia region is nowextending its value proposition to ICdesign and R&D areas with more jointdevelopment projects between multinationalcorporations (MNC) and localinstitutes. SEMI expects to see a morerobust semiconductor ecosystem arisefrom the region as a result of theseendeavors and as companies seek readyaccess to customers throughout Asia-Pacific and South Asia.Currently, Singapore has 14 waferfabrication plants, including the world’stop three wafer foundries. Singaporealso has 20 semiconductor assemblyand test operations, including three ofthe world’s top six outsourced assemblyand test companies. There are about40 IC design centers that comprisenine of the world’s “top 10” fabless ICdesign companies.Imec Reports 6.7% Growth for 2012Fiscal Year EndImec reported financial resultsfor fiscal year ended December 31,2012. Revenue for 2012 totaled 320million euro, a 6.7% increase from theprevious year. The 320 million eurofigure includes the revenue generatedthrough collaborations with more than600 companies and 200 universitiesworldwide, a yearly grant from theFlemish government totaling 48.2million euro, and a 8.2 million eurogrant from the Dutch governmentto support the Holst Centre. “Wecontinued to expand and renew ourR&D partnerships on semiconductortechnology scaling, as well as on newemerging areas such as the biomedicalfield,” said Luc Van den hove, CEO ofimec. “Our robust growth last year is atestament to the strength and value thesepartnerships add to the developmentof next-generation technology andits applications.”In 2012, imec’s talent base grewto 2,051 people, representing 75nationalities. Of these, 377 wereresidents, visiting researchers from<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]13

partner companies and institutes, and276 were PhD researchers. One-hundredtwenty-two employees are based atthe Holst Centre, an open-innovationinitiative between imec and TNOlocated in Eindhoven, the Netherlands.“Given the current challengingeconomic backdrop, I am thrilled withthe steady growth we have realizedthe last two years,” said Van den hove.“Thanks to the efforts and talent of ouremployees, as well as the strength ofour strategic research partnerships, weachieved significant breakthroughs in allour research areas.”Among the highlights of the 2012R&D report include: 1,064 peerreviewedarticles published, 161 patentsawarded, 133 patent applicationssubmitted, and the successful renewalof the IOS9001 quality certification.Yole Développement <strong>Issue</strong>sForecasts in MEMS and Glass WafersRecent forecasts by YoleDéveloppement covered the MEMSpressure sensor market, and the glasswafer market:MEMS Pressure Sensor MarketAfter years of limited growth,Yole Développement reported thatthe MEMS pressure sensor market isgrowing due to consumer electronicapplications and is expected to showa 22% CAGR. Pressure sensors areplaying an important role today inmodern industries. MEMS pressuresensors are already widely adopted indifferent applications for their highperformance,low cost and small size.In its new report “MEMS PressureSensor,” Yole Développement givesa detailed overview of the MEMSpressure sensor markets, technologiesand players. This report details the mainapplications in automotive, consumer,medical, industrial and high-endsegment, and the main players in theindustry. It also analyzes the currentpressure sensor technologies includingMEMS technologies, and gives adetailed MEMS pressure sensor marketforecast by application.Emerging consumer applicationsare boosting the growth of the MEMSpressure sensor market and reshufflingthe main playersThe MEMS pressure sensor is oneof the very first MEMS componentsappearing in the microsystem world.The technologies are quite mature andthe market is big and expected to growfrom $1.9B in 2012 to $3B in 2018(Figure 1). “The MEMS pressure sensorfor consumer applications, especiallyfor smartphones and tablets, isfollowing the model of accelerometersand gyroscopes. Adoption of this modelwill help the MEMS pressure sensormarket to boom again! We believe,this huge opportunity will result in theglobal volume of the MEMS pressuresensor market hitting 2.8 billion unitsby 2018,” announced Wenbin Ding,Technology & Market Analyst, MEMSDevices & Technologies at YoleDéveloppement. “Consumer pressuresensors will represent 1.7 billion unitsand will overtake automotive as themarket leader in volume,” she added.Even though the consumer applicationhas a much lower ASP than otherapplications, this promising segmentFigure 1: MEMS pressure sensor market forecast by applications 2012-2018.SOURCE: MEMS Pressure Sensor report, April 2013, Yole Devéloppement.will bring more than 8% CAGR to theglobal MEMS pressure sensor market.The report consolidated market data for2012 and provides forecasts until 2018.Automotive applications are stilldominating the MEMS pressure sensormarket. TPMS, MAP and BAP willbe the biggest sub applications in thisfield, noted Yole. Automotive, medical,industrial and high-end markets aregrowing 4% to 7%, however, theconsumer market is growing 25% invalue (38% in volume) because of newopportunities in smartphones and tablets.The MEMS pressure sensor findsnew applications in each domain, forexample: in-cylinder pressure sensingfor automotive, the CPAP (continuouspositive airway pressure) machine formedical use, smartphones (SamsungGalaxy Slll for indoor navigation) andtablets for the consumer electronicsindustry, etc. All these emergingapplications are still in their infancy,but they appear promising and YoleDéveloppement’s analysts believe theMEMS pressure sensor will find newways to satisfy end users in each domain.Glass Wafer MarketYole Développement recentlyannounced results from its glasssubstrates for semiconductormanufacturing report.The research firm notedthat over the last fewyears, glass has gainedconsiderable interestfrom the semiconductorindustry due to its veryattractive electrical,physical and chemicalproperties, as wellas its prospects fora relevant and costefficientsolution. Theapplication scope ofglass substrates in thesemiconductor fieldis broad and highlydiversified. End14<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

applications include: MEMS, CMOSimage sensors, LED, memory and logicICs, RF/analog ICs, power, microbatteries,optoelectronic components,and microfluidics. Functionalitiesinclude support substrate,WLCapping, 3D through-glass via(TGV)/2.5D interposer, carriers, andmicro-structuring.Mainly driven by the wafer-levelpackaging industry, Yole expects theglass wafer market to grow from $158Min 2012 to $1.3B by 2018, at a CAGRof ~41% over the next five years (Figure2). “Initially driven by CMOS imagesensor and MEMS applications, thisgrowing industry will be supported byrelevant end-applications such as LED,memory and logic IC, where glass ison its way to being commercialized,”said Amandine Pizzagalli, Marketand Technology Analyst, Equipment& Materials Manufacturing, at YoleDéveloppement. “In terms of wafersshipped, a 4X glass wafer growth isexpected in the semiconductor industryover the next five years, achieving morethan 15M 8” EQ [wafer starts per year]WSPY by 2018.”The glass WLCapping platform is amature functionality already adoptedwith significant volume in CMOSimage sensors, where more than 3.3Mglass caps were shipped in 2012. Thismarket is expected to grow slowly,with a CAGR of 14% from 2012-2018,mainly supported by MEMS devicesimpacted by the request for furtherminiaturization. On the flip side, theglass market for WLOptics will likelydecline from 2015-2018 because of thedevelopment of competing technologies.Despite the above considerations,Yole expects to see strong growth inthe glass market, mainly supported bytwo emerging WLP platforms: with aCAGR of 110% and 70% respectively,the glass-type 2.5D interposer emergingplatform and the carrier wafer will beglass’s fastest-growing fields over thenext five years, because glass offersthe best value proposition in terms ofcost, flexibility, mechanical rigidity andsurface flatness.If glass is qualified for 2.5Dinterposer functionality, the glassmarket could exceed $1B in revenueby 2018. However, it’s still unclearhow back-end-of-line (BEOL) waferfabs will choose glass over the currentsilicon technology used for logic ICapplications (for the 2.5D/3D systemon-chip(SoC) and system partitioningareas), but the glass variety of 2.5D(continued on Page 46)PHOTOLITHOGRAPHYFOR TSV AND 3D-ICEVG ® 150 Resist Processing SystemConformal Coating in Vertical ViasExposure with Proximity LithographyIn-Via Resist DevelopmentGET IN TOUCH To Discuss Your Manufacturing Needs: www.EVGroup.comVia processed on EVG ® systems<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]15

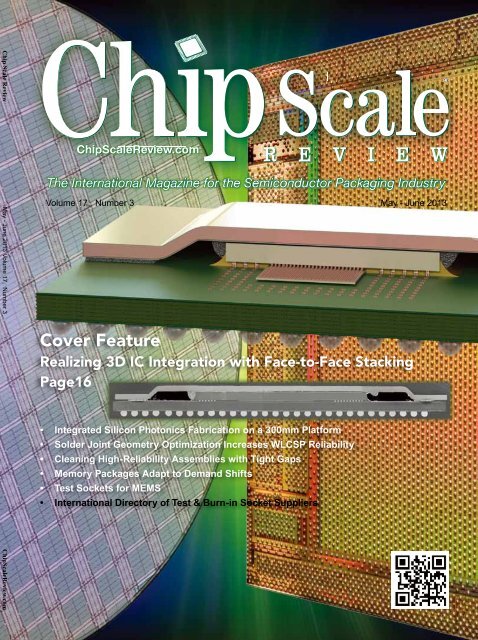

Realizing 3D IC Integration with Face-to-Face StackingBy John Xie [Altera Corporation] and Deborah Patterson [Amkor Technology, Inc.]Semiconductor processscaling, as driven byMoore’s Law, hasbeen the key driving force behindthe evolution of today’s high-techindustry. But increasingly, traditionalprocess scaling alone can no longermeet system performance, throughputand power requirements. Althoughside-by-side monolithic silicon (2Dstructures), package-on-package(PoP), and package-in-package (PiP)platforms allow for two or more chipsto be bonded together, they do not offerenough density, bandwidth or powerto meet the requirements of nextgenerationproduct roadmaps.The trade-offs between placing morefunctions on a chip (system-on-chip,SoC) versus placing more functionswithin a package (multi-chip package,MCP, or system-in-package, SiP) mustbe fully evaluated. Optimizing overallperformance as well as total cost-ofownershipare equally important. Andperhaps one of the most significantissues is accelerating time-to-market, asit is a strategic enabler to the end users.To properly assess the above tradeoffsin terms of effective silicon usagevis-à-vis functional integration (nodeoptimization), die yield considerationsfrom ramp to production, and theinfluence of the packaging strategy onsignal integrity − ideally the packagewould be invisible to the signal whileproviding protection, thermal dissipation,etc. − both 2.5D and 3D packaging arebeing actively investigated.An example of a 3D integrated circuit(IC) is represented by stacked ICs withthrough-silicon vias (TSV). In a 3D ICstack, solder bumps are used to join onedie on top of another to allow the signalsto travel between the die. 3D IC stackscan be packaged independentlyor can be connected side-bysideon a substrate to otherICs. A 2.5D IC package, incontrast, is defined by the useof a multilayer passive siliconinterposer as a substrate tointerconnect multiple activedie or die stacks in a sideby-sideconfiguration. TSVsare used to route the signalsthrough the silicon interposerdown to flip-chip solder bumpslocated on the interposer’sbottom side. The ICs themselvesuse much smaller copper (Cu) pillarmicro-bumps for assembly onto thesilicon interposer.Using silicon as a platform forinterconnecting the active ICspreserves signal integrity far betterthan conventional substrate materialsand, in fact, enables new ways ofthinking about SoC versus MCP tradeoffs.The 2.5D package offers silicongradeinterconnect density and greatlyreduced signal latency because of theshort interconnect path between theactive silicon die. Power consumptionis also reduced because of I/O driversthat can be designed with Si-Si directinterconnect and reduced Joule loss onthe interconnect path. 2.5D stacking alsohas a time-to-market advantage because3D ICs require longer lead times toimplement design and manufactureat the component level, and then tocoordinate their concurrent assembly.The performance advantages of stackedICs are illustrated in Figure 1, whichcompares the relative interconnectdensity, thermal resistance, and powerusage between monolithic, 2.5D, and3D IC packages.The advantages of 2.5D stackedFigure 1: Comparison of the relative interconnect density, thermalresistance and power usage between three types of stacked multichippackages.packaging have ushered in a newmindset on how to approach SoC versusMCP packaging and their combinedimpact upon near- and long-term siliconand package functional integrationroadmaps. Aside from 2.5D and 3Dsemiconductor packaging approaches,there are still other innovative waysto increase function and performancewhile keeping package footprints smalland supporting time-to-market goals.Realizing that an optimized stackingconfiguration, coupled with a properdesign and manufacturing flow canenable a relatively low cost stackedstructure, Altera Corporation and AmkorTechnology collaborated on the projectroadmap for functions: for example,whether to use an SoC, or to re-architecta device, separating it into pieces toincrease die yield.Introducing an ‘About Face’Stacking innovation is a key focus formany semiconductor suppliers as wellas packaging and assembly companies.Altera’s internal R&D organizationhas produced a five-year roadmap forstacking technology. Similarly, Amkor’sadvanced development team supportsnumerous stacked manufacturing and16<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

assembly approaches involving bothwire bond and flip chip solutions.A “face-to-face” packaging approachrepresents one type of stacked chipon-chip(CoC) arrangement. Two dieare joined face-to-face through copperpillar micro-bumps in order to make theconnection between the active circuitryon each die closer - without havingto add any TSV processing. One diemust be sufficiently larger than theother (mother) such that all of its dieto-substrateflip-chip bumps are placedaround the larger die’s perimeter, withthe smaller die (daughter) attachedinside. The daughter die and its bondedCu columns must be thinner than thecollapsed flip-chip bumps surroundingit, to ensure sufficient clearance betweenit and the next assembly surface. Figure2 illustrates an example of this structure,dubbed the POSSUM packageconfiguration by Amkor.Figure 2: Illustration showing a face-to-face chipon-chipassembly that brings the active circuitryon each IC as close as possible without the useof TSVs. The larger die (mother) is assembled tothe BGA substrate through flip-chip solder bumps(shown) or Cu pillar bumps/posts and the smallerdie (daughter) is joined to the mother die throughcopper pillar micro-bumps.The key feature of this packagingstyle is that it bonds two active ICsdirectly using Cu pillar micro-bumpswithout the need for TSVs or a siliconinterposer. In fact, the structureuses established flip-chip substrateand assembly technology. It offersalmost all of the true 3D IC stackingadvantages: the stacked chips talkdirectly to each other with reducedlatency, better signal quality, andadditional power savings as comparedwith a 2.5D structure. The footprint isreduced and the stack does not growin the Z-axis. Integration cost is alsomuch lower than in 2.5D stacking. Theface-to-face flip-chip structure alsonegates the complicated design and highmanufacturing costs associated withintegrating TSVs into active silicon.Face-to-face stacking offers severalpackaging options. In addition to face-to-face flip-chip chip scale package(CSP) or ball grid array (BGA)packaging, lead frame packaging hasalso been demonstrated (Figure 3).Face-to-face PBGA represents the mostadvanced of these packages as it utilizesa POSSUM mounted die assembledto the face of a larger die.Figure 3: Illustration of three different face-to-face chip-on-chippackage configurations.Circumventing the Cost vs. DensityTrajectoryAs I/O density increases, the relativecost of packaging also increases. Figure4 sets as a baseline a typical 2D flipchipBGA (FCBGA) shown at the lowerleft corner of the chart. With a 100µmminimum I/O pitch and 10µm silicontrace width (which cannot be matchedoff-chip), the trend is toward an increasein cost as increasing I/O density andsmaller feature size progress. The finerpitches and line widthscharacterized by anultra-high density I/O(UHDI-O) device, andthat of the sub-50µmpitches that enable 2.5Dinterposer structuresconfirm the predictablecost progression.Against this backdrop,note that face-to-faceassembly, be it Cupillar flip-chip or wirebonded interconnect,deviates from this lineback toward a lowercost offering.Applications of Face-to-FaceStacking TechnologyThere are a number of semiconductorcombinations that will benefit from aface-to-face stacking approach. Forexample, a high-density FPGA maybe bonded with an ASIC to providea combination of ASIC performanceand FPGA flexibility ina specific applicationspace. Perhaps themost obvious use isto combine two dicefabricated in differenttechnologies, such as anRF front-end die and anFPGA die. Face-to-facebonding gives sufficientbandwidth between thetwo devices to allow fordirect digital interactionwith the RF circuitry.Similarly, bonding anFPGA to an externalmemory die can greatlyexpand the FPGA’s access to lowlatencymemory without incurringthe energy costs of high-frequencychip crossings.As system throughput demands andworking-storage bandwidths increase,the memory energy issue looms large.Figure 5 compares the switching powerneeded per I/O channel for differentmemory solutions. It shows that face-tofaceSRAM stacking offers essentiallythe same power and bandwidthadvantage as a true 3D IC stack.Figure 4: Illustration of packaged IC cost progression as I/O density increases.<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]17

Figure 5: Simulated data demonstrating that face-to-face assemblyof an SRAM onto an FPGA offers the same power and bandwidthadvantage as a 3D TSV stacked die structure (MLAB is referring toembedded memory or the SOC option).Nurturing a 3D PackagingAlternativeConsideration of the design andresponse of semiconductors and theirpackaging in parallel is important andgreatly influences downstream technicaldirection, especially when the designmust concurrently optimize total costof-ownership,product performance,and time-to-market. This awarenesssupports early partnering between theIC supplier and the OSAT (outsourcedsemiconductor assembly and test serviceprovider). This broad combination ofexpertise, resources and experience isrequired in identifying viable packagingtechnologies that support aggressiveproduct roadmap objectives.The face-to-face POSSUM packageprovides an example of this blendingof expertise. The structure was chosendue to its ability to join two or moredie with closer coupling for shorter,faster communication. Less inductance,cross talk and parasitic resistancemeant that the method was suitablefor high frequency, high bandwidthapplications. And the package wasbased on established process flows thatwere already in production, such as Cupillar micro-bumping, flip-chip solderbumping, chip-on-chip mass reflow and/or thermo-compression bonding, chip-tochipwire bonding, or chip-to-substrateflip-chip or wire bonding, as appropriate.In addition, the package could beramped to high-volume manufacturingwithout introducing complexwafer handling processes.Face-to-Face <strong>Chip</strong>-on-<strong>Chip</strong>AssemblyThe platform supportingCoC assembly is a directresult of the combination ofcopper pillar wafer bumpingknow-how and its advancedfine pitch assembly. Thespecifics of the bumping aretailored to the product designand assembly process flow.After the copper pillarmicro-bumps are applied tomother and daughter wafers,back grinding and dicingare performed. There is the optionto separate the mother die or for itto remain in wafer form, dependingon process flow optimization. Thedaughter die is then joined to themother die using Cu pillar microbumps.Various bump structures,interconnection materials and processesto control bump standoff (e.g., noncollapsiblecore) are being investigatedto provide for optimal reliability,electrical, and thermal performance. Cupillar micro-bumps are in high-volumemanufacturing at 40µm peripheral and80µm staggered pitch, and in lowvolumeproduction at 30µm peripheraland 60µm staggered pitch.Multi-Bump Height Flip-<strong>Chip</strong>ImplementationFor the current face-to-faceconfiguration, a taller Cu pillar microbumpis created on the daughter die anda shorter height bump is formed on thelarger mother die. Figure 6 illustrates aclose up of the concept where the dualsize bumps are joined between motherand daughter die.Note that the structure also utilizesFigure 6: Close-up view of the dual size copperpillar micro-bumps used to join the mother (top)and daughter (bottom) die in a face-to-faceconfiguration (not to scale).advanced dual height bumping for thelarger mother die. The CoC die padregion is bumped with the shorter bumpswhile the peripheral region outside theCoC bonding area is bumped with thetaller copper pillar micro-bumps.Assembling a 3D Package WithoutTSVsThere is a choice of two chip attachassembly processes for face-to-face Cupillar bonding. The first is mass reflowwith capillary underfill (MR+CUF),which is typically used for bump pitch>80µm with migration to >50µm.The second chip attach assemblyprocess is thermo-compression bondingwith non-conductive paste (TC+NCP).This process is currently used in highvolumemanufacturing production fordie with 40/80µm I/O pitch for die-tolaminatesubstrates and has been foundto be high yielding and reliable.The TC+NCP assembly processis employed to join the mother anddaughter ICs. Upon completion ofthis face-to-face assembly, the bondeddice are then attached to the substratethrough a mass reflow process. It iscritical to maintain a proper underfillflow that is uniform across the gapbetween the mother and daughter ICsin order to avoid the formation of airpockets after underfill cure. The processwas refined to ensure void-free underfilland proper gap collapse between themother and daughter die. Both variationof the die and substrate warpage aretaken into consideration. The assemblyof the devices onto the substrate is thenfollowed by lid attach, ball attach, lasermarking and test. Figure 7 shows across-section and various close up viewsof the assembled package.On-going development continuesto advance the sphere of influenceof chip-on-chip assembly. <strong>Chip</strong>-on-Wafer (CoW) processing, which utilizesequipment and process methods wherethe smaller die is attached directly tothe larger die while it is still in waferform, are in development. CoW alsoprovides for the support of wafer-levelchip scale packaging (WLCSP) withinthe POSSUM platform. Advances18<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

Figure 7: Cross-section of a FPGA die (mother) with a thinned 60µm ASICdie below (daughter). The two devices are assembled face-to-face throughan array of 40µm Cu pillar micro-bumps. The ASIC is joined to the substratethrough thicker Cu posts + solder microballs at a pitch of 200µm.in materials across all 3D platforms aresimilarly adoptable to CoC applicationas they become available.Temperature cycle tests have beenconducted on packages using the Cu+ SnAg solder caps. The packageshave passed -55°C to 125°C for 2000temperature cycles (JESD22-A104D,Level B). Other packages using Nibumps + SnAg that are joined to Cupillar + SnAg have withstood -55°C to125°C for 3000 temperature cycles.3D IC integrationwith TSVs remainsan industry target,there are clever waysto address low-coststacking in the nearterm. Face-to-faceflip-chip packaging isexpected to producecomplex, highlyintegrated, andhigh performanceproducts for a vastarray of computing,communications,automotive andconsumer products.This is especiallyimportant for devices with theprogramming flexibility of FPGAswhere ever increasing functionality anddecreasing size and weight are required.AcknowledgementsThe authors would like to thank MJLee, Yuan Li, Zhe Li and the Alterapackaging R&D team in both San Joseand Penang, as well as Jemmy Sutanto,DongHe Kang, Michael Oh, Kwang-Seok Oh, KyungRok Park, Sa YunMa, Robert Lanzone, Dave Hiner, RonHuemoeller and their advanced productdevelopment teams from AmkorTechnology and Amkor TechnologyKorea for their joint contributions tothis project.BiographiesJohn Xie received his PhD inPhysics from the Chinese Academy ofSciences with post-doctoral researchat UC Berkeley and LawrenceBerkeley Labs; he is the Director ofPackaging Technology Research andDevelopment at Altera Corporation; emailjxie@altera.comDeborah Patterson received her BS inEngineering from the U. of California,San Diego and is the Sr. Director ofProduct and Technology Marketingat Amkor Technology, Inc.; emaildeborah.patterson@amkor.comSummaryUpstream concurrent IC and packagedevelopment allows for the assimilationof cost effective packaging solutionsthat optimize the right set of featuresin order to support the varied andaggressive requirements of end users.In a short period of time, the jointdevelopment team has made tremendousprogress on silicon bump design andmanufacture, substrate structure andprocess, and assembly BOM andmanufacturing flow. The team ispursuing several other types of stackingapproaches and their integration intoestablished packaging platforms (e.g.,from wire bond and flip-chip to BGAsand lead frames).The POSSUM configurationillustrates how face-to-face packagingcan be optimized to leverage highperformance in a multi-chip assemblywithout the use of expensive 2.5D or3D TSV constructions. Although fullSockets, Contactors & Adaptersfor Prototype Development & Test• Compatible with virtually any footprint• Probe-pin & Elastomer solutions• Pitch range from 0.30mm to 2.54mm• Pin counts up to 2000• Bandwidth to 40GHz• SMT, thru-hole & solderless options• Several socket closure styles available• Custom requirements are welcome• Competitive pricing• Expedited deliveryFor further information visit www.e-tec.comor contact us directly for immediate attentionE-Tec Interconnect Ltd, USA Marketing & SalesE-mail: info-US@E-tec.com, Telephone: +1 408.746.2800(www.e-tec.com)<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]19

Integrated Silicon Photonics Fabrication on a300mm PlatformDouglas Coolbaugh, Thomas N. Adam, Gerald L. Leake, Phung Nguyen, Michelle L. Pautler [College of Nanoscale Science and Engineering]Jonathan Bradley, Ehsan Hosseini, Michael Watts [Research Laboratory of Electronics, Massachusetts Institute of Technology]The College of NanoscaleScience and Engineering(CNSE) working incollaboration with the MassachusettsInstitute of Technology (MIT) hasdeveloped a full flow photonicsprocess on 300mm silicon-oninsulator(SOI) and bulk wafers.This offering encompasses multilevellow-loss silicon and siliconnitride waveguides, high speedgermanium detectors, and activeelectro-optical components that canbe co-integrated with advanced 65nmlow power CMOS base technologiesusing 3D integration (Figure 1).These derivatives were developed forintegrated photonic solutions and otheroptoelectronic applications. Stateof-the-artindustry-leading 193nmimmersion photolithography and afully equipped 300mm research fabenabled the successful incorporationof nanophotonic elements with highendCMOS base technologies and afully developed 3D integration process.Basic and advanced process flowswere employed for standard photonicsapplications in conjunction with CMOSFigure 1: Fully equipped 300mm CMOS and photonics cleanroom facilities.and 3D integration. In addition, researchlevel photonics can be modified forspecific customer requirements, andnovel materials and prototype devicescan readily be developed and tested.Integrated CMOS-compatibleWaveguidesIntegrated photonics circuits requirewaveguides that transport optical signalsbetween components on one chip aswell as on and off the chip. While signaldispersion can be neglected for theserelatively short distances, the lowestabsorption is needed to balance the lowdetector sensitivity and small opticalgain in on-chip amplifiers and sourcesof today. In addition, a wide range ofwavelengths (633nm to 1550nm) isneeded for specialized applications thatrequire guiding, mixing, or pumpingwith sources using shorter wavelengths.Most common integrated waveguidesand resonators are of rectangularor ridge geometry and fabricated insilicon (single- or poly-crystalline) orsilicon nitride. Single-level designsfor components test applications werebuilt using either silicon or siliconnitride as the waveguiding layer. Twoleveldesigns were implemented todetermine coupling efficiencies andtest modulators, switches, and opticallypumped components. Multiple-levelphotonics circuits were integrated withfull-build CMOS logic to demonstratefully functional opto-electronic circuits.Leading-edge 193nm immersionlithography with sub-60nm resolutionand advanced reactive ion-etchingwas used to pattern waveguides withminimal loading effects, negligibleinter-level misalignment, and nearlyperfect rectangular shape (sidewallangle of 90±1degrees). The residualsidewall roughness caused by lineedgevariations during the lithographyprocess as well as random geometricfluctuations stemming from reactiveionetching was eliminated using acombination of dose and focus offsets,tone reversal, and thermal and oxidation/etching processing. As depicted inFigure 2, sub-100nm features (gaps,holes, lines) were obtained withoutoptical proximity correction (OPC)while a resolution of 50nm and belowcan be achieved applying OPC models.Furthermore, advanced UV lithographyis available for printable features of20nm and below.Dielectric Waveguides. Traditionally,low-pressure chemical vapor deposition(LPCVD) nitride on top of micrometerthick thermal oxide was used inphotonics circuits owing to extremelylow losses in the visible and infraredspectrum [1]. However, co-integrationwith CMOS or bipolar circuitryis prohibitive due to the excessivethermal budget and consumption ofsilicon during oxidation. Therefore,combinations of low-temperature and20<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

Figure 2: Features defined by immersion lithography without optical proximity correction. a) (Left) 95nmgap between waveguide and micro-ring resonator before softmask removal; b) (Right) 95nm silicon nitridewaveguide on buried silicon waveguide.low-loss deposited nitride and oxidehave become an attractive alternativethat allow logic-first co-integration.We have developed plasma-enhancedSi 3 N 4 waveguides fabricated onmicrometer thick plasma-enhancedtetraethyl orthosilicate SiO 2 (pTEOS)cladding with processing temperaturesrestricted to 500°C and below. Thisallowed the monolithic integration ofoptical components in both the frontend(Cu not yet on the wafer) andback-end (Cu metallization present).For front-end co-integration, LPCVDnitride on top of pTEOS can also beused to further reduce the propagationloss. Final line-edge roughness (LER)mitigation included thermal oxidationand wet chemical oxide removal.Residual hydrogen incorporated duringthe plasma deposition resulted inweak absorption peaking at 2db/cmnear 1520nm. Annealing in an inertatmosphere for extended durations[2] permitted the reduction to 0.4db/cm. Comparable low absorption valueswere observed in the range betweenthe infrared and visible wavelengths.Single and multiple levels of dielectricwaveguides were produced usingrepeated planarization and patterning.Silicon Waveguides. Single andmulti-mode rectangular and ridgetypesilicon waveguides (WG) werefabricated on standard and thick-oxideSOI substrates using CMOS-compatiblelithography and non-scalloping reactiveionetching techniques. Dependingon the desired WG and claddingthicknesses, soft masks (resist) or hardmasks (dielectric material) were used toprotect the top silicon during etching.The use of SOI substrates facilitatesoptical confinement and improvedprocess repeatability and control (endpointtracing and thickness controlusing ellipsometry). Calibrated angledhigh-resolution inline scanning electronmicroscope (SEM) and scatterometrywere employed to determine and controlthe sidewall roughness and angle.Typically, substrates with 2µm buriedoxide (BOX) and 220nmtop silicon thicknesswere utilized, and ridgesas well as terminatingedges were definedusing standard silicondry etching chemistriesin high-density plasmaetchers. The residualline-edge roughness wasreduced using a thinmedium-temperature dryor wet oxidation step [3]followed by a removal ofthe resulting oxide in abrief immersion in diluteHF (Figure 3).Resonators, Filters, CouplersOptical components such asresonators, modulators, filters, splitters,and couplers complete the functionaldesign of an integrated photonicsapplication. Important parameters arequality factor, resonance frequency,insertion and coupling loss, bandwidth,Figure 3: Silicon waveguide and photonicsstructures after line-edge roughnessmitigation treatment.and tuning range. While most of thedesign parameters are determinedby geometry, i.e., lithography andpattern transfer, secondary effectssuch as sidewall roughness, patternproximity, and reactive ion etch (RIE)lag complicate design targeting.As an example, evanescent wavecouplers require tight control of thegap dimensions and geometry in orderto function at the desired wavelength.This imposes new constraints on OPCmodels for photonics components thatare computationally intense comparedto their standard CMOS counterparts.Figures 4 and 5 depict a selection ofFigure 4: Photonic elements fabricated in silicon on SiO2 and siliconnitride on SiO2: a) Microring filter structure; b) Microdisk resonatorin 95nm proximity of waveguide; c) Splitter; d) Splitter + microdiskresonator + phased-array emitter; and (e) Grating structure forsurface coupling.photonic components fabricated insilicon and silicon nitride core materials.Because of the high resonator qualityfactors and low propagation loss, verynarrow peak widths were obtainedin resonators and filters as displayedin Figure 6. As can be seen, smallvariations in geometry (gaps, grating<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]21

Figure 5: Silicon nitride waveguides with linear distributed feedbackline structures: a) Deep gratings; b) Shallow gratings; c) Externalproximity gratings. The features were rounded due to the absenceof optical proximity correction.periods, etc.) resulted in substantialshifts of resonance frequencies and asa result, additional resonance tuningbeyond lithography defined set-pointsare needed to dynamically matchvarious photonic on-chip components.Electro-optical effects, and morerecently, thermal modulation, providethe necessary tuning capability on themicroscopic scale.In order to couple the light from thefiber to the chip, grating structures andfiber trenches were developed. For thepurpose of lateral fiber end-coupling,trenches (as deep as approximately halfthe fiber diameter) were fabricated usingcyclic deep reactive ion etching (DRIE)prior to chip dicing. Sidewall tapering,control of final depth, and slopedbottom topography make this approachchallenging for final fiber alignment.In contrast, in-plane grating structureswere readily fabricated in silicon andsilicon nitride by shallow non-cyclicreactive ion etching in a single orarray-type coupling arrangement. Incombination with integrated modulators,Figure 6: Resonant wavelengths of photonic elements: a) (Left) DBRresonance as a function of grating period (in nm); b) (Right)Microdisk (R=100µm) resonance as a function of gap (in nm) towaveguide. Data fitting indicated Q ≈ 500,000 and a≈ 0.6db/cm.tunable phased-arrayemitters were fabricatedthat allowed beam steeringfrom a 64x64 emitter arrayembedded directly on amicrochip [4].Modulators andDetectorsIntegrated photoniccircuits rely on theemission, modulation,and detection of light inthe communications band(1.3µm to 1.55µm). Dueto the larger bandgapcompared to the energyof light, silicon is a poor detectormaterial for 1.55µm. In contrast, thebandgap absorption edge in germaniumis near 1.58µm, and even thoughGe is an indirect semiconductor, itprovides sufficient photo-response foroptoelectronic applications using 1.3and 1.55µm carrier wavelengths. In thisreport, we present results from p-i-n Gediode detectors. The Ge detectors wereembedded in low-temperature depositedoxide (between 0.5 and 1.0µm thick) byblanket deposition, patterning with RIE,and Ge CVD growth and planarization.Bottom contacts were achieved byp-type ion implantation while topcontacts were in situ n-type dopedpoly-crystalline silicon. The growth ofGe was performed using either a lowthroughputtwo-step process similar tothat reported by Luan [5] or by a fasthigh-temperature one-step technique[6]. Both methods required postgrowthannealing cycles to reduce theamount of threading dislocations andlower the reverse leakage current intothe nA/µm 2 range [7]. Following aplanarization step, theGe was immediatelycapped, patterned, andcontacted using a lowtemperaturein situ n-typedoped polysilicon film.After a spike activationanneal, the top electrodewas defined and backendmetallization layerswere processed. Across-sectional transmission electronmicroscope (TEM) picture is shown inFigure 7 for a sample with insufficientdefect annihilation anneal. While mostdislocations are confined to the first fewhundred Angstroms, a small number ofdislocations still propagated to the topcontact. Detectors of this type producedFigure 7: Cross-sectional TEM of Ge detector andtop contact (in situ n-type dopedpolycrystalline silicon).reverse leakage currents of 0.5 to 2µA/µm 2 at -1V, while un-annealed Geresulted in >10µA/µm 2 . In contrast,

Figure 8: a) (Left) Dark and illuminated IV curve of integrated 1µm-by-9µm Ge detector; b) (Right) Spectral photo-response at various valuesof reverse bias.by the Defense Advanced ResearchProjects Agency (DARPA) of the UnitedStates under the E-PHI and SWEEPERprojects, grant no. HR0011-12-2-0007.Contact AuthorDouglas Coolbaugh received hisPhD from SUNY Binghamton, NYin Physical Chemistry in 1987. He isan Assistant Vice President of CMOSderivatives at the College of NanoscaleScience and Engineering (CNSE); emaildcoolbaugh@albany.eduWada, L. C. Kimerling,“High-quality GeEpilayers on Si with LowThreading-dislocationDensities,“ AppliedPhysics Letters, Vol. 75,<strong>Issue</strong> 19, 8 Nov. 1999, pp.2909 – 2911.6. A. Sammak, L. Qi, W.B. de Boer, L. K. Nanver,“PureGaB p+n Ge DiodesGrown in Large Windows to Siwith a Sub-300nm TransitionRegion,“ Solid-State Electronics,Vol. 74, 2012, pp. 126 – 133.7. Y. H. Tan, C. S. Tan, “Growthand Characterization ofGermanium Epitaxial Film onSilicon (001) Using ReducedPressure Chemical VaporDeposition,“ Thin Solid Films,Vol. 520, 2012, pp. 2711 – 2716.Faster,Easier,SmarterJettingReferences1. A. Gondarenko, J. S. Levy, M.Lipson, “High ConfinementMicron-scale Silicon NitrideHigh-Q Ring Resonator,” OpticsExpress, Vol. 17, <strong>Issue</strong> 14, 6 July2009, pp. 11366 – 11370.2. K. Wörhoff, P. V. Lambeck, A.Driessen, “Design, ToleranceAnalysis, and Fabricationof Silicon Oxynitride BasedPlanar Optical Waveguides forCommunication Devices,“ Jour.of Lightwave Tech., Vol. 17, <strong>Issue</strong>8, Aug. 1999, pp. 1401 – 1407.3. D. K. Sparacin, S. J. Spector, L. C.Kimerling, “Silicon WaveguideSidewall Smoothing by WetChemical Oxidation,“ Jour. ofLightwave Tech., Vol. 23, <strong>Issue</strong> 8,Aug. 2005, pp. 2455 - 2461.4. J. Sun, E. Timurdogan, A.Yaacobi, E. S. Hosseini,M. R. Watts, “Large-scaleNanophotonic Phased Array,“Nature, Vol. 493, 10 Jan. 2013, pp.195 – 199.5. H.-C. Luan, D. R. Lim, K. K. Lee,K. M. Chen, J. G. Sandland, K.* patents pendingYou can rely on our award-winning support network.Visit our website to contact your local office:USA | China | Europe | Japan | Korea | India | Singapore | TaiwanFind out more now: advancedjetting.comThe NexJet ® System*featuring the one-pieceGenius Jet Cartridge*The Genius Jet Cartridge is the onlysystem part that contains fluid — theonly piece that needs tobe changed and cleaned.It is easily removed inseconds without tools.Built-in memory tracksand stores usage data,thereby increasing qualityand consistency in precisionmanufacturing applicationssuch as adhesive dispensing, precisecoating and underfill.<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]23

Cleaning High-Reliability Assemblies withTight GapsBy Thomas M. Forsythe [Kyzen Corporation]State of the art electronicdevices continue toadvance at a rapid ratedelivering new capabilities to consumersthroughout the world. Mobile phonesalone account for over 400 million unitsper quarter, a solid 35% of which aresmart phones. Smart phone productionvolumes now eclipse PC shipments,even with the generous inclusion oftablet sales in the PC statistics.As even the casual observer is aware,these smart phones are smart indeed andtheir capabilities are steadily improving.This enhanced performance is a keyelement driving demand for thesedevices, not surprisingly as performanceimproves so does the user’s expectationsof quality and reliability; if one has their“life on one’s phone,” we certainly arenot happy to see it go up in smoke inany way.Electrochemical migration (ECM) isa critical risk factor in any electronicreliability analysis. Since everyelectronic device is powered up tofunction, and virtually every devicedoes so in the presence of humidity, thesure way to prevent ECM is the absenceof ionic residues.Reducing or eliminating residuesstarts with a well-designed, validated,well run cleaning process. Sucha process has two major buildingblocks: the equipment delivering themechanical energy, and the cleaningagent delivering a well matchedchemical solution that together removeall undesired contaminants not onlyfrom readily accessible surface areasbut difficult to reach gaps beneathcomponents and other devices.The balance between chemical andmechanical elements in the process iscritical to robust process design, equallyimportant to a detailed understanding ofthe assemblies or packages which are tobe cleaned.Those schooled in the art of cleaningknow that board density can increase thecleaning challenge, but the critical driverin today’s complex designs is the “gap.”The gap, also known as the stand-offheight, is the distance between the bottomof a device and the board surface; theshorter this distance, the more difficultthe cleaning challenge. Not surprisingly,truly flush mounted components presentthe greatest challenge.With a sound understanding of thechallenges presented by the assemblydesign, next we turn to the cleaningprocess itself. This evaluation beginswith certain fundamentals developedduring decades of research into cleaningtechnology that can act as a guideduring the process:Increased temperature generallyenhances process results. However,the results provided by slightly elevatedtemperature are often not bettered at veryhigh temperatures. More is not alwaysbetter, and our data set will guide us todefining the point of diminishing returns.Higher concentrations of thecleaning agents often enhanceperformance. As with temperature,there is routinely an inflection pointof diminishing returns that shouldbe understood in any process design.Operating concentrations have a lineareffect on operating costs and alwaysreceive close scrutiny.The mechanical energy deliverysystem is important. It comprises thefollowing: pressure, spray patterns,exposure gaps.Exposure time to the cleaning agentand mechanical energy is anotherkey factor. Time is always a preciouscommodity, and frequently subject toarbitrary limits determined prior to thedevice evaluation. When consideringtight gaps or low standoff height devicecleaning, a fifth element comes intoplay: cleaning agent surface tensionand propensity for capillary action. Inconjunction with the driving force ofmechanical impingement, lower surfacetension improves capillary action.Together, these forces enhance wettingand penetration of the fluid into tightgaps beneath components.Experimental DesignThe purpose of this designedexperiment is to evaluate theeffectiveness of a variety of cleaningagents under an array of processconditions. As such, mechanicalenergy was limited to allow for fullunderstanding of the chemical drivingforces at work as evaluated by ionchromatography. This DOE focused oncleaning effectiveness of a selected lowgap chip-scale package.Two commonly used water solublefluxes typical for this type of packagewere selected along with threedifferent cleaning solutions plus thecommonly used water alone baseline.Three temperatures of 20°C, 40°C and60°C were evaluated all with minimalagitated soak via mild shaking agitation.Response variables included visioninspection at 100x, and both anion and24<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

cation evaluation via ion chromatography (IC).Dozens of studies have been conducted over the past 10years, evaluating various aspects of new and novel cleaningprocesses providing a range of perspectives. Generally, theyshared a modest number of substrates and resulting datapoints. This study attempted to address that with a largedata set, 82 different points each with IC results to compareand contrast an unusually large body of IC data that we willattempt to analyze thoroughly.Data AnalysisWe begin the data review with our control sample. Whatis the state of the substrates prior to any cleaning step at all?Figure 1 provides the anions detail. We have chlorides,nitrates and weak organic acid (WOA) present. WS#2 hasgenerally lower levels of WOA than WS#1. Cation datawas similar with generally very low levels with an elevatedsodium level.One challenge with this DOE is that it is a point sourceanalysis. We did not evaluate full assemblies because surfacecleaning is generally not very challenging these days. It canbe, but cleaning in these tight gaps is the critical successcriteria. For this reason, the results are a bit different fromother recent studies.The challenge comes with interpreting the data—currentindustry standards are logically focused on the acceptabilityof a full assembly not a single challenging device. The properapproach for scaling down these full assembly acceptablestandards is also work that will be addressed in the future.SemiconductorAssemblymAteriAlSWS-641 Cu-PillarFlip-<strong>Chip</strong> FluxKey points:• Proven success in mobileplatforms in Asia• Industry-leading cleanabilityApplications:• Water-soluble dipping flux• Copper pillar/microbumps• Thermocompression bondingLearn more:http://indium.us/E031Figure 1: Control anions.Cations detail is in Figure 2. We have sodium, lithium,potassium present. WS#2 also generally has lower levelsof cations than WS#1. Water alone was included in theevaluation for one reason: it is the most common cleaningagent used to clean water soluble fluxes throughout the world.The key question is how does it measure up versus the controland the various cleaning agents evaluated. Evaluating thewww.indium.comaskus@indium.comASIA • CHINA • EUROPE • USA©2013 Indium Corporation<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]25

Figure 2: Water only anion results.Figure 4: Agent A anions at 60°C.Figure 3: Agent A anions at 20°C.water only anion results we see that chlorides, bromides,nitrates and weak organic acids are all present, while WS#2has lower levels of WOA. The results also strongly parallelthose found on the controls for both the anion and cations.Now, let’s look at the results for the various cleaning agents.Inferences that can be drawn from the Agent A data(Figure 3) include less visual difference between the twofluxes than when exposed to water alone, and cleaning wasmarginally improved with higher concentration.Looking specifically at anions, the levels were very lowoverall. At the lowest temperature point of 20°C, we do seethe data spread for WOA as with water and the control. Astemperature increases, all the results trend together with WOAreduced to 0ppm as the temperature is increased to 40°C and60°C (Figure 4) while nitrates and phosphates rose slightlyat 40°C and 60°C. Cation data presented a similar positiveresponse to temperature.Interaction and Main Effects PlotsAgents B and C showed slightly better performance, butFigure 5: Interaction plot for weak organic acid (WOA).Figure 6: Interaction plot for sodium.rather than review those data points individually, we will doso through the use of selected interaction and main effectsplots to allow easy comparison (Figure 5).Water responds meaningfully to increased temperature26<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

Figure 7: Interaction plot for potassium.Figure 8: Interaction plot for calcium.Figure 9: Main effects for grand total.from 20°C to 40°Cas one would expect.While WS#2 appearsto have lower levelsof WOA, the data isskewed by the controland water only resultsthat are meaningfullypoorer than all theagent data. Thisis a meaningfulobservation.While WS#2 wasconsistently betterthan WS#1, it wasa slight difference.The major change inthe plot was againdriven by the controland water points.Sodium also trendsbetter with increasedtemperature (Figure6). Concentrationseems to help,while temperaturedoes not appearvery responsive forthe potassium ions(Figure 7). Agent Conce a gain a clearwinner with littledifference betweenWS#1 & WS#2 (Figure 8). With thecontrol data skewed, Agent C breaks outas the winner though temperature andconcentration do not trend toward moreis better (Figure 9).SummaryThe large data package in this DOEmakes the analysis rather straightforward. As in most protocols, thereare ambiguous results at times andnot every data set reaches the sameconclusion. This point is key: anyparticular product life cycle may haveunique sensitivities important to itsoperating for every day of its servicelife. Detailed data such as this, thoughexpensive and time consuming togenerate, can be enormously instructivefor such high-value, long-lived devices.Work such as this has severalpotential paths forward. One is toinclude more soils into the currentdata matrix. Another is to keep thesame dataset and move downstreaminto commercial grade cleaningequipment to evaluate the impact ofmeaningful mechanical energy. Moreimportantly for the industry, as worksuch as this propagates, industrystandards will need to be developedand validated for these point sourcecontamination levels.AcknowledgmentsThis paper was presented at theSMTA Pan Pacific 2013 Conference.A great deal of thanks goes to theleadership at Kyzen for allocating thesubstantial resources to complete thisproject: in-house IC equipment andmore importantly, a talented team ledby Dr. Mike Bixenman and DavidLober that includes John Garvin andJames Perigen.BiographyThomas M. Forsythe received his BSfrom the United States Naval Academy,Annapolis MD in Operations Researchand Engineering and his MBA fromBoston U. in Finance; he is the VP ofSales & Mktg at Kyzen Corp; emailtom_forsythe@kyzen.com.<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> May/June 2013 [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]27