Technology of Q 2500 colour TV set

Technology of Q 2500 colour TV set

Technology of Q 2500 colour TV set

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

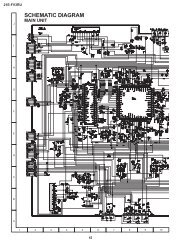

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Via the sampling circuit, the digital Y signal,which is now 9-bits wide, reaches a DAC,which generates an analogue signal. This isthen output on pin 44 at 1.5 Vss.4.6.5 Microprocessor interfaceAll processes in the SAA 4979 are controlledby SDA6000 via the I²C bus 0 (pin 1 = SDA,pin 2 = SCL). In addition, information for theSAA 4993 and the memory control is alsotransferred.The SAA 4993 is controlled by the BESIC viathe microprocessor bus to pins 108 (µP DA)and 107 (µP CL).Switching outputs 4 are used for the switching<strong>of</strong> the VGA synchronisation. If a switch ismade to the VGA programme location, thenpin 4 is switched from I 2311 to L level. Withthis logic state the vertical synchronous pulse<strong>of</strong> the VGA interface W 1011 pin 4 is switcheddirectly to the video/deflector controller I 2521via the four Nand gates I 2361 A/B/C and D.The VGA synchronous pulse is, in addition,monitored by I 2271 on its pin 17. If no synchronisationor false synchronisation is detected,I 2311 re<strong>set</strong>s its output on pin 4 andthereby switches over to internal V synchronisation.4.6.6 Control <strong>of</strong> the 100 Hz processing(Display)This stage synchronises the read out from thehalf pictures and the writing to memory in thesecond memory. As the signals in the SAA4993 are written to and read out, it has directcontrol and is only synchronised by theBESIC.Furthermore, the display stage gives a horizontalpulse on pin 54 and a vertical synchronouspulse on pin 55 for the synchronisation<strong>of</strong> the deflection in TDA9332. At the sametime, the vertical pulse VD acts as a re<strong>set</strong> forthe Falconic and the half picture memories, forre<strong>set</strong>ting the address counter on reading fromthe memory and for writing to the secondmemory.4.7 Video/deflection processor TDA9332/Range Video/RGB pathThe last IC for picture signal processing, apartfrom the RGB output stages, is the TDA 9332.It also controls the deflection stage.Inputs for analogue R-Y, B-Y and Y signals:- Two RGB inputs for analogue signals fromthe CCU and the VGA interface and/or picturein picture generation- Matrix circuits for RGB generation from thedifference signals- Signal selection for the switching <strong>of</strong> therequired RGB signals- Y and <strong>colour</strong> difference matrix for the generation<strong>of</strong> Y and difference signals from theselected RGB signal- Hue control for NTSC operation andgamma correction in the Y branch- Saturation, contrast and brightness <strong>set</strong>tingVia pulse RE (pin 84) the Falconic modulecontrols the reading from both half picturememories and the writing to the second memory.With pulse IE (pin 83) SAA 4979 controls thedata inputs in the second half picture memory.With L level a switch can be made to freezeframe, for example.Document Q <strong>2500</strong> 102 © Loewe ProCollege