Technology of Q 2500 colour TV set

Technology of Q 2500 colour TV set

Technology of Q 2500 colour TV set

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>231-90415.917Loewe Opta GmbHPostfach 155496305 KronachIndustriestraße 1196317 KronachTel: (09261) 99-0Fax (09261) 9 54 11e-mail: loewe@loewe.dehttp://www.loewe.deDokument Q <strong>2500</strong> 1 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Document Q <strong>2500</strong> 2 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>1 Introduction..............................................51.1 Foundations <strong>of</strong> 100 hz technology ................ 71.1.1 Prerequisites for 100 Hz........................ 71.1.2 100 Hz display modes ........................... 71.1.3 Mode AABB ......................................... 71.1.4 Mode ABAB ......................................... 91.1.5 Mode AA’B’B....................................... 91.1.6 Mode AA*BB* ..................................... 92 Basic board............................................122.1 Standby power supply ................................. 122.1.1 Standby power supply circuit .............. 122.2 Blocking oscillator type power supply........ 132.2.1 Primary side......................................... 142.2.2 Start-up................................................ 162.2.3 Normal and control operation.............. 162.2.4 Protective operation............................. 172.2.5 Power Factor Control .......................... 172.2.6 Secondary side..................................... 182.2.7 Voltage stabilisation............................ 202.2.8 Voltage increase .................................. 202.2.9 Servicing information.......................... 212.3 Horizontal deflection and high voltageproduction ............................................................... 212.3.1 Horizontal driver ................................. 212.4 Horizontal output stage ............................... 222.4.1 High voltage production...................... 252.4.2 Horizontal- <strong>of</strong>f<strong>set</strong> deflector ................. 252.5 East/west correction .................................... 262.5.1 Circuit.................................................. 272.6 Vertical output stage.................................... 282.6.1 Flyback generator................................ 292.6.2 Vertical protective circuits .................. 302.7 Beam current limitation............................... 322.7.1 Overbeam current fuse ........................ 332.7.2 HFLB protective circuit....................... 342.8 Speed modulator.......................................... 342.8.1 General ................................................ 342.8.2 Switching <strong>of</strong> the speed modulator ....... 362.9 Colour stages............................................... 372.9.1 Cut <strong>of</strong>f control ..................................... 382.9.2 Switch <strong>of</strong>f flash suppression................ 402.10 Rotation panel ............................................. 402.10.1 Raster correction ................................. 402.10.2 Circuit.................................................. 412.11 NF output stages.......................................... 423 Receiver components ............................443.1 HF/IF unit.................................................... 443.1.1 HF/IF components............................... 443.2 DVB Board.................................................. 463.2.1 Overview ............................................. 463.3 Features and parameters .............................. 483.3.1 DVB internal features.......................... 483.3.2 DVB/<strong>TV</strong>-Features ............................... 523.3.3 Architecture......................................... 523.4 Components................................................. 543.4.1 Satellite front end ................................ 543.4.2 Functional distribution ........................ 543.4.3 Tuner ................................................... 543.4.4 DVB demodulation and fault correction563.4.5 LNC supply..........................................594 Signal board .......................................... 604.1 Device control..............................................604.1.1 The infrared sensor...............................624.1.2 Infrared receiver...................................654.1.3 The SDA 6000 central control unit ......664.1.4 Re<strong>set</strong>.....................................................674.1.5 Creation <strong>of</strong> cycle frequency .................684.1.6 Operational commands.........................684.1.7 LED display .........................................684.1.8 ON/OFF function .................................684.1.9 Protective circuit ..................................684.1.10 AV operation........................................694.1.11 SAT standby.........................................704.1.12 SAT unit control...................................714.2 Bus systems in Q <strong>2500</strong> chassis.....................724.2.1 I²C bus systems ....................................734.2.2 IC 24C64 memory................................754.2.3 EPROM M 27 C 322............................754.2.4 SRAM ..................................................764.2.5 Search functions...................................764.2.6 Storage .................................................764.2.7 Programme recall .................................764.2.8 System clock ........................................774.2.9 Control <strong>of</strong> signal processing.................774.2.10 Service mode........................................784.2.11 Video text.............................................784.2.12 Picture signal processing......................784.2.13 Components for....................................794.2.14 Signal path ...........................................804.2.15 IC functions..........................................844.3 VPC 3230.....................................................844.3.1 Input interface ......................................854.3.2 20.25 MHz clock generator..................864.3.3 Comb filter ...........................................874.3.4 Multi-standard <strong>colour</strong> decoder .............894.3.5 Line compression and .........................894.3.6 Output format conversion ....................904.3.7 Synchronisation block..........................904.3.8 I²C bus interface...................................904.4 Half picture memory SAA4955HL..............904.4.1 Storage space........................................914.4.2 Conversion <strong>of</strong> signals in.......................924.4.3 Half picture memory 2 and 3 ...............924.4.4 Control pulses ......................................924.5 Falconic module SAA 4993.........................964.5.1 Noise reduction ....................................964.5.2 Line interpolation.................................984.5.3 Movement detector ..............................994.5.4 Memory control....................................994.6 SAA 4979 (BESIC)......................................994.6.1 Chroma branch...................................1004.6.2 Band width doubling..........................1014.6.3 Colour flank sharpening....................1014.6.4 Y signal path ......................................1014.6.5 Microprocessor interface....................1024.6.6 Control <strong>of</strong> the 100 Hz processing.......102Document Q <strong>2500</strong> 3 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>4.7 Video/deflection processor TDA 9332/RangeVideo/RGB path.................................................... 1024.7.1 Matrix circuits and signal.................. 1034.7.2 Control stages.................................... 1054.7.3 I²C bus interface and ......................... 1054.8 Picture in picture ....................................... 1054.9 Video/deflection controller TDA9332(deflection area) .................................................... 1084.9.1 Clock generation/Phase 2 loop .......... 1084.9.2 DAC for OW/V control..................... 1084.9.3 Beam current dependent correction... 1085 Audio signal processing.......................1105.1 Audio-Signal path Block diagram Q <strong>2500</strong>H/M and B............................................................. 1105.2 Demodulator/Decoder-Block .................... 1125.2.1 Audio baseband processing ............... 1135.2.2 Demodulator/decoder block .............. 1135.2.3 Nicam processing .............................. 1145.2.4 Audio signals from the interface ....... 1145.2.5 AM audio signals at L standard......... 1145.2.6 Audio base band processor................ 1155.2.7 Loudspeaker branch .......................... 1155.2.8 Loudness ........................................... 1155.2.9 Sound <strong>set</strong>ting..................................... 1155.2.10 Loudspeaker control and AVC.......... 1165.2.11 DAC .................................................. 1165.2.12 Headphone branch............................. 1165.2.13 Interface branch................................. 1165.2.14 Deadline volume ............................... 1165.2.15 Mute circuit ....................................... 1175.2.16 Headphone amplifier ......................... 1195.3 AC3 module (Dolby Digital)..................... 1215.3.1 Block diagram, AC3 module............. 1215.3.2 AC 3 signal processing...................... 1215.3.3 AC 3 IC functions ............................. 1236 Interface switching ...............................123Document Q <strong>2500</strong> 4 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>1 IntroductionThe Q <strong>2500</strong> chassis is a further development<strong>of</strong> the tried and tested 100 Hz Q 2400 chassis.The modular design, dimensions and layouthave been retained.In order to improve picture performance evenfurther, several circuit components have eitherbeen modified or newly added. For sound signals,IF processing in the main receiver unit isnow entirely digital.The Q <strong>2500</strong> chassis is available in three differentversions, Q <strong>2500</strong>/H (High End), Q<strong>2500</strong>/M (Medium) and Q <strong>2500</strong>/B (Basic). Thesignal board is different for all three versions.It has different equipment in certain areas owingto the different power spectrum <strong>of</strong> thethree versions. All H/M and B signal boardversions are electrically interchangeable. Dueto the incorporation <strong>of</strong> 2 or 3 AV sockets (theback <strong>of</strong> the <strong>TV</strong> <strong>set</strong> does not fit) they are notmechanically compatible. Except for the signalboard there is no differentiation with respect toall other components for the different versions– High End, Medium and Basic. The Q <strong>2500</strong>chassis therefore supersedes the Q 2400 andQ 4140 chassis completely.Because <strong>of</strong> this concept it is now possible t<strong>of</strong>it a DVB upgrade kit to all 100 Hz <strong>TV</strong> <strong>set</strong>s –from the Contur to the Aconda. So far this hasonly been possible for <strong>set</strong>s with the Q 2400chassis and not for <strong>set</strong>s with the Q 4140chassis.The following features have been retainedfrom the previous chassis:- 8 bit digital signal processing- ACP (Automatic Channel Programming) forfully automatic programming <strong>of</strong> stationsand sorting <strong>of</strong> cable and SAT reception, includingan update function.- child protection security-plus with secretcode.- - Sharpness control, photo CD circuitand comb filter (S-PAL).- SCS (Sharpness Control System) for apicture-dependent velocity modulation <strong>of</strong>the horizontal (line) sweep.- DTI Plus (Digital Transient Improvement)for <strong>colour</strong> edge sharpening.- 576-line still picture- Adjustable noise suppression DNC (DigitalNoise Control)- Suppression <strong>of</strong> interline flicker DLC (DigitalLineflicker Control).- Digital Line Interpolation (DLI) for full framepicture display for PALplus and also in allzoom modes.- Digital Motion Interpolation (DMI) ensurescontinuous movement over all single framepictures.- Automatic Movie Detection (AMD) forswitching to wide screen format in PALstandard on 16:9 units.- Automatic PALplus recognition and formatswitching for 16:9 units.- Digital Scene Control (DSC) for improvedgrey scales.- Various switching modes (4:3, Cinema,Zoom, 16:9 and Panorama Mode for 16:9units).- Automatic Volume Control (AVC) for adjustingthe volume between different channelsand during commercial breaks- On the front: Headphone output and inputwith S terminals and three cinch sockets.Document Q <strong>2500</strong> 5 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>- Copy function for re-recording betweendifferent inputs and outputs (also instandby mode), and during <strong>TV</strong> programmes.- Internal clock synchronized with Teletext.- EPG function (electronic programmeguide).- Recording timer for video recorder andSAT standby function.- Operation <strong>of</strong> Loewe video recorders via themenu.- Switch-<strong>of</strong>f automation and timer.- In 81 cm <strong>set</strong>s a rotary panel is used in orderto compensate for the earth’s magneticfield. This prevents distortion <strong>of</strong> the pictureno matter where the <strong>set</strong> is placed.- Personal Control System (PCS): operationtailored to individual customer requirements.The most frequently used functionsmay be assigned to four buttons <strong>of</strong> the remotecontrol. Additionally, the operatingmanual may be viewed on the screen – OnScreen Display (OSD). This includes helpinstructions on functions currently used, informationon the remote control functionsand an index, which enables immediateimplementation <strong>of</strong> functions. It is also possibleto <strong>set</strong> limitations to the scope <strong>of</strong> operationaccording to customer requirements.The user may, for example, be preventedfrom making changes to particular<strong>set</strong>tings.- A Dolby Digital Module can be installed inmodel versions H and M.- The EAROM and the DVB s<strong>of</strong>tware maybe directly written to via an external V 24service interface using a PC and serviceadapter.The following features are completely new:- Depending on version, either two or threeAV sockets.- Depending on version, a Teletext memorywith 3000 pages (with active EPG function2000 pages).- An own radio menu, accessible over the“speaker symbol“ on the remote control.- Improved Digital Movie Mode (DMM). Featurefilms are recognized safely. Therefore,accidental switching to camera mode isprevented. Switching effects do not occuranymore.The following circuit descriptions have beensubdivided according to the individual modules.Deviation from this scheme occurs occasionallyin order to emphasize relations betweencircuits more effectively. All componentpositions in the circuit diagrams are identifiedby four figures. For the signal board the fullyequipped version H is explained. For versionsM and B only the differences are noted.The upgrade kits are explained in a separatecircuit description.- Automatic Gain Control (AGC) for all videosignals shown in the main picture.- The RGB signals are no longer convertedto analogue Y/C signals but are directlydigitised instead.- An Audio-In socket to which, for example,an external digital radio receiver may beconnected.- Some models, e.g. Aconda, may be upgradedDocument Q <strong>2500</strong> 6 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>1.1.2 100 Hz display modes1.1 Foundations <strong>of</strong> 100 Hz technology1.1.1 Prerequisites for 100 HzIn order to double the picture frequency at thereceiver, the signals have to be read into therelevant memory blocks and then read outtwice at double rate.The following prerequisites must be met:- The signals need to be digitised.- The memory modules require at least 3Mbits storage capacity.- The s<strong>of</strong>tware must be able to run a controller,which in turn monitors the read-in andread-out functioning <strong>of</strong> the memory.- Suitable frequency-stabilized oscillators forgenerating the clock frequency must beprovided.- The drive signals for the output stages, lineand field deflection, and the E/W correctionmust also be at double frequency.- The power output stages for deflection, aswell as the deflector itself, need to be designedfor the higher frequency and the resultinghigher currents.- The RGB output stages need to be able toprocess the doubled bandwidth.When examining display modes the deflectionraster and the video raster need to be consideredtogether. In 50 hz operation, the two single-framepictures A and B are written to thescanning system ‘a’ and ‘b’, i.e. every secondline <strong>of</strong> frame A and the intermediate lines <strong>of</strong> B.This is achieved in that the flyback <strong>of</strong> ‘a’ beginsin the middle <strong>of</strong> a line. Trace ‘b’ startsalso in the middle <strong>of</strong> a line but is written to theend <strong>of</strong> a complete line. The next trace ‘a’starts again at the beginning <strong>of</strong> a line. Thetrace time, however, is always the same.1.1.3 Mode AABBThe simplest case <strong>of</strong> 100 hz operation involvesa simple doubling <strong>of</strong> single-frame picturedisplay, i.e. field A is displayed twice consecutivelyfollowed by field B (AABB).To achieve this the deflection raster must bemodified so that ‚a’ is written twice followed by‘b’ (aabb). Theoretically, this can be accomplishedin two ways. Firstly, by adjusting theflyback’s starting time for the 4 single frames.A half-line more is written for ‘a1’ and a halflineless in for the third field. In practice, sucha scheme would be quite difficult to implement.In comparison, the second possibility iseasier to achieve. This involves shifting the 2 ndand 3 rd fields (a2 and b1). This can be accomplishedby adjusting the current though thedeflector by modifying the base resistance.This produces the same time interval for alltraces over all fieldsDocument Q <strong>2500</strong> 7 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Deflection 100Hz319/73a 100HzScanning pattern a-a-b-bScanning pattern a320/8321/93.Halfpicture...1. 50Hz620/308732083219......620308Scanning pattern a319Scanning pattern b7320/8321/9...2.Half picture(300,5 Lines)1.Half picture(301 Lines)Scanning pattern b3191.Halfpicture620/3083.Half picture(300 Lines)4.Half picture(300,5 Lines)2.100HzScanning pattern a-b-a-b732083219......620308Scanning pattern a1. Half picture319Scanning pattern b2. Half picture7320/8321/9...620/3083b 100HzScanning pattern a-a-b-bScanning pattern a319Displacementby one line<strong>of</strong> 2nd half picture732083219......620308Scanning pattern a3. Half picture319Scanning pattern b4. Half picture320/7321/8.../91.Half picture(301 Lines) 2.Half picture(301 Lines)Scanning pattern b319Displacementby one line<strong>of</strong> 3rd half picture620/...3083.Half picture(301 Lines)4.Half picture(301 Lines)Document Q <strong>2500</strong> 8 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>For AA and BB display, delay lines must ensurethat the lines <strong>of</strong> the 1st and 2nd, and 3rdand 4th fields contain the same picture informationwhen superimposed on one another.This mode <strong>of</strong> display allows for very effectivereduction <strong>of</strong> large-area flicker. A reduction <strong>of</strong>interline flicker is, however, not possible, becauseintermediate lines are only traced after20ms.Memory 1Memory 1retardedMemory 2Output10 10 1010 10 910 8 810 10 9x x xx x xx x xx x x1.1.4 Mode ABABThis mode, together with the two describedbelow, are only possible in conjunction with asecond single-frame picture memory because<strong>of</strong> the alternating display <strong>of</strong> A and B. The deflectionmust also operate in ‘abab’ rasterform. In this display mode, the signals are notmodified during deflection or image processingoperations. In this case, both interlineflicker and large area-flicker can be reduced.However, jerking effects in moving imagescan arise. This form <strong>of</strong> display is only suitablefor signals where an image is formed from tw<strong>of</strong>ields between which there is no relativemovement. This mode is therefore <strong>of</strong> interestonly for “Photo CD” or cinema scope films inPALplus.signal delayed by one single-frame are comparedwith one another. If deviations are de-Interpolation exampletected in one <strong>of</strong> the signals, this signal is eliminatedand the values that agree in the othertwo signals are retained. If all three signalsvary, an average is formed.The deflection proceeds as sweep ‘abab’. Thecalculated A’ and B’ are written to shiftedscanning system <strong>of</strong> the 2 nd and 3 rd singleframes. A and B are written to the non-shiftedsystem <strong>of</strong> frames 1 and 4.This mode is suitable for the display <strong>of</strong> horizontalmotion between frames. Only smalljerking effects arise between movements.The mode is used to suppress interline flickerin normal <strong>TV</strong> operation.1.1.6 Mode AA*BB*Reduction <strong>of</strong> interline flicker withoutmovement interpolation (DLC)Memory 1Memory 1 Memory 2retarded1.1.5 Mode AA’B’BOutputDeflectionScanningpatternA A v B A aA A v A A' bB B v A B' aB B v B B bA A v B A aIn this display mode two single-frame pictures,A’ and B’, are calculated. By using an interpolationfilter the current single-frame, the currentsingle-frame delayed by one line and theIn this display mode with respect to the calculatedframes A* and B*, the movement betweenthe original frames A and B, and betweenB and the next A are taken into account.This movement interpolation (DMI –Digital Motion Interpolation) takes into accountboth horizontal and vertical movements whichcover several lines. This means that whensuppressing interline flicker, continuousmovement over all frames is achieved.For full frame pictures (films) it is also assuredthat no movement between two single-framepictures takes place (DMM – Digital MovieMode).In this display mode the deflection is also‘abab’.Document Q <strong>2500</strong> 9 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Movement interpolationPcture 1Picture 2 Picture 3Picture 1 Picture 1*Picture 2 Picture 2*Picture 3 Picture 3*Display mode 100HzNo.PicturechangefrequencyVideoscanningpatternDeflectionscanningpatternModeAdvantages1.50HzA-Ba-b2.100HzA-A-B-Ba-a-b-bDLC <strong>of</strong>f-Reduction <strong>of</strong> large area shimmer3.100HzA-B-A-Ba-b-a-b-Photo CD on-PAL plus Cinema Scope-Reduction <strong>of</strong> large area shimmer-Reduction <strong>of</strong> interline shimmerin full picture <strong>set</strong>up4.100HzA-A´-B´-BababDLC on-Reduction <strong>of</strong> large area shimmer-Reduction <strong>of</strong> interline shimmer in fullpicture <strong>set</strong>up with movement5.100HzA-A*-B*-BababDMI-Reduction <strong>of</strong> large area shimmer-Reduction <strong>of</strong> interline shimmer in fullpicture <strong>set</strong>up with movement-Movement interpolationDocument Q <strong>2500</strong> 10 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>SATunitTwinSA<strong>TV</strong>ideoNF - LNF - RVideoAudioZFEuro-, Hosiden-, CinchandHeadphones socketsInterfacecontrolDVBDVB<strong>TV</strong>OPSUSet control unit<strong>TV</strong>OFB230V~Operating unit,standby PSUIR recieverVGA -InterfaceU5 SB†berhub.ON/OFFRSIGSignal-BoardSignal processingDolby DigidalPIPBooster coilFBAS / PIPFBASAudio-ZFNF-Mono100 HzRGBCut <strong>of</strong>fSpeed modulatorRGB output stagesc.r.t. plateRGBRotation panelnot additional to <strong>TV</strong>OVertical output stageVertikal deflection coilBasic-BoardO/W output stageHorizontal output stageDiode split transformerNF output stagesHorizontal deflection coiUG2FocusHigh voltageAuxiliary voltagesNF - LNF - RPower supplyOperatingvoltagesHF- ZF / PIPHF- ZFFBAS / PIPFBASAudio-ZFNF-MonoDocument Q <strong>2500</strong> 11 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>2 Basic boardThis main heading covers the analoguestages from the power supply circuit throughthe power output stages to beam current limitation,irrespective <strong>of</strong> whether or not they arecontained on the basic board. In order tomaintain consistency, several smaller stageson the basic board are also described.2.1 Standby power supplyThe Q <strong>2500</strong> receiver once again contains astandby power supply circuit, thus limiting currentconsumption in this mode to < 2 Watt.The use <strong>of</strong> a new CCU SDA 6000 on the signalboard increases the standby power consumptionfrom 1 W to 2 W, compared to theolder model. To meet the requirements <strong>of</strong> increasedpower consumption, there is now asmall, blocking oscillator type power supplyattached to the operating control, which suppliesthe U5 SB.Siemens Corporation has announced a newindex <strong>of</strong> the SDA 6000, that needs only 1 Wpower in standby operation. This will be implementedon the signal board, but thestandby power supply will not be changed.mode. All <strong>of</strong> this contributes to the standbymode’s low power consumption.2.1.1 Standby power supply circuitThe main voltage is fed via W 8103 the switchS 8101 and W 8611 to the basic board andcontinues via the line filter (C 612, T612,C613) and the 3-pole pin connector W613/BBback to pin 2/3 <strong>of</strong> operating control W 8613.The 220V is rectified by the bridge rectifier D8133 and smoothed by C 8133. The blockingoscillator type power supply consists essentially<strong>of</strong> the control circuit I 8131, in which theswitching transistor for the primary blockingoscillator winding is integrated, the transformerT 8101 and the opto-coupler I 8122. Anoperating voltage <strong>of</strong> about 18V is led fromwinding T 8101 pin1/2 via D 8138/D 8131 andC 8132 to I 8131 on pin 4. Control input I 8131pin 3 is supplied with secondary side currentcontrol information by opto-coupler I8122.This control circuit stabilises the secondaryside output voltage derived from the windingpin 5/8 <strong>of</strong> T 8101 at 5V. This is then fed via W8181 pin 8 to the signal board. I8122 is fittedwith an internal excess temperature, excesscurrent and excess voltage switch protection.The blocking oscillator type power supply operatesat a switching frequency <strong>of</strong> about 50kHz.The circuit itself is mounted together with theIR receiver and the LEDs on its printed circuitboard. It supplies the U5 SB, which maintainsfunctioning <strong>of</strong> the IR detector, the processorcircuit and the operating s<strong>of</strong>tware. The lasttwo circuits operate in standby mode, i.e. theclock frequency is reduced internally so thatonly those stages required to recognize aswitch-on command are maintained in operation.Because <strong>of</strong> the Nex<strong>TV</strong>iew function with U3.3 the <strong>TV</strong> RAM is retained in self refreshDocument Q <strong>2500</strong> 12 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Q<strong>2500</strong> Operating ControlT8101Standby transformer3 5MP04W8613VH-JSTws 7R92 3pol3from BB21R8134D8133DF08SF8133B8103R10C81334u7/400VT630mAMP031C813647nI8131VIPER1228734MP0265MP01R81380RD8131LL4148C813210u41D8138LL41482 8C8106470uI8122TLP621(BL)-D44132D8121BYG20DR8121470RI8123TL431ACLPR81221kC8123100nR81231k2R81241k5R812612kC8107100nL8106FE_PEC8103100nC8104100uU5SBU5SBW8181JST sw s8W86112pol sw 7R92to BB21642Overtravel contactL810121D8106LL4148Standby-LEDOvertravelON/OFF7654Mains21W81032pol ge 7R92531S8101C8118100nQ8114BC847BWR8113Q8111BC847BW2k2R811122kR811222kD8114R82041kLL4148R82191kR82020RD8202C12VD8201C12V321D8207redgreenD8207D8204C12VThe rectified secondary voltage is applied topin 2 <strong>of</strong> the relay winding L 8101. via protectiveresistor R 106. The cold end is open sinceQ114 is non-conducting and the receiver is instandby mode. This is indicated by illumination<strong>of</strong> the red LED.Transistor Q 8114 is blocked, if the workingcontact is open, the device is in standby,which is indicated by illumination <strong>of</strong> the redLED.If the processor receives an ON commandfrom the infrared detector it <strong>set</strong>s its appropriateswitch output to low level. This is then fedto the base <strong>of</strong> Q 8111 via pin 5 in plug W 8181which is blocked. Via R 813, U5 SB makestransistor Q 8114 switch. The cold end <strong>of</strong> therelay coil is earthed, the working contact isclosed and the main voltage flows to the mainpower supply circuit via pin 1 <strong>of</strong> W 8613,thereby switching the receiver on.2.2 Blocking oscillator type powersupplyThe voltage supply in the Q 2400 chassis isdrawn once again from a free-running blockingoscillator type power supply. TDA 4605 isused as the control and regulating circuit. Interms <strong>of</strong> its function, this IC resembles thewell-known TDA 4601.It has, however, a different type <strong>of</strong> outputstage. The 4605 is designed to control a fieldeffect transistor.This circuit uses a BUZ 91 MOS-FET as theswitching transistor. Since control <strong>of</strong> field effecttransistors requires virtually no current,reducing the need for heat dissipation, it hasbeen possible to eliminate the heat sink in theTDA 4605 control IC and house the circuit in adual-in-line package.Dokument Q <strong>2500</strong> 13 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>On the secondary side, BUZ 71 A V-MOStransistors are used to stabilise U3.3, U5 andU12 in order to keep power dissipation to aminimum.The converter transformer, which also providesthe standard VDE power distribution,has a primary working winding and a secondarywinding to supply voltage to the IC and togenerate a control voltage.Secondary windings also generate the followingvoltages:UBto supply the line output stageU 25 to supply the line driver stage2.2.1 Primary sideThe mains voltage flows through the mainspower switch, the working contact <strong>of</strong> thestandby relay and the mains RFI suppressionfilter to the degaussing coil, and via the startupcurrent limiter R 613 to the bridge rectifierD613.A voltage <strong>of</strong> approx. 310 V very rapidly buildsup at charging capacitor C 620. This is appliedto the drain terminal on the switching transistorvia the working winding in the convertertransformer.Since the gate BUZ 91 is not driven at thistime, there is no load on the operating voltage.U 3.3, U 5 and U 12predominantly to supply an operatingvoltage to the digital controlU9U8for the interface switching ICsfor the video ICsUNF+ and UNFusedto supply a floating voltage to theVF output stages, approx. + 18 VDocument Q <strong>2500</strong> 14 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Q<strong>2500</strong> blockingo oscillator type power supply, primary sideUBD680ZPY100R68047kC6691u/100VUBR6693k3R670100kI670TL431ACLPC67022nC6782n2D670C30VR66556kR6624k7/1%UBP6621kR663220k/1%UBR693220RR659*Typ-Var*D666SD103CC6714n7R6721kB663R62156kC622100uR6234k7R622820kC623 MP147220n3B635R10 MP12R634680kR625680kC621470n/100VMP1126I611TDA4605-35C6373n9/63VLIVE CIRCUITB619R10MP1581MP104MP13B630R10D622BA157R62710k/1%C630100p/500VC632R63022RR62422R220nR6361kR63282R23Q624BUZ91A-E3162L618FE_PEC6334n7R6332k2C6341u14R65118k/2%I669PS2561-1L-VD636BA157MP19R62622RR62922RC6364n7L626FE_PEC62822n/630V C627150p/1600VU7T639SMT+PFC2268D672C3V952019181715L619820uC624820p/1600VMP04D623STTA506F101614C620330U/450V13from BBW61121to demagnificationW618 1F611T3,15AR6131R5C612470n/310VT6122x18m5C619100n/250VC613470n/310VR6193to BBW61321FBI3.7L1M1-4D613MP03D617FUF5408C611470n/275VC6391n5/400VR63910M122C6141n/400VDocument Q <strong>2500</strong> 15 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>2.2.2 Start-upThe power supply section is started up by anadditional starting circuit. The required voltageis rectified using a diode path in the bridgerectifier. It is fed via resistor R 621 to pin 6 inTDA4605 where capacitor C 622 is thenslowly charged. During this charging phase,capacitor C 637 is charged to 6.6 V on pin 2via an internal IC path. A reference voltage <strong>of</strong>1V that is required during the start-up phaseand later during normal operation is also generatedin the IC.If the voltage at pin 6 reaches 12 V the IC operatesand makes the switching transistorconducting via pin 5. A current flows throughboth the transformer working winding and theswitching transformer drain source path. Duringthis period, magnetic energy is beingstored in the transformer. During this conductivephase, a drain current simulator C 637,integrated in the IC, is charged on pin 2. If theinternal reference value <strong>of</strong> 1 V is reached theIC blocks the switching transistor. The magneticfield in the transformer breaks down andthis induces voltages in the windings.The start-up procedure recommences and thesystem swings/oscillates to normal operation.This is arrived at when a voltage <strong>of</strong> 400 mVhas built up at pin 1.2.2.3 Normal and control operationA static state is <strong>set</strong> in normal operation atconstant load. The operating voltage for the ICis drawn from the transformer winding pin 5-6and rectified with D622. The voltage at pin 6 inthe IC is then 11 V. The control input at pin 1is 400 mV and the duty cycle for the zero passagedetector at pin 8 in the IC is <strong>set</strong>.The switching transistor is controlled with afixed frequency <strong>of</strong> between 20 and 40 kHz,which corresponds to the instantaneous load.If the load changes, the duty cycle at pin 8 inthe IC also changes. The negative edge indicatesto the IC when the energy stored in thetransformer has been dissipated. If the loadincreases, this occurs more quickly and the ICreduces the control frequency. If the load decreases,the control frequency increases. Thismeans that load variations between approx.40 and 260 W and mains voltage fluctuationsbetween 180 and 270 V can be compensatedfor.In order to achieve a higher UB voltage stability,regulation on the secondary side is nowused which influences the primary circuit’s I669 opto-coupler. The I 669 opto-coupler iscontrolled via I 670. The control mechanism isinfluenced via several paths:- With d.c. voltage via R 663- Alternating, by coupling to the R 680 diode.- When not under load, via D 672The operating voltage is <strong>set</strong> with the P662potentiometer. A small resistance here indicatesa high value <strong>of</strong> UB. Correspondingly, ahigh value <strong>of</strong> R means a low value for UB.If UB increases, e.g. due to a smaller load onthe line output stage, UB exerts a strongerinfluence via R 663 at the input <strong>of</strong> I 670. Thisresults in the I 670 cathode outputting asmaller voltage. The photodiode in I 669 receivesmore current through R 665. The pathbetween pin 3/4 <strong>of</strong> I 669 has a lower resistanceallowing for a higher voltage on pin 1 <strong>of</strong>I 611. Component I 611 then regulates outputvoltage until a value <strong>of</strong> 400 mV on pin 1 isreached again. If the value <strong>of</strong> UB becomeslower, then the regulation process is exactlythe inverse <strong>of</strong> that described here.Via D 680, R 669 and C 669, ripple voltagecomponents are coupled into the regulatingcircuit. In particular, this branch prevents a low50 hz ripple voltage arising on UB. With 60 hzsignal sources (NTSC, PAL 60 Hz or VGAoperation), this would result in humming interferencein the picture.Document Q <strong>2500</strong> 16 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Without secondary-side regulation, e.g. inSAT standby operation, UB would increase toapprox. 180 V. In this mode <strong>of</strong> operation,other voltages (e.g. the bias voltages for the U5, U 12 branch) do not alter significantly. Stabilizationis also guaranteed for these voltagesin this mode <strong>of</strong> operation.Due to the secondary-side stabilization withUB as stabilization factor, UB without any loadwould naturally remain constant. In this case,the power supply would regulate down fromapprox. 180 V (without secondary-side regulation)to the previously <strong>set</strong> value <strong>of</strong> UB, typically146 V. This would also result in all othervoltages being reduced. The bias voltages forthe stabilized voltages would be too low andthey would no longer be stabilized. The digitalelectronics would search for errors.In order to prevent this, the regulation acts viaU 7. This is accomplished via components D672, R 693 and 666.U 7 also drops when the line-output stage isdisconnected. When this has reached a value<strong>of</strong> approx. 6V, the D 666 Schottky diode voltagehas also fallen sufficiently for it becomesconducting. A further drop in operating voltageis prevented by the I 670 input. Stabilization <strong>of</strong>secondary side voltages, e.g. for U 5 and U12, still operate properly in this mode <strong>of</strong>operation.The indicator for this is the voltage on pin 6 inTDA4605. During normal operation this voltageis approx. 11 V. If the load increases, dueto a short circuit on the secondary side, forexample, the voltage on pin 6 drops. If it dropsbelow 7V, the logic circuit switches <strong>of</strong>f. Thesame occurs if the voltage on pin 6 exceeds15 V due to complete discharge or a fault inthe control circuit. There is also a second protectivecircuit to safeguard against overloading.If the current flowing through the workingwinding in the transformer and therefore alsothrough the switching transistor is so greatthat the voltage on pin 3 drops below 1 V, thepower supply also cuts out.In addition, integrated thermal protectionswitches the system <strong>of</strong>f at chip temperatures<strong>of</strong> over 150°.2.2.5 Power Factor ControlAll <strong>TV</strong> <strong>set</strong>s with power consumption <strong>of</strong> morethan 75 W, and delivered after 01.01.2001,must be fitted with a Power Factor Control(PFC) circuit.The circuit power supplies used up to nowoverlay a pulsed current on the sinusoidalmains alternating voltage. The Power FactorControl circuit ensures current extraction isalmost completely sinusoidal. This function isimplemented by changing the power supply’sinput rangePower Factor Control2.2.4 Protective operationT639The IC contains a protective circuit to preventthe control frequency from entering rangeswhere it would otherwise damage the switchingtransistor during over- and underload. Insuch cases the system is shut down.230V~R613D613D617C611L618C628D623C620Document Q <strong>2500</strong> 17 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>The alternating voltage from the mains is rectifiedby the D 613 bridge rectifier. When inresonance, C 620 is loaded to approx. 310 V.Without PFC this means that mains currentwill only be drawn when the sinusoidal halfwaveexceeds 310 V. Sinusoidal current extractionis therefore not guaranteed. With thePFC circuit, C 620 is not directly charged fromthe mains. Charging <strong>of</strong> C 620 is via the C 628current pump. When the Q 624 switchingtransistor is conducting, C 628 is connected toearth. C 628 is charged via D 617 and L 619.If Q 624 is now switched <strong>of</strong>f, a voltage <strong>of</strong>approx. 400 V is <strong>set</strong> on the drain.The energy stored both in C 628 and in thecoil can now charge up C 620 via D 623. C628 will naturally also be charged when thesinusoidal mains alternating voltage justcrosses zero and has a low value.Q 624 is switched with a frequency between20 kHz and 40 kHz, depending on load conditions.This also means that C 620 is chargedwith a current at the same frequency. Thecurrent drawn from the mains would also correspondto this frequency, but will be harmonizedby the mains input filter.2.2.6 Secondary sideAlthough the secondary side voltages arerelatively stable, and fast and transientchanges in load can be compensated for bythe field effect transistor in the primary side,stabilisation <strong>of</strong> voltages in the digital componentis still required.The two secondary voltages U 3.3, U 5, U 8,U 9 and U 12 are stabilisedFor the other secondary voltages:- UB for the horizontal stage- U 25 for the horizontal driver stage- UNF+ and UNF- for the VF output stageStabilisation is not required, as no current isdrawn from these non-controlled levels.Document Q <strong>2500</strong> 18 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Q<strong>2500</strong> blocking oscillator type power supply, secondary sideU-MuteC4924u7R4921kD4911N4148D652*Best-Var*W701to power supply unit <strong>TV</strong>O32U141 an L534/(UB)L650FE_PED651T639SMT+PFC2265810201918171516141312F656F3,15AR4913R3F672T5AF689L685FE_PEF661T4A*Best-Var*C0650150p/1600VL656FE_PED671STPS20L40CF1 3R6860R1L661FE_PER6870R1C688680p/500VR6574k7/1%D656EGP30FC661680p/500V2,4C65147u/250VC656680p/500VD663*Best-Var*C682D687BYW98-200UBD661*Best-Var*C6621000uD0681D686BYW98-200C687C689680p/500VC663B548R10B549R10R06584k7/1%U25U14Q663STP16NE06FPC6724700uC657470u/50V470u/50V330nC681L686FE_PER06891RC673330nR6901RR6604k7C6554u7C691Q674STP16NE06FPU+NFR684R6521RR685L687U-NFFE_PER6881RR683100uI674TL431ACLPQ682I691L78S09CV1 IN OUTGNDC692330nC66422nD660C12VU722R6614k7C67422nR6641kR675R678I676TL431ACLPR66618k/1%R6741k1k10k/1%R681R682R691*Best-Var*3C693330nI663L7808ACV1 IN OUT 3GNDC660100uR653100RC665 C668330n 470u/50VR6684k7/1%C677C666R67710k/1%R679100k220uQ681330nC552330nR56215kQ562STP16NE06FPR692*Best-Var*C694100uR654100RC667100uU5I569TL431ACLPU9U8U12U25C659D569C12V220uC658330nU3.3R5613k9/2%R56010k/1%Document Q <strong>2500</strong> 19 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>2.2.7 Voltage stabilisationFor each <strong>of</strong> the operating voltages U 3.3, U 5and U 12 a V-MOS transistor is used as ahorizontal controller for stabilisation. Theirgate voltages are kept constant by the connectedIC's I 569 for 3.3 V, I 676 for 5 V and I674 for 12 V. In addition, their control input isconnected to the voltage distributor by therespective output voltage.If the output voltage falls under high load, theIC's become high resistant causing the gatevoltage to increase and the horizontal controllersare controlled upwards further, whereuponthe output voltage increases again. If theload decreases the opposite occurs.In addition, voltages U8 for the video controland U9 for the interface with the fixed voltagecontrollers L 7808 and. L 78S09 are stabilised.The controllers I 663 and I 691 are nowalso located in the power supply. The inputvoltage is U 12.2.2.8 Voltage increaseTo avoid overloading the VF output phases,they are supplied with a load-dependent operatingvoltage. The control range <strong>of</strong> the circuitfor this lies between +18 V in no-load operationand +13 V at full load.The pulses taken from pin 14 <strong>of</strong> the transformerare rectified by D 681 and applied tothe emitter connections <strong>of</strong> transistors Q 682and Q681. For no-load or low-load operationno voltage is felt across current measurementresistor R 681. This means that Q 681 isblocked and Q 682 is switched through to itsbase with L level via R 684. The voltage frompin 14 <strong>of</strong> the transformer increases the VFoperating voltage to +18 V.If the noise level is increased, more current isdrawn accordingly. There is a correspondingvoltage drop across R 681, which means thebase <strong>of</strong> Q 681 goes more negative, the transistorswitches and as a consequence withbase Q 682 going positive, a greater or lesserdegree <strong>of</strong> blocking is achieved. The VF operatingvoltage is reduced accordingly.Harmonic distortion is therefore kept low. thuspreventing overheating <strong>of</strong> the output ICs. Inthis way a noise-level dependent video pumpingcan be prevented.Voltage increase for VF8T63914F689D68113R686D686L686UNF+C681R685Q682R681R687D687C687R684Q68110SM-Trafo12C689L687UNFÐR683R682Document Q <strong>2500</strong> 20 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>2.3.1 Horizontal driver2.2.9 Servicing informationFor repairs and fault-finding in the power supplyunit the following should be noted:Always connect the unit via an isolation transformer,especially when fault finding the primaryside.The horizontal driver stage is controlled fromI 2521 on the signal board via pin 13 fromconnector W 1511. The pulse at this point is2.5 Vss.U25The load on C 620 remains active long afterthe unit has been switched <strong>of</strong>f. Discharge theload if necessary via a low-resistance resistor.C521!R521T528D532R532T531Q534Operation <strong>of</strong> the power supply unit without thedigital unit is possible. For this pin 5 on pinconnector W 8181 is connected to earth, butnot until a voltage is applied to the standbypower supply. For specific failures, this testcan also be done with an integrated digitalcomponent.C527 R527C528D527C526R533Basic boardUBA check <strong>of</strong> the horizontal output stage cannotbe made by withdrawing the deflection plug.For this test L 534 must be unsoldered. Anextra load is not required.R526C524D526Q526A separate test <strong>of</strong> the power supply unit functionwithout interference from the chassis canbe achieved by unsoldering one side <strong>of</strong> thesecondary side rectifier diodes. The rectifierbranch for the UB (D 651) and U7 (671) mustbe available. The UB can then be loaded witha 100 Watt LED.U5R1044R2563Q2561R2561R2558R2562Signal boardQ2556 R2557HQ2951DEFLECTIONI 2521Video /deflectionprocessor879I 2801CCUU 7 and UB are necessary for power supplycontrol, so do not deactivate them.U52.3 Horizontal deflection and highvoltage productionOn the 100 Hz Chassis Q <strong>2500</strong> the horizontaldriver, horizontal output stage and high voltageproduction are essentially the same asthe predecessor.Capacitive control via C 524 prevents driverstage Q 526 being held conductive continuouslyif components are faulty or there are nocontrol pulses. Diode D 526 enables rapiddischarge <strong>of</strong> C 524, if Q 526 is controlled inthe blocking phase.Document Q <strong>2500</strong> 21 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>It can be clearly determined from the linedriver circuit, as from the control <strong>of</strong> the lineoutput stage, that this is a case <strong>of</strong> lowresistancecurrent control. The driver stage isequipped with a transistor, which supplies forthe drive transformer T 528 (conversion ratio7:1) output stage the required base controlcurrent <strong>of</strong> up to 0.9 Ass. To limit inductiveswitching peaks an R/C combination is connected,a.c. to earth, to the collector <strong>of</strong> Q 526after diode D 527. The driver stage operateswith respect to the output stage in alternatingoperation, i.e. if Q 526 is conducting, thenQ 534 is blocked and vice versa.2.4 Horizontal output stageAs mentioned in the previous section control<strong>of</strong> the horizontal output stage, or more preciselythe horizontal switching transistor, alternatesaccording to the switching regulatorprinciple. Essentially the base resistance consists<strong>of</strong> R 532 and the series secondary winding<strong>of</strong> the driver transformer T 528. The parallelarranged resistor R 533 dampens switchingpeaks arising in the inductivity.An additional anti-parallel diode from collectorQ 534 to earth, which was used as a boosterdiode in earlier forms <strong>of</strong> thyristor deflectionswitching, is not required, as in this switchingconcept the collector-base route <strong>of</strong> the switchingtransistor Q 534 fulfils the function <strong>of</strong> thebooster diode by a process <strong>of</strong> inverse operation.In practice the parallel O/W-modulationdiodes cause a perceptible load reduction <strong>of</strong>the switching transistor. The drawing belowshows that this inverse operation <strong>of</strong> the transistoroccurs during the first half <strong>of</strong> the trace,until about the middle <strong>of</strong> the line. In the secondhalf <strong>of</strong> the run the transistor operates asnormal with conducting base-emitter diode.Only during the relatively short flyback time isthe switching transistor blocked. The low resistancebase switching already describedenables the base peak current between +0.9A and –0.9 A in both directions to be dissipatedquickly.Document Q <strong>2500</strong> 22 © Loewe ProCollege

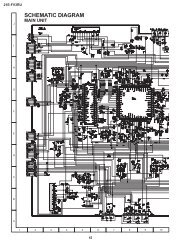

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Document Q <strong>2500</strong> 23 © Loewe ProCollegeC506???FE_PEL5432k2/0W5R50644uL506L537C5241uL5401m8C5402u2/350V47RR540L53022m3R3R5413R3R5343R3R5313R3R521C541C539L538R5431k51RR594R546220RQ526FXT653R53710k/1%R53610k/1%L534150uL533FE_PEL544L542D541BA1571N5822D537BA157D533D532C591C546470p/1000VESC011MD5392 13B534R10W5322pol grau1213polW5111312111098Q586BD537Q534Q533BF422Q532ZTX614Q531ZTX712B533R5R5921RR5911RR59010R1kR586R585150RR5551k2/1%220RR0553R549150k/2%R539100kR538100kR0535100kR53312R/1%R5324k7R530R5294k74k7R528R5274k7R52656RR5254k74k7R524R51810RR51722RR51622RT5284321L5901m6C590C555100nC544C543C542C53847u/250V100p/500VC537100uC535C534100uC533100p/500VC532100p/500VC531C528680p/500VC527220n/100VC526100p/500VC0521100u15712D527EU02V0BA157D546RU2MD531D5261N4148U25UBUVideoMP29MP28MP27MP20MP18MP17MP16MP02MP01HDRIVESEKGNDFPHFLBHDGNDHPOSQ<strong>2500</strong> horizontal output stageOW

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>It is conceivable that the essentially higheremitter currents (IE max. = 4.5 A) will invokeenormous "flooding" <strong>of</strong> charge carriers in theN-P- and P-N-transitions <strong>of</strong> the semiconductor.In order to guarantee rapid switchingbehaviour and to ensure rapid discharge<strong>of</strong> the charge carriers in the base zone, thebase control is correspondingly low resistance.32“/16:9/RF c.r.t.s, 142V at 21,24,28“/4:3 and136 V for all other c.r.t.s. The exact controland switching rhythm during a line period correspondsto the principle <strong>of</strong> the switchedresonant circuit. For this the line switchingtransistor operates via its three operating conditions- conduction, inverse conduction andblocked – in such a way that the charge anddischarge procedures <strong>of</strong> the collector capacityC 531 and inductivity T 531 determine theexact trace and flyback intervals.Screen+ II Abl.0- I+UU CE0- UTrace1st partInverseoperationTrace2nd partNormaloperationSwitchingtransistortOnly during the horizontal flyback time isQ 534 blocked for 6 µs. By charging the operatingvoltage the capacitor <strong>of</strong> the parallel resonancecircuit C 531 forms the positive halfwave <strong>of</strong> a sinusoidal oscillation. C 531 andT 531 are dimensioned in such a way thatthey create horizontal flyback pulses. Thenatural desire <strong>of</strong> a parallel resonance circuit toconvert the stored charge in the capacitor intoinductance as magnetic energy leads to reversal<strong>of</strong> polarity <strong>of</strong> the current.Normally the negative component <strong>of</strong> the sinosoidaloscillation is felt on the collector <strong>of</strong>Q 534. This attempt is however prevented bythe collector-base diode path <strong>of</strong> Q 534.On reaching the start up voltage the diodepath becomes conductive and cuts the negativecomponents. In these cases the E/Wmodulator diodes support this function,whereby in the switching transistor the powerdissipation <strong>of</strong> the transistors is reducedIn this respect it must be mentioned that thecontrol pulses are specially formed for thedual functionality <strong>of</strong> Q 534 normal and inverseoperation. In principle the trace relationship <strong>of</strong>the base control <strong>of</strong> 6 µs flyback and 26 µstrace time is changed to 14 µs flyback and18 µs trace time. In this way it is possible, toprocess unavoidable production dispersion <strong>of</strong>the driver transformer. By means <strong>of</strong> promptcontrol the switching transistor has sufficienttime to prepare for the following operationalphase.The horizontal deflection pulses are detacheddirectly from the collector <strong>of</strong> the switchingtransistor on the parallel deflection winding.Between the base point <strong>of</strong> the horizontal deflectorand the E/W diode modulator theeast/west correction information is coupled inaccordance with the dual generator principle.This procedure is almost non-reactive withrespect to the primary winding <strong>of</strong> the highvoltage transducer.The operating voltage <strong>of</strong> the horizontal outputstage is taken from the switch mode powersupply and is 146 V for 33“/4:3 andDocument Q <strong>2500</strong> 24 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>2.4.1 High voltage productionQ<strong>2500</strong> secondary H output stageThe filament voltage <strong>of</strong> the c.r.t. is assigned topin 9. On pin 4 the flyback pulse for the synchronisation<strong>of</strong> the control is assigned to pin 4.At the same time this pulse is rectified byD547 and fed to the c.r.t. plate via connectorW 549. The 60V occurring here is required bythe c.r.t. PCB for the speed modulator. TheUV+ and UV- for the vertical stage (approx. +13 V) occur in the windings between pin 6 and9 and pin 3 and 9.C532100p/500VD531RU2MR5313R312B533R5T53116W511Pin10 Pin11R5502k2R5421k8/2%32kVHFLBR548120RFPR545Just like the amplitude <strong>of</strong> the radiation currenta corrective voltage for the stabilisation <strong>of</strong> thehorizontal amplitude can be tapped at thebase, connection 10 <strong>of</strong> the high voltage winding.This radiation current dependent voltage is ledto the signal board via pin 11 <strong>of</strong> connectorW 511. The radiation current fuse and limiterare found here.R5343R35MP2017FOCUS13FOCUSUG2104869C54922nD5481N4148R5473R3L553R5581RD549C30VD547BA159C547100p/500VD558RU2MC556100p/500VB560R5C5502200uR551150k/2%R5521MC54822u/250VUV-C51122u/250VW550UVideo 5UF 43USVM21The operating voltage U 200 for the videooutput stage is tapped on the primary side <strong>of</strong>the pin 5 <strong>of</strong> the diode split transformer andrectified by D 531. In addition on connection 5another voltage UB -10 V and on pin 7 a voltage<strong>of</strong> UB +10 V are produced, which are felton capacitors C 535 and C 534. On UB = 136V there are 126 V and 146 V. These voltagesare required for the <strong>of</strong>f<strong>set</strong> correction <strong>of</strong> thehorizontal deflector.3R5571RC5582200uD557RU2MUV+2C557100p/500V2.4.2 Horizontal- <strong>of</strong>f<strong>set</strong> deflectorThe high voltage transducer also contains thecascade. The secondary winding <strong>of</strong> the stepup transformer is divided into four and thehigh voltage rectifier diodes are connectedbetween the individual winding sections. Thisform <strong>of</strong> high voltage production is possiblewithout the highly charged capacitors used upto now, which increases the reliability <strong>of</strong> highvoltage production and makes possible aspace-saving compact solution.The deflector pulse is formed in such a waythat through the deflection and S-correction alinear deflection results. This only functionshowever when the deflection is exactly central.As the Q <strong>2500</strong> chassis could also be usedas a VGA monitor, high demands are placedon linearity. For this reason the possibility <strong>of</strong><strong>of</strong>f<strong>set</strong> correction is created.The resistance voltage divider and the potentiometer<strong>of</strong> the focus and G2 adjustment isintegrated mechanically into the splitting combinationfor units with 4:3 c.r.t.s.Document Q <strong>2500</strong> 25 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>A free DAC in I 2271 is used for horizontal<strong>of</strong>f<strong>set</strong> correction. The d.c. voltage felt on pin55 can be <strong>set</strong> in the servicing mode. This isfed via connector W 511 /W 1511, pin 8, to thebase <strong>of</strong> transistor Q 533 on the basic board.Q 533 together with R 555 represents a currentsource for the push-pull stage Q 531 andQ 532. The operating point for the push-pullstage is <strong>set</strong> with R 537 and the parallel circuit<strong>of</strong> R 535/538/539. At rest the operating voltage<strong>of</strong> the line output stage is applied to thebase connections <strong>of</strong> Q 531/532 and both transistorsare blocked.If I 2271 increases the base voltage <strong>of</strong> transistorQ 533 and this then conducts, the basevoltage <strong>of</strong> the push-pull stage drops and Q531 conducts. This means the d.c. current ismade more negative by resistors R 516,R 517 and R 518 and coil L 530, whereby thedeflection shifts to the left.If, on the other hand, the voltage on pin 27 <strong>of</strong>I 2271 drops, transistor Q 533 becomes highresistance and the base voltage on the pushpullstage increases. This means Q 532 conductsand L 530 increases the voltage on pin2 <strong>of</strong> the deflection coil. This leads to a shifting<strong>of</strong> the d.c. current component in a positivedirection and deflection to the right. Coil L 533serves as d.c. current coupling for the deflection.2.5 East/west correctionIn order to compensate for the pincushion(distortion) in 110° units in an east/west direction,the horizontal deflection current in thevertical centre must be increased with respectto the vertical start and vertical end. The rightdegree <strong>of</strong> correction is achieved by influencingthe horizontal deflection current with a verticalfrequency parabola in the east/west diodemodulator.Two generators connected to each other by abridging circuit provide the correction signalfor the E/W modulator for the horizontal deflectioncurrent.G1G2C1C2L1L2UB2D1D2UB1In the above drawing the two generators, G1 =horizontal generator, and G2 = east/west generator,are represented only by their resonantcircuits. The deflection current in the deflectioncoil L1 is supplied by both generators. Sothat the high voltage is not influenced by theE/W modulator, the voltage on transformer THis determined only by the horizontal generatorG1. Therefore, for correct bridge compensationduring the line trace, only E/W modulation<strong>of</strong> the deflection current takes place in an almostnon-reactive fashion on the horizontaloutput level. For improved clarity the conceptualflow diagram above is shown in the followingdrawing with the actual componentlocations.STHDocument Q <strong>2500</strong> 26 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>C541C5432.5.1 CircuitThe components <strong>of</strong> the east/west outputstage, as well as the diode modulator are locatedon the basic board.W511Pin1VPROTR598C596R596Q597Q596R597Hor.vom Signal-BoardHorizontaldeflectorE/WchargingcoilC590Q534C581R581R582Q582C582R583Q589D584D539aD539bQ534C541R585D539aD539bUBE/W correctionR587C589R584L543C531C543R588Q593R589L539L588C588Q59312 3L541L536U12R593R592R591SplittingtransformerT531R590L590D590D589The video/deflection processor TDA 9332 appliesa d.c. underlying parabola type voltageto pin 3. This Information contains all correctionsfor picture width and east/west. The followingamplifier stage, consisting <strong>of</strong> transistorsQ 582 to Q 589, could therefore be implementedsimply as a conventionally baseddifferential amplifier.Control is via low-pass filter R 581, C 581 andR 582 on the base <strong>of</strong> transistor Q 582. Thelow-pass filter suppresses any noise componentsfrom the pulse width generator inI 2521.The base <strong>of</strong> transistor Q 589 is determined bythe voltage divider R 588/R 589 in d.c. andthereby determines the operational point <strong>of</strong>the differential amplifier.The amplification <strong>of</strong> the differential amplifier isdetermined essentially by the relationship <strong>of</strong>the negative feedback resistance R 583 andthe output resistances R 581/582. The parabolatype voltage, amplified to 12 V by outputstages Q 585 and Q 586, is fed via the E/Wcharge coil to the diode modulator. Dual diodeD 539 superimposes the deflection current onit and the E/W correction is implemented.Transistor Q 593 was incorporated to protectthe output stage transistor Q 586 in the event<strong>of</strong> the deflection connector being withdrawn.Normally Q 593 acts as positive feedback toQ 586. If the deflection connector is withdrawnthe current increases through Q 586 andtherefore also through resistors R 591 /R 592.This causes Q 593 to conduct and the powerloss in Q 586 to be returned to a normal level.In the event <strong>of</strong> a fault the two transistorsQ 596 and Q 597 ensure that the unitswitches to protective operation. Q 596 isconductively controlled by a reduced basevoltage. Q 597 conducts and controls VPROTat low level. The CCU protective circuit respondsand switches the unit <strong>of</strong>f.R586Q586C590Document Q <strong>2500</strong> 27 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>2.6 Vertical output stageIn comparison with earlier models the Q <strong>2500</strong>generation <strong>of</strong> chassis does not have an a.c.coupled, but a d.c coupled vertical outputstage. This has the advantage that the verticaldeflection coils can be supplied with currentdirectly and the large coupling capacitor canbe dispensed with. This means that verticalcorrection information can operate directly,without vertical distortions caused by the deflectioncoil coupling capacitor.As we know, a positive and a negative deflectioncurrent flow through the vertical deflectioncoils. In order for the d.c. coupled output stageto produce this negative current, it must besupplied with a +/- voltage.The two possible variants <strong>of</strong> the vertical outputstage IC´s (TDA 8177/S<strong>TV</strong>9379FA) incorporatedinto the 100 Hz Q <strong>2500</strong> chassisare housed in a Heptawatt plastic housing.The following functional groups are incorporatedinto the IC´s as circuit components:• A power operational amplifier that is able todrive the vertical deflection coils with apeak deflection current up to 3 Ass.• A flyback generator, that generates thevoltage charge for the vertical flyback.• A temperature protection circuit that limitsthe deflection current on overload.The power operational amplifier is controlledsymmetrically and inversely on its noninvertingand inverting inputs. Therefore, thevideo/deflection processor outputs two inverselysymmetrical vertical control signals.Vertical output stageV+ VÐV-FlybackR566R578W 511Pin 1VPROTW 511Pin 4R563C564C563C567R565C579 R579 C578R573D561UV+16VUV--13V246 3 7I 561FlybackGeneratorTDA 8177/S<strong>TV</strong>9379A1-+5R564R567R569VerticaldeflectioncoilsTemperatureprotection circuitR574R568C568Document Q <strong>2500</strong> 28 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>W 511Pin 4Vertical output stageV-FlybackR559R563 C564U-SVMPicture formation is normally established bythe d.c. current component <strong>of</strong> the deflectioncurrent. This means that for a d.c. coupled Voutput stage, by simply changing the d.c.components <strong>of</strong> the control sawtooth, the d.c.component <strong>of</strong> the deflection current can bechanged, and with it the picture formation.C561D561UV+13VUV--13V246 3FlybackGeneratorS<strong>TV</strong>9379FAI 5612.6.1 Flyback generatorThe job <strong>of</strong> the flyback generator is to provide,the switching voltage for the voltage increaseduring the vertical flyback. The problem withthis is as follows:These two control signals contain all verticalcorrection information. This means that outputside S correction, which is necessary for a.c.coupled output stages, can be dispensed withcompletely. The component insert at the output<strong>of</strong> the V output stage is also considerablyreduced. Symmetrical control almost fullysuppresses interference that can affect thetwo V control signals due to the very highcommon mode rejection ratio <strong>of</strong> the V-poweroperating amplifier. The two V control signalsV+/V- are applied to the pin connector W 511,pin 2/3 and reach the series resistors R 566/R 578 via the inputs on pin 1/7 <strong>of</strong> the V outputstage I 561. The sawtooth, which is amplifiedabout 10 times, is output by pin 5 <strong>of</strong> I 561 andforces the current through the vertical deflectioncoils.The R/C combination 568, from the output <strong>of</strong>pin 5 to earth, prevents the tendency <strong>of</strong> theoutput stage to oscillate and protects it fromswitching peaks that can be caused by thedeflection coins. To stabilise the V outputstage, part <strong>of</strong> the sawtooth from the base <strong>of</strong>the deflection coils is fed back via resistorR 579 to the inverted input pin 1 .The energy requirement <strong>of</strong> the vertical outputstage is at its highest during the flyback, asthe electron stream has to be directed rapidlyfrom the lower right corner <strong>of</strong> the screen to thetop left corner.This transitory additional energy requirementis achieved by doubling the operating voltage,which is only available for the vertical outputstage. During the vertical trace, the bootstrapcapacitor C 563 is charged to approx. 26 V viaD 561. The output <strong>of</strong> the flyback generator atpin 3 <strong>of</strong> I 561 at this point is UV-/-13 V. At thetime <strong>of</strong> flyback start, the flyback generator isswitched by the output stage output at pin 5and applied to the output at pin 3 UV+/ +13 V.Due to the d.c. shift on the minus pin <strong>of</strong> capacitorC 563, the operating voltage for theoutput stage on pin 6 increases by the voltagein C 563. At the same time, D 561 is blocked,which prevents the charge in the power supplyleaking away. This means that for rapid flybackthere is a transitory +40 V (approx.) operatingvoltage available.For many c.r.t. types the flyback pulse is notsufficient to fully return the deflection beam,so that flyback lines are visible.Dokument Q <strong>2500</strong> 29 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>In these devices the V output stage <strong>of</strong>S<strong>TV</strong>9379FA is used. For the flyback generatorthis has an independent voltage supply. AUSVM/60V is used that is fed to the I 561 viathe fused resistor R 559 on pin 3.If the V output stage is changed during servicethen ensure it is replaced with the same type.The two IC variants are not compatible.2.6.2 Vertical protection circuitsProtection circuits are used to protect the c.r.t.against burning if the vertical deflection fails.For a d.c. coupled V output stage a fault situationcan theoretically occur in which the deflectionsaw tooth appears to be available, buta faulty d.c. component directs the electronbeam to the upper or lower end <strong>of</strong> the c.r.t.neck. This could cause the c.r.t. neck to meltand lead to destruction <strong>of</strong> the c.r.t. neck.To prevent this a V saw tooth is taken fromthe base <strong>of</strong> the V deflection coils with R 573and a d.c. voltage is applied to the signalboard with R 2651.U40V13VVertical protective circuit via CCUtBasic boardC563C564R563W1731Pin 4R1036Signal boardU5R2594D2594I 2801CCU/Pin94D2661D2586UV+D56126 3FlybackGeneratorD2591D1769R2593C2592/93R2594Q2594R2586UV-4I 561TDA 8177Bild 2 - 15This VPROT signal is fed to the protectivecircuit that consists <strong>of</strong> the dual operationalamplifier I 2651. Operational amplifier A workson its non-inverting input pin 3, with referencevoltage <strong>of</strong> 3 V and operational amplifier B onits inverting input pin 6 with 5 V. If the VPROTsignal - Diagram A – does not fall below orexceed the reference values <strong>of</strong> 3V and 5 V,then the V deflection and the vertical d.c.component through the deflection coils is correct.If the d.c. component is too positive ortoo negative - Diagrams B + C – this is interpretedas a fault. If, for example, the d.c.component <strong>of</strong> the VPROT signal is too small(5V DiagramB ) pin 7 goes from OP B to H level andthe CCU switches the device <strong>of</strong>f.Document Q <strong>2500</strong> 30 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Vertical protective circuit via CCUCCU Pin 94D2657LL4148R2656100R7I2651LM 3588+B-456R26633k3R26544k7R26515V4k7U8C2650100nU3.3D2596LL103CR266122kD2661LL4148D2667LL4148C2662100nR2666100R 1I2651ALM 358+A-323VR26644k7MP002R1031100RC103122nW 1511/ Pin 1Signal boardV+ V-I 561+-R579VerticaldeflectioncoilsVPROTW 511/ Pin 1Basic boardC578R574R573UMP 350,8VUMP024,5V3,5V0Vt0Vt-0,8V5Va.)3VUVPROTI2651/Pin6I2651/Pin3tb.)U5V3V0VI2651/Pin6I2651/Pin3td.c. current component much too positivec.)U5V3V0VI2651/Pin6I2651/Pin3td.c. current component much too negativeDokument Q <strong>2500</strong> 31 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>Beam current limitationD531R53112(9)C51132kVR552UvidR551Signal boardR2604R2611U8D2611R2603BCLC2604C2603I 252143 Video/deflectionProcessor14 45T53110FocusUG2D548 D549C549W511/Pin11Basic boardFPW1511/Pin11R2609C2608R2608R1043D2544FPR2608R2607 D2607R2606R2544D2549R2547R2552E/W amp. compensationPhase compensationR2636R2549Q2638R2637R2638C2638Q2639R2546U8The second protective switch monitors the Vflyback pulse that is fed from I 561 /pin 6 viaR 563 to the pin connector W 511 /pin 4. Onthe signal board this V flyback pulse is rectifiedby diode D 2591/1769 and integrated withcapacitor C 2592/2593. With the voltage availableon capacitor C 2992/2593, Q 2594 conducts.The collector <strong>of</strong> Q 2594 is then at thesame potential as L, and diode D 2594 isblocked.If there is no flyback pulse due the absence <strong>of</strong>a V output stage, no voltage can build up oncapacitors C 2592/2594 and Q 2594 blocks.Pin 94 <strong>of</strong> the CCU is <strong>set</strong> to H level via diode D2594.If pin 94 <strong>of</strong> C 161 is <strong>set</strong> to H level by the absence<strong>of</strong> a V flyback pulse in the operatingcondition <strong>of</strong> the unit, as described, after 2seconds the CCU switches the device back tostandby operation. This permits safe shutdown <strong>of</strong> the device with a faulty deflectioncontroller.2.7 Beam current limitationTo limit the beam current the Q <strong>2500</strong> chassisis provided with an average value control. Thelimit switch is integrated into TDA 9332.Document Q <strong>2500</strong> 32 © Loewe ProCollege

<strong>Technology</strong> <strong>of</strong> Q <strong>2500</strong> <strong>colour</strong> <strong>TV</strong> <strong>set</strong>The switch to limit the contrast and brightnessis controlled with a d.c value via pin 43.The switch is designed in such a way that fora voltage <strong>of</strong> >3.3 V there is no limitation oncontrast and brightness.For a voltage between 3.3 and 2.2V the contrastis reduced in proportion to the voltage. Ifthe voltage drops below 1.8 V the brightnessas well as the contrast is reduced. At approx.1 V on pin 15 the brightness and the contrastare reduced by 100%, whereupon the screenis black.To achieve beam current limitation the base <strong>of</strong>the diode split transformer influences the d.c.value on pin 43 <strong>of</strong> TDA 9332. Inversely proportionalvoltage information on the beam currentcan be obtained at the base.In order for the TDA pin to be at >3.3 V with abeam current <strong>of</strong> zero, the base <strong>of</strong> the transformeris connected to U 200 via R 551/552.The positive voltage in this operational state ischarged via resistors R 2608, R 2609 andR 2611 <strong>of</strong> Elko C 2603 and on pin 43 <strong>of</strong> theTDA there is a voltage <strong>of</strong> >3.3 V; there is nobeam current limitation.As the high voltage winding in the diode splittransformer operates with a virtual earth, thebase becomes negative with increasing beamcurrent, whereby C 2603 via R 2608, R 2609and R 2611 can be correspondingly dischargedto a greater or lesser degree and thebeam current controlled.Diodes D 2607 and D 2611 are provided sothat the circuit can also react to jumps inbeam current. They ensure the rapid discharge<strong>of</strong> C 2603.In addition, for a 4:3 display in a 16:9 <strong>TV</strong> <strong>set</strong>,from pin 113 <strong>of</strong> I 2311 via Q 2612 and R 2601,the voltage on C 2603 drops. This corrects thebeam current limitation for the smaller screenarea. (see also signal board deflection).CCU Pin 94Overbeam current protective circuitU3.3D2596LL103CR258622kC2618100nD2618LL4148Q2616BC847BWR261810kC26161uU5R2617220kR2616220kC2608100nR260822kR260618k100RR1043100RC10431n111213FPW15112.7.1 Overbeam current fuseIn correct operation the beam current measurementinput on pin 43 <strong>of</strong> TDA is at a d.c.level <strong>of</strong> 2 to 4 V. According to the level, theRGB output amplifier in this IC is controlled toa greater or lesser extent, which ensures thatthe beam current limitation is implemented.If the c.r.t. is controlled upwards to the fullextent, even though the gain <strong>of</strong> the amplifierhas been fully reduced , which can occur ifthere is a fault in the RGB output stage or itsDocument Q <strong>2500</strong> 33 © Loewe ProCollege