TSC2101-Audio Codec w/ Integrated Headphone Speaker Amp ...

TSC2101-Audio Codec w/ Integrated Headphone Speaker Amp ...

TSC2101-Audio Codec w/ Integrated Headphone Speaker Amp ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

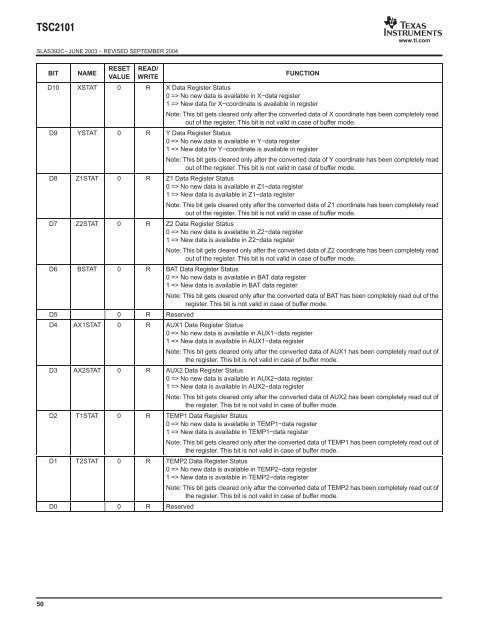

SLAS392C− JUNE 2003 − REVISED SEPTEMBER 2004www.ti.comBITNAMERESETVALUEREAD/WRITEFUNCTIOND10 XSTAT 0 R X Data Register Status0 => No new data is available in X−data register1 => New data for X−coordinate is available in registerNote: This bit gets cleared only after the converted data of X coordinate has been completely readout of the register. This bit is not valid in case of buffer mode.D9 YSTAT 0 R Y Data Register Status0 => No new data is available in Y−data register1 => New data for Y−coordinate is available in registerNote: This bit gets cleared only after the converted data of Y coordinate has been completely readout of the register. This bit is not valid in case of buffer mode.D8 Z1STAT 0 R Z1 Data Register Status0 => No new data is available in Z1−data register1 => New data is available in Z1−data registerNote: This bit gets cleared only after the converted data of Z1 coordinate has been completely readout of the register. This bit is not valid in case of buffer mode.D7 Z2STAT 0 R Z2 Data Register Status0 => No new data is available in Z2−data register1 => New data is available in Z2−data registerNote: This bit gets cleared only after the converted data of Z2 coordinate has been completely readout of the register. This bit is not valid in case of buffer mode.D6 BSTAT 0 R BAT Data Register Status0 => No new data is available in BAT data register1 => New data is available in BAT data registerNote: This bit gets cleared only after the converted data of BAT has been completely read out of theregister. This bit is not valid in case of buffer mode.D5 0 R ReservedD4 AX1STAT 0 R AUX1 Data Register Status0 => No new data is available in AUX1−data register1 => New data is available in AUX1−data registerNote: This bit gets cleared only after the converted data of AUX1 has been completely read out ofthe register. This bit is not valid in case of buffer mode.D3 AX2STAT 0 R AUX2 Data Register Status0 => No new data is available in AUX2−data register1 => New data is available in AUX2−data registerNote: This bit gets cleared only after the converted data of AUX2 has been completely read out ofthe register. This bit is not valid in case of buffer mode.D2 T1STAT 0 R TEMP1 Data Register Status0 => No new data is available in TEMP1−data register1 => New data is available in TEMP1−data registerNote: This bit gets cleared only after the converted data of TEMP1 has been completely read out ofthe register. This bit is not valid in case of buffer mode.D1 T2STAT 0 R TEMP2 Data Register Status0 => No new data is available in TEMP2−data register1 => New data is available in TEMP2−data registerNote: This bit gets cleared only after the converted data of TEMP2 has been completely read out ofthe register. This bit is not valid in case of buffer mode.D0 0 R Reserved50