section 7 - Index of

section 7 - Index of section 7 - Index of

zero (bit 2) .................... 5-10, A-17 memory expansion port (port A) ..... 2-6Condition Codes ........................ A-3 on-chip emulator (OnCE) .......... 2-6Convergent Rounding .................... 3-6phase-locked loop (PLL)based clocking ............ 2-6program control unit .............. 2-5-0--E-DataALUdouble precision multiply mode ........ 3-16MAC ............................ 3-13 Edge Sensitive ........................ 7-16MAC and logic unit .................. 3-6 Edge Triggered ......................... 5-6programming model ................ 3-19 Electronic Bulletin Board ................. 11-7summary ......................... 3-19 Encodings .......................... A-311Data ALU Accumulator Registers ........... 3-7 condition code and address .......... A-315Data ALU components ................... 3-3 double-bit register ................. A-312Data ALU Registers ................. 3-3,6-6 effective addressing mode ........... A-315input registers ...................... 3-5 five-bit register .................... A-314operands table ..................... A-5 four-bit register ................... A-313Data Arithmetic Logic Unit (see Data ALU) ... 3-3 memory space bit ................. A-314Data Bus Move Field .................... 6-5 no parallel move .................. A-318Data Bus Signals (00-015) ........... 8-3, 8-5 nonmultiply instruction .............. A-332Data Buses ............................ 2-3 parallel instruction opcode ........... A-330Data Conversion ....................... 3-11 parallel move ..................... A-316Data Organization ................... 6-6, 6-9 program control unit registers ........ A-315Data Shifter/Limiter ...................... 3-9 single-bit register .................. A-312DEBUG .............................. A-76 six-bit register .................... A-314Debug Mode triple bit register ................... A-313entering . . . . . . . . . . . . . . . . . . . . . . . .. 10-14 write control . . . . . . . . . . . . . . . . . . . . .. A-314Debug Request Input (DR) ............... 10-6 ENDDO ............................. A-98Debug Serial Output (DSO) .............. 10-5 ENDDO Instruction Restrictions ............ 7-9DEBUGcc ............................ A-78 EOR .............................. A-100DEC ................................ A-80 Exception (Interrupt) Priorities ............. 7-12Design Verification Support .............. 11-3 Exception Processing State .............. 7-10DFO-DF3 ............................ 9-12 EXTALDIV ................................. A-82 synch w/CKOUT ................... 9-14DO ................................. A-88 Extension Bit ..................... 5-11 , A-16DO Instruction Restrictions ................ 7-8 External Interrupt Request Pins ............ 5-6DO loop control ......................... 2-5Double Precision Multiply Mode ........... 3-16algorithm examples ................. 3-16-F-Double Precision Multiply Mode Bit ........ 5-13Fast Interrupt ..................... 7-10,7-12Dr. BuB .............................. 11-7Fast Interrupt Execution ................. 7-26DSP Applications ....................... 1-7FFT Code ......................;..... B-3DSP Functions ......................... 1-7FIR Filter ............................. B-3DSP News .......................... 11-16Frequency Multiplication .................. 9-3DSP56K Central ArchitectureFrequency Multiplier ..................... 9-5central components . . . . . . . . . . . . . . . . . . 2-3address buses .................. 2-4address generation unit ........... 2-5-GdataALU . . . . . . . . . . . . . . . . . . . . . . . 2-5data buses ..................... 2-3 Global Data Bus (GOB) ................... 2-3

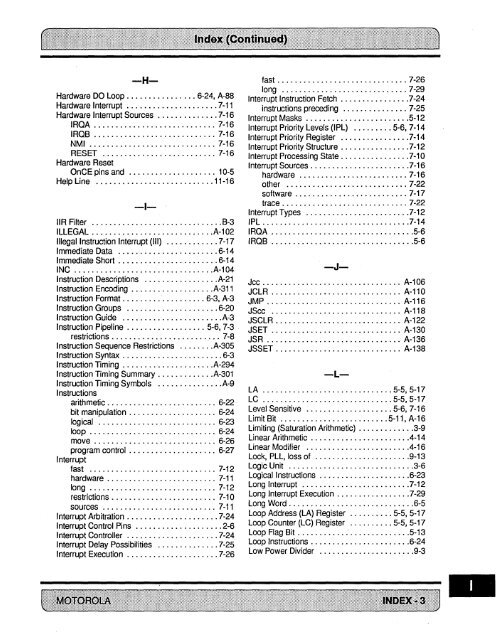

-H- fast .............................. 7-26long ............................. 7-29Hardware DO Loop ................ 6-24, A-88 Interrupt Instruction Fetch ................ 7-24Hardware Interrupt ..................... 7-11 instructions preCeding ............... 7-25Hardware Interrupt Sources .............. 7-16 Interrupt Masks ........................ 5-12IROA ....... , .................... 7-16 Interrupt Priority Levels (IPL) ......... 5-6, 7-14IROB ............................ 7-16 Interrupt Priority Register ................ 7-14NMI ............................. 7-16 Interrupt Priority Structure ......... , ...... 7-12RESET .......................... 7-16 Interrupt Processing State ................ 7-10Hardware ResetI nterrupt Sources ....................... 7-16OnCE pins and .................... 10-5 hardware ......................... 7-16Helpline ........................... 11-16 other ............................ 7-22software .......................... 7-17trace ............................. 7-22Interrupt Types ........................ 7-12IIR Riter .............................. B-3 IPL .................................. 7-14ILLEGAL ............................ A-102 IROA ........ , ........ ' ........... , ... 5-6Illegal Instruction Interrupt (III) ............ 7-17 IRQB ................................. 5-6Immediate Data ..............•........ 6-14Immediate Short ....................... 6-14INC ................................ A-104Instruction Descriptions ................. A-21Instruction Encoding ................... A-311Instruction Format ................... 6-3, A-3Instruction Groups ..................... 6-20Instruction Guide ....................... A-3Instruction Pipeline .................. 5-6, 7-3restrictions . . . . . . . . . . . . . . . . . . . . . . . . . 7-8Instruction Sequence Restrictions ...... : .A-305Instruction Syntax ....................... 6-3Instruction Timing ..................... A-294Instruction Timing Summary ............. A-301Instruction Timing Symbols ............... A-9Instructionsarithmetic ......................... 6-22bit manipulation . . . . . . . . . . . . . . . . . . . . 6-24logical ........................... 6-23loop ............................. 6-24move ........................ , ... 6-26program control . . . . . . . . . . . . . . . . . . . . 6-27Interruptfast ............................. 7-12hardware ......................... 7-11long ............................. 7-12restrictions . . . . . . . . . . . . . . . . . . . . . . . . 7-1 0sources .......................... 7-11Interrupt Arbitration ..................... 7-24Interrupt Control Pins .................... 2-6Interrupt Controller ..................... 7-24Interrupt Delay Possibilities .............. 7-25Interrupt Execution ..................... 7-26Jcc ................................ A-106JCLR .............................. A-110JMP ...................... '" ...... A-116JScc .............................. A-118JSCLR ............................ ' A-122JSET ............................. , A-130JSR .................. , ....... , .... A-136JSSET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-138-1--J--L-LA .............................. 5-5, 5-17LC .............................. 5-5,5-17Level Sensitive .................... 5-6, 7-16Limit Bit ......................... 5-11 A-16Limiting (Saturation Arithmetic) .......... .' .. 3-9Linear Arithmetic ...................... .4-14Linear Modifier ........................ 4-16Lock, PLL, loss of ...................... 9-13Logic Unit ............................. 3-6Logical Instructions ..................... 6-23Long Interrupt ......................... 7-12Long Interrupt Execution ................. 7-29Long Word ............................. 6-5Loop Address (LA) Register .......... 5-5, 5-17Loop Counter (LC) Register .......... 5-5, 5-17Loop Flag Bit .......................... 5-13Loop Instructions ....................... 6-24Low Power Divider ...................... 9-3

- Page 549 and 550: Immediately before MOVEC from SSH o

- Page 551 and 552: A.9.S REP RestrictionsThe REP instr

- Page 553 and 554: Table A-18 Triple-Bit Register Enco

- Page 555 and 556: Table A-24 Program Control Unit Reg

- Page 557 and 558: R: Register to Register Parallel Da

- Page 559 and 560: JSSETJSSET#n,X:pp,XXXX#n,Y:pp,xxxx2

- Page 561 and 562: JSSET#n,S,xxxx23 16 15 87 000001011

- Page 563 and 564: BCHGBCHG#n,X:aa#n,Y:aa23 16 15 87 0

- Page 565 and 566: MOVE(M)MOVE(M)S,P:aaP:aa,DREP #XXXR

- Page 567 and 568: LUAea,O23 16 15 87 0I 0 0 0 0 0 1 0

- Page 569 and 570: ENDDO23 16 15 87 00 0 0 0 0 0 0 o 1

- Page 571 and 572: Table A-28 Operation Code QQQ Decod

- Page 573 and 574: Table A-30 Special Case #10 P E R C

- Page 575 and 576: NEGD23 87 43 0DATA BUS MOVE FIELDLS

- Page 577: ADDRS,D23 87 43 oDATA BUS MOVE FIEL

- Page 580 and 581: lEI

- Page 582 and 583: Table 8-1 27-MHz Benchmark Results

- Page 584 and 585: .*._---*-----*-------**-------....

- Page 586 and 587: ;Latest Revision - September 30, 19

- Page 588 and 589: All coefficients are divided by 2:w

- Page 590 and 591: Real input FFT based on Glenn Bergl

- Page 592 and 593: countountcountcountorg y:coefset 0d

- Page 594 and 595: ; Real-Valued FFT for MOTOROLA DSP5

- Page 596 and 597: ; first group in the last passmove

- Page 599: A Accumulator ....... ' ...........

- Page 603 and 604: PGND ..............................

- Page 605 and 606: DSP56K FAMILY INTRODUCTIONDSP56K CE

-H- fast .............................. 7-26long ............................. 7-29Hardware DO Loop ................ 6-24, A-88 Interrupt Instruction Fetch ................ 7-24Hardware Interrupt ..................... 7-11 instructions preCeding ............... 7-25Hardware Interrupt Sources .............. 7-16 Interrupt Masks ........................ 5-12IROA ....... , .................... 7-16 Interrupt Priority Levels (IPL) ......... 5-6, 7-14IROB ............................ 7-16 Interrupt Priority Register ................ 7-14NMI ............................. 7-16 Interrupt Priority Structure ......... , ...... 7-12RESET .......................... 7-16 Interrupt Processing State ................ 7-10Hardware ResetI nterrupt Sources ....................... 7-16OnCE pins and .................... 10-5 hardware ......................... 7-16Helpline ........................... 11-16 other ............................ 7-22s<strong>of</strong>tware .......................... 7-17trace ............................. 7-22Interrupt Types ........................ 7-12IIR Riter .............................. B-3 IPL .................................. 7-14ILLEGAL ............................ A-102 IROA ........ , ........ ' ........... , ... 5-6Illegal Instruction Interrupt (III) ............ 7-17 IRQB ................................. 5-6Immediate Data ..............•........ 6-14Immediate Short ....................... 6-14INC ................................ A-104Instruction Descriptions ................. A-21Instruction Encoding ................... A-311Instruction Format ................... 6-3, A-3Instruction Groups ..................... 6-20Instruction Guide ....................... A-3Instruction Pipeline .................. 5-6, 7-3restrictions . . . . . . . . . . . . . . . . . . . . . . . . . 7-8Instruction Sequence Restrictions ...... : .A-305Instruction Syntax ....................... 6-3Instruction Timing ..................... A-294Instruction Timing Summary ............. A-301Instruction Timing Symbols ............... A-9Instructionsarithmetic ......................... 6-22bit manipulation . . . . . . . . . . . . . . . . . . . . 6-24logical ........................... 6-23loop ............................. 6-24move ........................ , ... 6-26program control . . . . . . . . . . . . . . . . . . . . 6-27Interruptfast ............................. 7-12hardware ......................... 7-11long ............................. 7-12restrictions . . . . . . . . . . . . . . . . . . . . . . . . 7-1 0sources .......................... 7-11Interrupt Arbitration ..................... 7-24Interrupt Control Pins .................... 2-6Interrupt Controller ..................... 7-24Interrupt Delay Possibilities .............. 7-25Interrupt Execution ..................... 7-26Jcc ................................ A-106JCLR .............................. A-110JMP ...................... '" ...... A-116JScc .............................. A-118JSCLR ............................ ' A-122JSET ............................. , A-130JSR .................. , ....... , .... A-136JSSET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-138-1--J--L-LA .............................. 5-5, 5-17LC .............................. 5-5,5-17Level Sensitive .................... 5-6, 7-16Limit Bit ......................... 5-11 A-16Limiting (Saturation Arithmetic) .......... .' .. 3-9Linear Arithmetic ...................... .4-14Linear Modifier ........................ 4-16Lock, PLL, loss <strong>of</strong> ...................... 9-13Logic Unit ............................. 3-6Logical Instructions ..................... 6-23Long Interrupt ......................... 7-12Long Interrupt Execution ................. 7-29Long Word ............................. 6-5Loop Address (LA) Register .......... 5-5, 5-17Loop Counter (LC) Register .......... 5-5, 5-17Loop Flag Bit .......................... 5-13Loop Instructions ....................... 6-24Low Power Divider ...................... 9-3