section 7 - Index of

section 7 - Index of section 7 - Index of

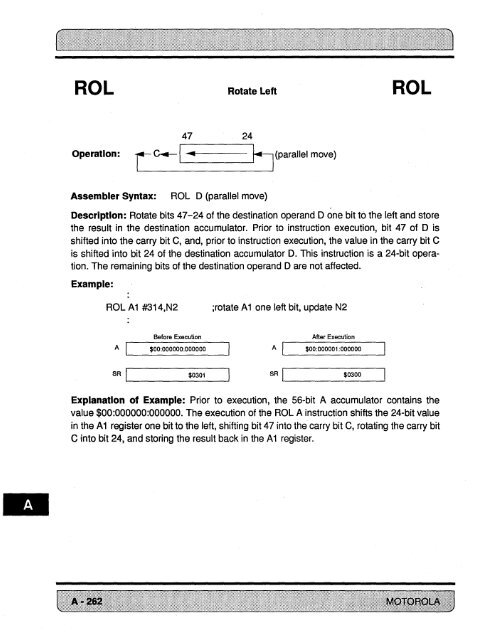

ROL Rotate Left ROLOperation:r47 24c.-I,-_ ... _____ b(parallel move)Assembler Syntax:ROL D (parallel move)Description: Rotate bits 47-24 of the destination operand D one bit to the left and storethe result in the destination accumulator. Prior to instruction execution, bit 47 of D isshifted into the carry bit C, and, prior to instruction execution, the value in the carry bit Cis shifted into bit 24 of the destination accumulator D. This instruction is a 24-bit operation.The remaining bits of the destination operand D are not affected.Example:ROL A1 #314,N2;rotate A1 one left bit, update N2Before ExecutionAfter ExecutionA 1~ ___ $_O_o:_oo_oo_oo_:o_oo_o_oo_~ A 1~ ___ $_O_O:O_O_OO_01_:0_00_OO_0 __ ~SR 1L-_________ $O_3_01 __--'SR 1~ ________ $O_30_0 __ ~Explanation of Example: Prior to execution, the 56-bit A accumulator contains thevalue $00:000000:000000. The execution of the ROL A instruction shifts the 24-bit valuein the A1 register one bit to the left, shifting bit 47 into the carry bit C, rotating the carry bitC into bit 24, and storing the result back in the A 1 register.

ROL Rotate Left ROLCondition Codes:15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 01 LF 1 DM 1 T I.. I s, I so I 11 I lois 1 L E I I U N z vCCR 1:1... MR ......S -L -N -Z -V -C -Computed according to the definition in A.5 CONDITION CODE COMPUTATIONSet if data limiting has occurred during parallel moveSet If bit 47 of A or B result Is setSet if bits 47-24 of A or B result are zeroAlways clearedSet if bit 47 of A or B was set prior to instruction executionInstruction Format:ROL DOpcode:23 8 7DATA BUS MOVE FIELD I 0 0OPTIONAL EFFECTIVE ADDRESS EXTENSION4 31 I doInstruction Fields:o dA 0BTiming: 2+mv oscillator clock cyclesMemory: 1 +mv program words

- Page 451 and 452: MOVECMove Control RegisterMOVECInst

- Page 453 and 454: MOVEC Move Control Register MOVECTi

- Page 455 and 456: MOVEM Move Program Memory MOVEMoper

- Page 457 and 458: MOVEM Move Program Memory MOVEMInst

- Page 459 and 460: MOVEMMove Program MemoryMOVEMInstru

- Page 461 and 462: MOVEP Move Peripheral Data MOVEPist

- Page 463 and 464: MOVEP Move Peripheral Data MOVEPCon

- Page 465 and 466: MOVEP Move Peripheral Data MOVEPIns

- Page 467 and 468: MOVEP Move Peripheral Data MOVEPIns

- Page 469 and 470: MPY Signed Multiply MPYExplanation

- Page 471 and 472: MPY Signed Multiply MPYInstruction

- Page 473 and 474: MPYR Signed Multiply and Round MPYR

- Page 475 and 476: MPYR Signed Multiply and Round MPYR

- Page 477 and 478: NEGNegate AccumulatorNEGInstruction

- Page 479 and 480: NOPNo OperationNOPInstruction Forma

- Page 481 and 482: NORM Normalize Accumulator Iteratio

- Page 483 and 484: NOTLogical ComplementNOTInstruction

- Page 485 and 486: ORLogical Inclusive ORORInstruction

- Page 487 and 488: ORI OR Immediate with Control Regis

- Page 489 and 490: REP Repeat Next Instruction REPRest

- Page 491 and 492: REPRepeat Next InstructionREPInstru

- Page 493 and 494: REPRepeat Next InstructionREPInstru

- Page 495 and 496: REP Repeat Next Instruction REPNote

- Page 497 and 498: RESETReset On-Chip Peripheral Devic

- Page 499 and 500: RND Round Accumulator RNDConvergent

- Page 501: RNDRound AccumulatorRNDInstruction

- Page 505 and 506: ROR Rotate Right RORCondition Codes

- Page 507 and 508: RTIReturn from InterruptRTIConditio

- Page 509 and 510: RTSReturn from SubroutineRTSInstruc

- Page 511 and 512: sec Subtract Long with Carry secExp

- Page 513 and 514: secSubtract Long with CarrysecInstr

- Page 515 and 516: STOPStop Instruction ProcessingSTOP

- Page 517 and 518: SUB Subtract SUBCondition Codes:S -

- Page 519 and 520: SUBL Shift Left and Subtract Accumu

- Page 521 and 522: SUBR Shift Right and Subtract Accum

- Page 523 and 524: SWISoftware InterruptSWICondition C

- Page 525 and 526: Tee Transfer Conditionally Teetion

- Page 527 and 528: Tee Transfer Conditionally TeeInstr

- Page 529 and 530: TFR Transfer Data ALU Register TFRC

- Page 531 and 532: TSTTest AccumulatorTSTInstruction F

- Page 533 and 534: WAIT Wait for Interrupt WAITConditi

- Page 535 and 536: including the number of words per i

- Page 537 and 538: 5. Compute final results.Thus, base

- Page 539 and 540: JLC (R2+N2)will requireand will exe

- Page 541 and 542: Table A-6 Instruction Timing Summar

- Page 543 and 544: Note that the "ap" term in Table A-

- Page 545 and 546: Table A-14 Memory Access Timing Sum

- Page 547 and 548: Other RestrictionsDO SSH,xxxxJSR to

- Page 549 and 550: Immediately before MOVEC from SSH o

- Page 551 and 552: A.9.S REP RestrictionsThe REP instr

ROL Rotate Left ROLOperation:r47 24c.-I,-_ ... _____ b(parallel move)Assembler Syntax:ROL D (parallel move)Description: Rotate bits 47-24 <strong>of</strong> the destination operand D one bit to the left and storethe result in the destination accumulator. Prior to instruction execution, bit 47 <strong>of</strong> D isshifted into the carry bit C, and, prior to instruction execution, the value in the carry bit Cis shifted into bit 24 <strong>of</strong> the destination accumulator D. This instruction is a 24-bit operation.The remaining bits <strong>of</strong> the destination operand D are not affected.Example:ROL A1 #314,N2;rotate A1 one left bit, update N2Before ExecutionAfter ExecutionA 1~ ___ $_O_o:_oo_oo_oo_:o_oo_o_oo_~ A 1~ ___ $_O_O:O_O_OO_01_:0_00_OO_0 __ ~SR 1L-_________ $O_3_01 __--'SR 1~ ________ $O_30_0 __ ~Explanation <strong>of</strong> Example: Prior to execution, the 56-bit A accumulator contains thevalue $00:000000:000000. The execution <strong>of</strong> the ROL A instruction shifts the 24-bit valuein the A1 register one bit to the left, shifting bit 47 into the carry bit C, rotating the carry bitC into bit 24, and storing the result back in the A 1 register.