section 7 - Index of

section 7 - Index of section 7 - Index of

NEG Negate Accumulator NEGOperation:Assembler Syntax:0-0 ~ 0 (parallel move) NEG D (parallel move)Description: Negate the destination operand D and store the result in the destinationaccumulator. This is a 56-bit, twos-complement operation.Example:NEG B X1 ,X:(R3)+ Y:(R6)-,A;O-B ~ B, update A,X1 ,R3,R6Before ExecutionBI~ __ $_0_0:_12_34_56_:7_89_A_BC __ ~BI~ __After Execution$F_F_:E_DC_B_A9_:8_76_54_4 __ ~Explanation of Example: Prior to execution, the 56-bit B accumulator contains thevalue $00:123456:789ABC. The NEG B instruction takes the twos complement of thevalue in the B accumulator and stores the 56-bit result back in the B accumulator.Condition Codes:15 14 13 12 11 10 9 8 7 6 5 4 3 2 0I LF I DM I T I *. I 81 I 80 I 11 I 10 I s I LIE I u I N I z v I c IS -L -E -U -N -Z -V -.... MR •. ~ CCR •.Computed according to the definition in A.5 CONDITION CODE COMPUTATIONSet if limiting (parallel move) or overflow has occurred in resultSet if the signed integer portion of A or B result is in useSet if A or B result is unnormalizedSet if bit 55 of A or B result is setSet if A or B result equals zeroSet if overflow has occurred in A or B resultNote: The definitions of the E and U bits vary according to the scaling mode being used.Refer to Section A.5 CONDITION CODE COMPUTATION for complete details.

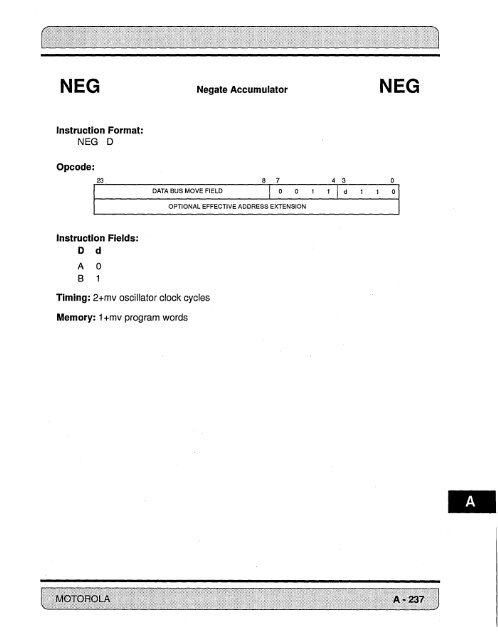

NEGNegate AccumulatorNEGInstruction Format:NEG 0Opcode:238 7DATA BUS MOVE FIELD I 0 0OPTIONAL EFFECTIVE ADDRESS EXTENSION4 3 o1 I d oInstruction Fields:o dA 0BTiming: 2+mv oscillator clock cyclesMemory: 1 +mv program words

- Page 425 and 426: X:R X Memory and Register Data Move

- Page 427 and 428: Y: Y Memory Data Move Y:Note: This

- Page 429 and 430: Y: Y Memory Data Move Y:S D DS,D d

- Page 431 and 432: Y: Y Memory Data Move Y:S D DS,D d

- Page 433 and 434: R:V Register and V Memory Data Move

- Page 435 and 436: R:V Register and Y Memory Data Move

- Page 437 and 438: R:V Register and Y Memory Data Move

- Page 439 and 440: L: Long Memory Data Move L:Example:

- Page 441 and 442: L: Long Memory Data Move L:Instruct

- Page 443 and 444: X: Y: xv Memory Data Move X: Y:Exam

- Page 445 and 446: X: Y: xv Memory Data Move X: Y:S1 D

- Page 447 and 448: MOVEC Move Control Register MOVECst

- Page 449 and 450: MOVEC Move Control Register MOVECCo

- Page 451 and 452: MOVECMove Control RegisterMOVECInst

- Page 453 and 454: MOVEC Move Control Register MOVECTi

- Page 455 and 456: MOVEM Move Program Memory MOVEMoper

- Page 457 and 458: MOVEM Move Program Memory MOVEMInst

- Page 459 and 460: MOVEMMove Program MemoryMOVEMInstru

- Page 461 and 462: MOVEP Move Peripheral Data MOVEPist

- Page 463 and 464: MOVEP Move Peripheral Data MOVEPCon

- Page 465 and 466: MOVEP Move Peripheral Data MOVEPIns

- Page 467 and 468: MOVEP Move Peripheral Data MOVEPIns

- Page 469 and 470: MPY Signed Multiply MPYExplanation

- Page 471 and 472: MPY Signed Multiply MPYInstruction

- Page 473 and 474: MPYR Signed Multiply and Round MPYR

- Page 475: MPYR Signed Multiply and Round MPYR

- Page 479 and 480: NOPNo OperationNOPInstruction Forma

- Page 481 and 482: NORM Normalize Accumulator Iteratio

- Page 483 and 484: NOTLogical ComplementNOTInstruction

- Page 485 and 486: ORLogical Inclusive ORORInstruction

- Page 487 and 488: ORI OR Immediate with Control Regis

- Page 489 and 490: REP Repeat Next Instruction REPRest

- Page 491 and 492: REPRepeat Next InstructionREPInstru

- Page 493 and 494: REPRepeat Next InstructionREPInstru

- Page 495 and 496: REP Repeat Next Instruction REPNote

- Page 497 and 498: RESETReset On-Chip Peripheral Devic

- Page 499 and 500: RND Round Accumulator RNDConvergent

- Page 501 and 502: RNDRound AccumulatorRNDInstruction

- Page 503 and 504: ROL Rotate Left ROLCondition Codes:

- Page 505 and 506: ROR Rotate Right RORCondition Codes

- Page 507 and 508: RTIReturn from InterruptRTIConditio

- Page 509 and 510: RTSReturn from SubroutineRTSInstruc

- Page 511 and 512: sec Subtract Long with Carry secExp

- Page 513 and 514: secSubtract Long with CarrysecInstr

- Page 515 and 516: STOPStop Instruction ProcessingSTOP

- Page 517 and 518: SUB Subtract SUBCondition Codes:S -

- Page 519 and 520: SUBL Shift Left and Subtract Accumu

- Page 521 and 522: SUBR Shift Right and Subtract Accum

- Page 523 and 524: SWISoftware InterruptSWICondition C

- Page 525 and 526: Tee Transfer Conditionally Teetion

NEGNegate AccumulatorNEGInstruction Format:NEG 0Opcode:238 7DATA BUS MOVE FIELD I 0 0OPTIONAL EFFECTIVE ADDRESS EXTENSION4 3 o1 I d oInstruction Fields:o dA 0BTiming: 2+mv oscillator clock cyclesMemory: 1 +mv program words