section 7 - Index of

section 7 - Index of section 7 - Index of

MACR Signed Multiply-Accumulate and Round MACRInstruction Fields 1:S1*S2 Q Q Q Sign k D dXOXO 0 0 0 + 0 A 0YO YO 0 0 1 1 8 1X1 XO 0 1 0Y1 YO 0 1 1XOY1 1 0 0YOXO 1 0 1X1 YO 1 1 0Y1 X1 1 1 1Note: Only the indicated 81 *82 combinations are valid. X1 *X1 and Y1 *Y1 are not valid.Timing: 2+mv oscillator clock cyclesMemory: 1 +mv program wordsExample 2:MACR -YO, #10,8Before ExecutionAfter ExecutionYO~I _________ $_65_4_32_1 __ ~ YO~I _________ $_6_M_32_1 __ ~BI~ ____ $_OO_:1_00_00_o_:oo_o_oo_o __ ~B~I ____ $O_O_:OF_E_6A_F_:O_OO_oo_o __ ~Explanation of Example 2: The content of YO ($654321) is negated, multiplied by 2- 1 °,added to the content of the 8 accumulator ($00:100000:000000), placed in the 8 accumulatorand then rounded to a single precision number (24 bits in 81). The net effect ofthis operation is to negate the content of YO, divide the result by 2 10 and add the resultto the accumulator. An alternate interpretation is that YO is negated, right shifted 10places, filled with the sign bit (0 for a positive number and 1 for a negative number), theresult is added to the accumulator and then rounded to a single precision number.

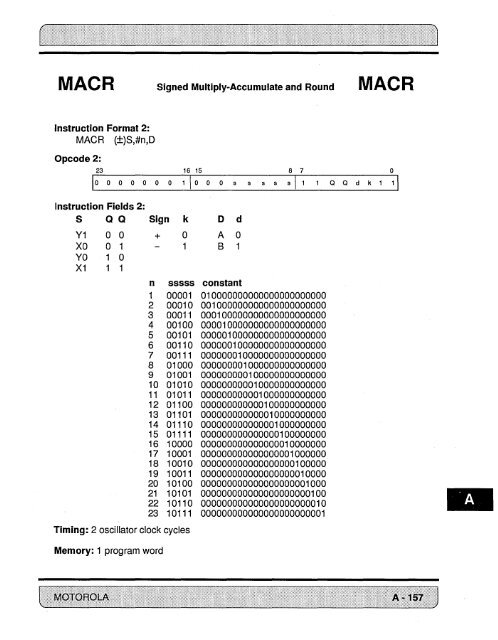

MACR Signed MUltiply-Accumulate and Round MACRInstruction Format 2:MACR (±)S,#n,DOpcode 2:23 16 15 8 7 o\0 0 0 0 0 0 0 1\000 S S ss S\1 1 Q Q d k 1 11Instruction Fields 2:S QQ Sign k D dY1 0 0 + 0 A 0XO 0 1 1 B 1YO 1 0X1 1 1n sssss constant1 00001 0100000000000000000000002 00010 0010000000000000000000003 00011 0001000000000000000000004 00100 0000100000000000000000005 00101 0000010000000000000000006 00110 0000001000000000000000007 00111 0000000100000000000000008 01000 0000000010000000000000009 01001 00000000010000000000000010 01010 00000000001000000000000011 01011 00000000000100000000000012 01100 00000000000010000000000013 01101 00000000000001000000000014 01110 00000000000000100000000015 01111 00000000000000010000000016 10000 00000000000000001000000017 10001 00000000000000000100000018 10010 00000000000000000010000019 10011 000000000000000000010000-20 10100 00000000000000000000100021 10101 00000000000000000000010022 10110 00000000000000000000001023 10111 000000000000000000000001Timing: 2 oscillator clock cyclesMemory: 1 program word

- Page 345 and 346: INC Increment by One INCInstruction

- Page 347 and 348: Jcc Jump Conditionally JccRestricti

- Page 349 and 350: JccJump ConditionallyJccEffectiveAd

- Page 351 and 352: JCLR Jump If Bit Clear JCLRRestrict

- Page 353 and 354: JCLRJump If Bit ClearJCLRInstructio

- Page 355 and 356: JCLR Jump If Bit Clear JCLRInstruct

- Page 357 and 358: JMPJumpJMPInstruction Fields:xxx=12

- Page 359 and 360: JSccJump to Subroutine Conditionall

- Page 361 and 362: JScc Jump to Subroutine Conditional

- Page 363 and 364: JSCLR Jump to Subroutine if Bit Cle

- Page 365 and 366: JSCLRJump to Subroutine If Bit Clea

- Page 367 and 368: JSCLRJump to Subroutine If Bit Clea

- Page 369 and 370: JSCLR Jump to Subroutine If Bit Cle

- Page 371 and 372: JSET Jump if Bit Set JSETRestrictio

- Page 373 and 374: JSETJump if Bit SetJSETInstruction

- Page 375 and 376: JSET Jump If Bit Set JSETInstructio

- Page 377 and 378: JSR Jump to Subroutine JSRInstructi

- Page 379 and 380: JSSET Jump to Subroutine if Bit Set

- Page 381 and 382: JSSETJump to Subroutine if Bit SetJ

- Page 383 and 384: JSSET Jump to Subroutine if Bit Set

- Page 385 and 386: LSL Logical Shift Left LSLCondition

- Page 387 and 388: LSR Logical Shift Right LSRConditio

- Page 389 and 390: LUALoad Updated AddressLUACondition

- Page 391 and 392: MAC Signed Multiply-Accumulate MACC

- Page 393 and 394: MACSigned Multiply-AccumulateMACTim

- Page 395: MACR Signed Multiply-Accumulate and

- Page 399 and 400: MOVE Move Data MOVEExplanation of E

- Page 401 and 402: MOVE Move Data MOVEWhen a 56-bit ac

- Page 403 and 404: No Parallel Data MoveInstruction Fo

- Page 405 and 406: I Immediate Short Data Move IExampl

- Page 407 and 408: I Immediate Short Data Move IDDD d

- Page 409 and 410: R Register to Register Data Move RE

- Page 411 and 412: R Register to Register Data Move RI

- Page 413 and 414: uAddress Register UpdateuInstructio

- Page 415 and 416: X: X Memory Data Move X:Note:Due to

- Page 417 and 418: X: X Memory Data Move X:S D DS,D d

- Page 419 and 420: X: X Memory Data Move X:S D DS,D d

- Page 421 and 422: X:R X Memory and Register Data Move

- Page 423 and 424: X:R X Memory and Register Data Move

- Page 425 and 426: X:R X Memory and Register Data Move

- Page 427 and 428: Y: Y Memory Data Move Y:Note: This

- Page 429 and 430: Y: Y Memory Data Move Y:S D DS,D d

- Page 431 and 432: Y: Y Memory Data Move Y:S D DS,D d

- Page 433 and 434: R:V Register and V Memory Data Move

- Page 435 and 436: R:V Register and Y Memory Data Move

- Page 437 and 438: R:V Register and Y Memory Data Move

- Page 439 and 440: L: Long Memory Data Move L:Example:

- Page 441 and 442: L: Long Memory Data Move L:Instruct

- Page 443 and 444: X: Y: xv Memory Data Move X: Y:Exam

- Page 445 and 446: X: Y: xv Memory Data Move X: Y:S1 D

MACR Signed MUltiply-Accumulate and Round MACRInstruction Format 2:MACR (±)S,#n,DOpcode 2:23 16 15 8 7 o\0 0 0 0 0 0 0 1\000 S S ss S\1 1 Q Q d k 1 11Instruction Fields 2:S QQ Sign k D dY1 0 0 + 0 A 0XO 0 1 1 B 1YO 1 0X1 1 1n sssss constant1 00001 0100000000000000000000002 00010 0010000000000000000000003 00011 0001000000000000000000004 00100 0000100000000000000000005 00101 0000010000000000000000006 00110 0000001000000000000000007 00111 0000000100000000000000008 01000 0000000010000000000000009 01001 00000000010000000000000010 01010 00000000001000000000000011 01011 00000000000100000000000012 01100 00000000000010000000000013 01101 00000000000001000000000014 01110 00000000000000100000000015 01111 00000000000000010000000016 10000 00000000000000001000000017 10001 00000000000000000100000018 10010 00000000000000000010000019 10011 000000000000000000010000-20 10100 00000000000000000000100021 10101 00000000000000000000010022 10110 00000000000000000000001023 10111 000000000000000000000001Timing: 2 oscillator clock cyclesMemory: 1 program word