section 7 - Index of

section 7 - Index of section 7 - Index of

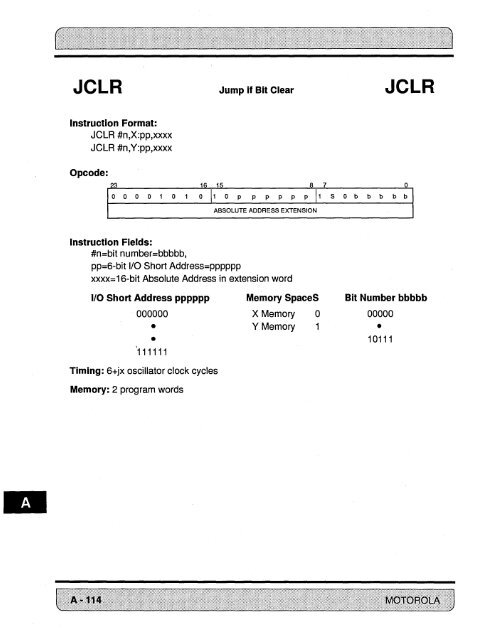

JCLRJump if Bit ClearJCLRInstruction Format:JCLR #n,X:pp,xxxxJCLR #n,Y:pp,xxxxOpcode:23 16 15 8 7 00000101 o 11 0 p p p p p p 11 SOb b b b bABSOLUTE ADDRESS EXTENSIONInstruction Fields:#n=bit number=bbbbb,pp=6-bit I/O Short Address=ppppppxxxx=16-bit Absolute Address in extension wordI/O Short Address pppppp000000••'111111Timing: 6+jx oscillator clock cyclesMemory: 2 program wordsMemory SpaceSX MemoryY MemoryaBit Number bbbbb00000•10111-

JCLR Jump If Bit Clear JCLRInstruction Format:JCLR #n,S,xxxxOpcode:23 16 15 87000001010111 D DDDDDIOOObbbbbABSOLUTE ADDRESS EXTENSIONInstruction Fields:#n=bit number=bbbbb,S=source register=DDDDDDxxxx=16-bit Absolute Address in extension wordSource Register4 registers in Data ALU8 accumulators in Data ALU8 address registers in AGU8 address offset registers in AGU8 address modifier registers in AGU8 program controller registersDDDDDDo 0 0 1 D Do 0 1 D D D010 TT To 1 1 N N N1 0 0 F F F1 1 1 G G GBit Number bbbbb00000•10111See Section A.1 0 and Table A-18 for specific register encodings.Notes: If A or B is specified as the destination operand, the following sequence of eventstakes place:1. The S bit is computed according to its definition (See Section A.5)2. The accumulator value is scaled according to the scaling mode bits SOand S1 in the status register (SR).3. If the accumulator extension is in use, the output of the shifter is limited tothe maximum positive or negative saturation constant, and the L bit is set.-4. The bit test is performed on the resulting 24-bit value, and the jump is takenif the bit tested is clear. The original contents of A or B are not changed.Timing: 6+jx oscillator clock cyclesMemory: 2 program words

- Page 303 and 304: BSET Bit Test and Set BSETNotes: If

- Page 305 and 306: BTSTBit TestBTSTCondition Codes:115

- Page 307 and 308: 8TSTBit Test8TSTInstruction Format:

- Page 309 and 310: 8TSTBit Test8TSTInstruction Format:

- Page 311 and 312: CLRClear AccumulatorCLRInstruction

- Page 313 and 314: CMP Compare CMPCondition Codes:15 1

- Page 315 and 316: CMPM Compare Magnitude CMPMConditio

- Page 317 and 318: DEBUGEnter Debug ModeDEBUGOpcode:23

- Page 319 and 320: DEBUGcc Enter Debug Mode Conditiona

- Page 321 and 322: DEC Decrement by One DECInstruction

- Page 323 and 324: DIV Divide Interation DIVThe DIV in

- Page 325 and 326: DIV Divide Interation DIVNote that

- Page 327 and 328: DIVInstruction Format:DIV S,DDivide

- Page 329 and 330: DO Start Hardware Loop DOexecuted 6

- Page 331 and 332: DOStart Hardware LoopDOAt LAOther R

- Page 333 and 334: DOStart Hardware LoopDOInstruction

- Page 335 and 336: DOStart Hardware LoopDOInstruction

- Page 337 and 338: DO Start Hardware Loop DONotes: If

- Page 339 and 340: ENDDO End Current DO Loop ENDDOExpl

- Page 341 and 342: EOR Logical Exclusive OR EORInstruc

- Page 343 and 344: ILLEGALIllegal Instruction Interrup

- Page 345 and 346: INC Increment by One INCInstruction

- Page 347 and 348: Jcc Jump Conditionally JccRestricti

- Page 349 and 350: JccJump ConditionallyJccEffectiveAd

- Page 351 and 352: JCLR Jump If Bit Clear JCLRRestrict

- Page 353: JCLRJump If Bit ClearJCLRInstructio

- Page 357 and 358: JMPJumpJMPInstruction Fields:xxx=12

- Page 359 and 360: JSccJump to Subroutine Conditionall

- Page 361 and 362: JScc Jump to Subroutine Conditional

- Page 363 and 364: JSCLR Jump to Subroutine if Bit Cle

- Page 365 and 366: JSCLRJump to Subroutine If Bit Clea

- Page 367 and 368: JSCLRJump to Subroutine If Bit Clea

- Page 369 and 370: JSCLR Jump to Subroutine If Bit Cle

- Page 371 and 372: JSET Jump if Bit Set JSETRestrictio

- Page 373 and 374: JSETJump if Bit SetJSETInstruction

- Page 375 and 376: JSET Jump If Bit Set JSETInstructio

- Page 377 and 378: JSR Jump to Subroutine JSRInstructi

- Page 379 and 380: JSSET Jump to Subroutine if Bit Set

- Page 381 and 382: JSSETJump to Subroutine if Bit SetJ

- Page 383 and 384: JSSET Jump to Subroutine if Bit Set

- Page 385 and 386: LSL Logical Shift Left LSLCondition

- Page 387 and 388: LSR Logical Shift Right LSRConditio

- Page 389 and 390: LUALoad Updated AddressLUACondition

- Page 391 and 392: MAC Signed Multiply-Accumulate MACC

- Page 393 and 394: MACSigned Multiply-AccumulateMACTim

- Page 395 and 396: MACR Signed Multiply-Accumulate and

- Page 397 and 398: MACR Signed MUltiply-Accumulate and

- Page 399 and 400: MOVE Move Data MOVEExplanation of E

- Page 401 and 402: MOVE Move Data MOVEWhen a 56-bit ac

- Page 403 and 404: No Parallel Data MoveInstruction Fo

JCLRJump if Bit ClearJCLRInstruction Format:JCLR #n,X:pp,xxxxJCLR #n,Y:pp,xxxxOpcode:23 16 15 8 7 00000101 o 11 0 p p p p p p 11 SOb b b b bABSOLUTE ADDRESS EXTENSIONInstruction Fields:#n=bit number=bbbbb,pp=6-bit I/O Short Address=ppppppxxxx=16-bit Absolute Address in extension wordI/O Short Address pppppp000000••'111111Timing: 6+jx oscillator clock cyclesMemory: 2 program wordsMemory SpaceSX MemoryY MemoryaBit Number bbbbb00000•10111-