Current-mode PWM controller

Current-mode PWM controller

Current-mode PWM controller

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Philips Semiconductors Linear Products<br />

<strong>Current</strong>-<strong>mode</strong> <strong>PWM</strong> <strong>controller</strong><br />

Product specification<br />

UC3842<br />

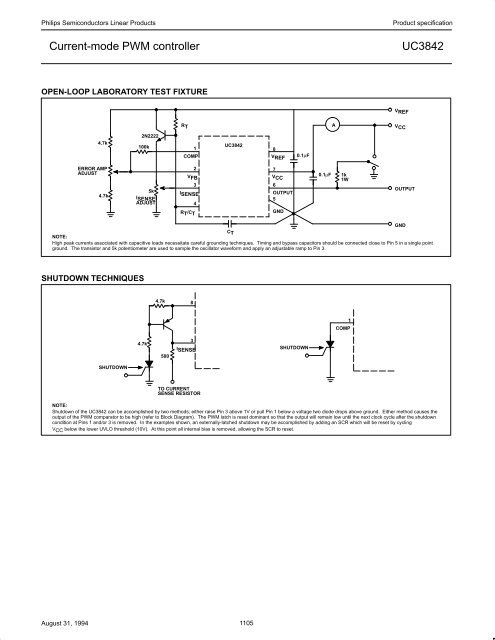

OPEN-LOOP LABORATORY TEST FIXTURE<br />

V REF<br />

R T<br />

A<br />

V CC<br />

4.7k<br />

2N2222<br />

100k<br />

1<br />

COMP<br />

UC3842<br />

8<br />

V REF<br />

0.1µF<br />

ERROR AMP<br />

ADJUST<br />

4.7k<br />

5k<br />

I SENSE<br />

ADJUST<br />

2<br />

V FB<br />

3<br />

I SENSE<br />

4<br />

R T /C T<br />

7<br />

V CC<br />

6<br />

OUTPUT<br />

5<br />

GND<br />

0.1µF<br />

1k<br />

1W<br />

OUTPUT<br />

C T<br />

NOTE:<br />

High peak currents associated with capacitive loads necessitate careful grounding techniques. Timing and bypass capacitors should be connected close to Pin 5 in a single point<br />

ground. The transistor and 5k potentiometer are used to sample the oscillator waveform and apply an adjustable ramp to Pin 3.<br />

GND<br />

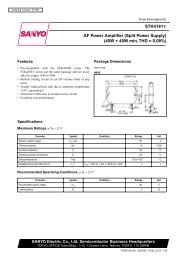

SHUTDOWN TECHNIQUES<br />

4.7k 8<br />

1<br />

COMP<br />

3<br />

4.7k<br />

I SENSE<br />

SHUTDOWN<br />

500<br />

SHUTDOWN<br />

TO CURRENT<br />

SENSE RESISTOR<br />

NOTE:<br />

Shutdown of the UC3842 can be accomplished by two methods; either raise Pin 3 above 1V or pull Pin 1 below a voltage two diode drops above ground. Either method causes the<br />

output of the <strong>PWM</strong> comparator to be high (refer to Block Diagram). The <strong>PWM</strong> latch is reset dominant so that the output will remain low until the next clock cycle after the shutdown<br />

condition at Pins 1 and/or 3 is removed. In the examples shown, an externally-latched shutdown may be accomplished by adding an SCR which will be reset by cycling<br />

V CC below the lower UVLO threshold (10V). At this point all internal bias is removed, allowing the SCR to reset.<br />

August 31, 1994 1105