contents - iirw.org Home

contents - iirw.org Home contents - iirw.org Home

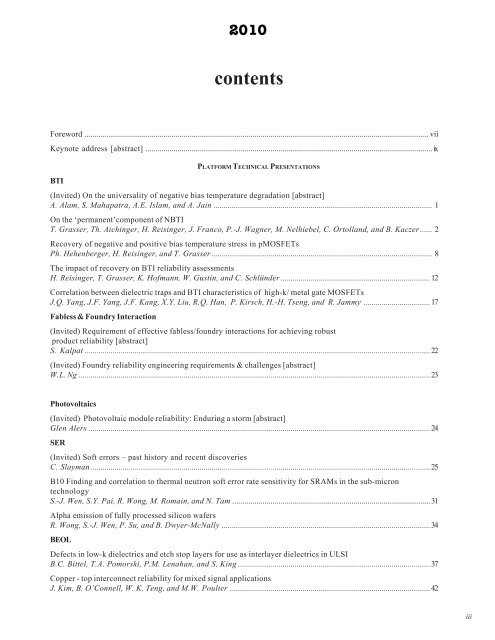

2010 contents Foreword .......................................................................................................................................................................... vii Keynote address [abstract] .............................................................................................................................................. ix PLATFORM TECHNICAL PRESENTATIONS BTI (Invited) On the universality of negative bias temperature degradation [abstract] A. Alam, S. Mahapatra, A.E. Islam, and A. Jain ............................................................................................................ 1 On the ‘permanent’component of NBTI T. Grasser, Th. Aichinger, H. Reisinger, J. Franco, P.-J. Wagner, M. Nelhiebel, C. Ortolland, and B. Kaczer ...... 2 Recovery of negative and positive bias temperature stress in pMOSFETs Ph. Hehenberger, H. Reisinger, and T. Grasser ............................................................................................................. 8 The impact of recovery on BTI reliability assessments H. Reisinger, T. Grasser, K. Hofmann, W. Gustin, and C. Schlünder..........................................................................12 Correlation between dielectric traps and BTI characteristics of high-k/ metal gate MOSFETs J.Q. Yang, J.F. Yang, J.F. Kang, X.Y. Liu, R.Q. Han, P. Kirsch, H.-H. Tseng, and R. Jammy .................................17 Fabless & Foundry Interaction (Invited) Requirement of effective fabless/foundry interactions for achieving robust product reliability [abstract] S. Kalpat ...........................................................................................................................................................................22 (Invited) Foundry reliability engineering requirements & challenges [abstract] W.L. Ng ..............................................................................................................................................................................23 Photovoltaics (Invited) Photovoltaic module reliability: Enduring a storm [abstract] Glen Alers .........................................................................................................................................................................24 SER (Invited) Soft errors – past history and recent discoveries C. Slayman ........................................................................................................................................................................25 B10 Finding and correlation to thermal neutron soft error rate sensitivity for SRAMs in the sub-micron technology S.-J. Wen, S.Y. Pai, R. Wong, M. Romain, and N. Tam ..................................................................................................31 Alpha emission of fully processed silicon wafers R. Wong, S.-J. Wen, P. Su, and B. Dwyer-McNally .......................................................................................................34 BEOL Defects in low-k dielectrics and etch stop layers for use as interlayer dielectrics in ULSI B.C. Bittel, T.A. Pomorski, P.M. Lenahan, and S. King ...............................................................................................37 Copper - top interconnect reliability for mixed signal applications J. Kim, B. O’Connell, W. K. Teng, and M.W. Poulter ...................................................................................................42 iii

- Page 2 and 3: iv 2010 Effect of reservoir on elec

- Page 4 and 5: vi 2010 Hot carriers Alain Bravaix

- Page 6 and 7: 2009 iv 2009 Transistor Application

- Page 8 and 9: DISCUSSION GROUP (DG) SUMMARIES DG:

- Page 10 and 11: iv 2008 2008 NBTI-2 Geometry effect

- Page 12 and 13: 2007 2007 contents Foreword .......

- Page 14 and 15: TUTORIAL ABSTRACTS Detection of ato

- Page 16 and 17: iv 2006 2006 Study of electrically

- Page 18 and 19: 2005 contents Foreword ............

- Page 20 and 21: 2005 2005 Designing radiation harde

- Page 22 and 23: iv 2005 Detection of trap generatio

- Page 24 and 25: 2004 2004 contents Foreword .......

- Page 26 and 27: 2004 2004 Reliability issues in adv

- Page 28 and 29: 2003 2003 Dielectric reliability st

- Page 30 and 31: 2002 2002 contents Foreword .......

- Page 32 and 33: 2002 2002 Comparison of calculated

- Page 34 and 35: iv 2001 2001 POSTER PRESENTATIONS O

- Page 36 and 37: �� 2000 2000 ������

- Page 38 and 39: 1999 1999 contents Foreword .......

- Page 40 and 41: contents 1998 1998 Foreword .......

- Page 42 and 43: 1997 1997 1997

- Page 44 and 45: 1997 1997 1997

- Page 46 and 47: 1996 1996 1996

- Page 48 and 49: 1995 1995 1995

- Page 50 and 51: 1994 1994 1994

2010<br />

<strong>contents</strong><br />

Foreword .......................................................................................................................................................................... vii<br />

Keynote address [abstract] .............................................................................................................................................. ix<br />

PLATFORM TECHNICAL PRESENTATIONS<br />

BTI<br />

(Invited) On the universality of negative bias temperature degradation [abstract]<br />

A. Alam, S. Mahapatra, A.E. Islam, and A. Jain ............................................................................................................ 1<br />

On the ‘permanent’component of NBTI<br />

T. Grasser, Th. Aichinger, H. Reisinger, J. Franco, P.-J. Wagner, M. Nelhiebel, C. Ortolland, and B. Kaczer ...... 2<br />

Recovery of negative and positive bias temperature stress in pMOSFETs<br />

Ph. Hehenberger, H. Reisinger, and T. Grasser ............................................................................................................. 8<br />

The impact of recovery on BTI reliability assessments<br />

H. Reisinger, T. Grasser, K. Hofmann, W. Gustin, and C. Schlünder..........................................................................12<br />

Correlation between dielectric traps and BTI characteristics of high-k/ metal gate MOSFETs<br />

J.Q. Yang, J.F. Yang, J.F. Kang, X.Y. Liu, R.Q. Han, P. Kirsch, H.-H. Tseng, and R. Jammy .................................17<br />

Fabless & Foundry Interaction<br />

(Invited) Requirement of effective fabless/foundry interactions for achieving robust<br />

product reliability [abstract]<br />

S. Kalpat ...........................................................................................................................................................................22<br />

(Invited) Foundry reliability engineering requirements & challenges [abstract]<br />

W.L. Ng ..............................................................................................................................................................................23<br />

Photovoltaics<br />

(Invited) Photovoltaic module reliability: Enduring a storm [abstract]<br />

Glen Alers .........................................................................................................................................................................24<br />

SER<br />

(Invited) Soft errors – past history and recent discoveries<br />

C. Slayman ........................................................................................................................................................................25<br />

B10 Finding and correlation to thermal neutron soft error rate sensitivity for SRAMs in the sub-micron<br />

technology<br />

S.-J. Wen, S.Y. Pai, R. Wong, M. Romain, and N. Tam ..................................................................................................31<br />

Alpha emission of fully processed silicon wafers<br />

R. Wong, S.-J. Wen, P. Su, and B. Dwyer-McNally .......................................................................................................34<br />

BEOL<br />

Defects in low-k dielectrics and etch stop layers for use as interlayer dielectrics in ULSI<br />

B.C. Bittel, T.A. Pomorski, P.M. Lenahan, and S. King ...............................................................................................37<br />

Copper - top interconnect reliability for mixed signal applications<br />

J. Kim, B. O’Connell, W. K. Teng, and M.W. Poulter ...................................................................................................42<br />

iii

iv<br />

2010<br />

Effect of reservoir on electromigration of short interconnects<br />

P. Lamontagne, D. Ney, and Y. Wouters ........................................................................................................................46<br />

Investigation into the effect of a "Through silicon via" process on the MOS transistor reliability of<br />

a standard 0.13�m CMOS technology<br />

A. Martin, L. Borucki, H. Reisinger, and C. Schlunder ...............................................................................................51<br />

Transistor<br />

Impact of body tie and Source/Drain contact spacing on the hot carrier reliability of 45nm RF-CMOS<br />

R. Arora, K. A. Moen, A. Madan, J.D. Cressler, E. Zhang, D.M. Fleetwood, R.D. Schrimpf,<br />

A.K. Sutton, and H.M. Nayfeh .........................................................................................................................................56<br />

Multiple microscopic defects characterization methods to improve macroscopic degradation<br />

modeling of MOSFETs<br />

Y.M. Randriamihaja, A. Bravaix, V. Huard, D. Rideau, M. Rafik, and D. Roy ..........................................................61<br />

MOS transistor characteristics and its dependence of plasma charging degradation on the test<br />

structure layout of a 0.13�m CMOS technology<br />

A. Martin, R.-P. Vollertsen, and H. Reisinger..............................................................................................................67<br />

Hot carrier impact on the small signal equivalent circuit<br />

L. Negre, D. Roy, S. Boret, P. Scheer, N. Kauffmann, D. Gloria, and G. Ghibaudo .......................................................................................72<br />

Reliability<br />

‘Atomistic’ simulation of RTS amplitudes due to single and multiple charged defect states and<br />

their interactions<br />

M. F. Bukhori, T. Grasser, B. Kaczer, H. Reisinger, and A. Asenov ...........................................................................76<br />

Stability and bias stressing of metal/insulator/metal diodes<br />

N. Alimardani, J.F. Conley, Jr., E. W. Cowell III, J.F. Wager, M. Chin., S. Kilpatrick., and M. Dubey ................80<br />

Product Reliability<br />

(Invited) Qualifying reliable systems from unreliable components [abstract]<br />

Amr Haggag .....................................................................................................................................................................85<br />

Memory<br />

Single bit read disturb failure mechanism and transistor size optimization for dual port SRAM<br />

bitcell in embedded NVM process SOC applications<br />

S.-R. Kim,K.J. Han, K.-S. Lee, T.-H. Kim, J. Wolfman, Y. Wang, B. Schmit, K. Hauch, H. Kim,<br />

P.-Y. Lee, E. Minh, Y. Jia, F. Dhaoui, P. Liu, and H.-C. Tseng ....................................................................................86<br />

Characterization of anomalous erase effects in 48 nm TANOS charge trapping memory cells<br />

D.-A. Loehr, R. Hoffmann, A. Naumann, J. Paul, K. Seidel, M. Czernohorsky, and V. Beyer ..................................89<br />

Cycling induced degradation of a 65nm FPGA flash memory switch<br />

B.A. Schmid, J.Y. Jia, J. Wolfman, Y. Wang, F. Dhaoui, H.-C. Tseng, S.-R. Kim, K.-S. Lee, P. Liu,<br />

K.J. Han, and C. Hu .........................................................................................................................................................92<br />

Impact of the storage layer charging on random telegraph noise behavior of sub-50nm<br />

charge-trap-based TANOS and floating-gate memory cells<br />

K. Seidel, R. Hoffmann, A. Naumann, J. Paul, D.A. Löhr, M. Czernohorsky, and V. Beyer ......................................95<br />

POSTER PRESENTATIONS—REFEREED<br />

Evaluation of x-ray irradiation defect on 65nm multi-level cell NOR flash technologies<br />

P. Navuduri, W. Melton, A. Oen, S. Eilert, C. Abraham, and S.-J. Wen ......................................................................98<br />

A novel virtual age reliability model for time-to-failure prediction<br />

Y. Wang and S.D. Cotofana.......................................................................................................................................... 102

2010<br />

Downstream electromigration improvement in 45nm technology<br />

Y. Zhao, X. Zeng, W. Liu, F. Zhang, and Y.K. Lim ...................................................................................................... 106<br />

Evaluation on the reliable operation of a gate-level pipelined self synchronous system against PVT<br />

and aging<br />

B. Devlin, M. Ikeda, and K. Asada .............................................................................................................................. 110<br />

Memory reliability model for accumulated and clustered soft errors<br />

S.Y. Lee, S. Baeg, and P. Reviriego ............................................................................................................................. 114<br />

An empirical model describing the MLC retention of charge trap flash memories<br />

T. Melde, R. Hoffmann, E. Yurchuk, J. Paul, and T. Mikolajick .............................................................................. 118<br />

TDDB chip reliability in copper interconnects<br />

M. Bashir, D.H. Kim, S.K. Lim, and L. Milor .............................................................................................................. 121<br />

Degradation of sub-micron gate AlGaN/GaN HEMTs due to reverse gate bias<br />

E.A. Douglas, C.-Y. Chang, T. Anderson, J. Hite, L. Lu, C.-F. Lo, B.-H. Chu, D.J. Cheney, B.P. Gila,<br />

F. Ren, G.D. Via, P. Whiting, R. Holzworth, K.S. Jones, S. Jang, and S.J. Pearton ............................................... 125<br />

SRAM Cell reliability degradations due to cell crosstalk<br />

J. Bae, S. Baeg, S.-J. Wen, and R. Wong ..................................................................................................................... 129<br />

The effect of Radon on soft error rates for wire bonded memories<br />

R. Wong, P. Su, S.-J. Wen, B. Dwyer-McNally, and S. Coleman ............................................................................... 133<br />

Understanding the influence of antifuse bitcell dimensions on the programming time and energy using<br />

an analytical model<br />

M. Deloge, B. Allard, P. Chandelier, J. Damiens, E. Le-Roux, and M. Rafik ......................................................... 135<br />

Insights about reliability of heterojunction bipolar transistor under DC stress<br />

F. Cacho, S. Ighilahriz, M. Diop, D. Roy, and V. Huard ........................................................................................... 139<br />

New DRAM HCI qualification method emphasizing on repeated memory access<br />

P.C.-F. Chia, S.-J. Wen, and S.H. Baeg ....................................................................................................................... 142<br />

Qualification of 128 Gb MLC NAND flash for space application<br />

J. Heidecker, M. White, M. Cooper, D. Sheldon, F. Irom, and D. Nguyen .............................................................. 145<br />

3D Simulation of charge collection and SEU of 0.13�m partially depleted SOI SRAM<br />

X. Zhang, S. Yue, L. Wang, and J. Li ........................................................................................................................... 149<br />

RAAPS: Reliability Aware ArchC based Processor Simulator<br />

T. Gupta, C. Bertolini, O. Heron, N. Ventroux, T. Zimmer, and F. Marc ................................................................. 153<br />

Design-in reliability for over drive applications in advanced technology<br />

J.-G. Ahn, P.-C. Yeh, J. Sowards, N. Lo, and J. Chang ............................................................................................. 157<br />

Improved evaluation of DRAM transistors and accurate resistance measurement for real chip contacts<br />

by nano-probing technique<br />

H. Park, K. Chae, S. Yamada, H.-S. Kuh, and B. Choi .............................................................................................. 161<br />

Complexities of the non-volatile memory reliability testing caused by the test structure<br />

A.A. Keshavarz, G.S. Spawn, N.D. Reyes, R. Mincitar, and L.F. Dion .................................................................... 164<br />

Tutorial Abstracts<br />

Reliability of III-V semiconductors/GaN<br />

Michael Dammann ........................................................................................................................................................ 168<br />

NBTI<br />

Hans Reisinger .............................................................................................................................................................. 168<br />

Radiation-induced soft errors: Status quo and key challenges<br />

Norbert Seifert .............................................................................................................................................................. 169<br />

BEOL<br />

James R. Lloyd ............................................................................................................................................................... 169<br />

v

vi<br />

2010<br />

Hot carriers<br />

Alain Bravaix ................................................................................................................................................................ 170<br />

TDDB physics: Transitioning from silica to high-k gate dielectrics<br />

Joe McPherson ............................................................................................................................................................... 170<br />

Discussion Group (DG) and Special Interest Group (SIG) Summaries<br />

DG: High-k ..................................................................................................................................................................... 171<br />

DG: NBTI ........................................................................................................................................................................ 172<br />

DG: BEOL ....................................................................................................................................................................... 172<br />

DG: Product reliability ................................................................................................................................................... 173<br />

DG: fast Wafer Level Reliability (fWLR) monitoring .................................................................................................. 174<br />

SIG: fast Wafer Level Reliability (fWLR) monitoring ................................................................................................. 176<br />

BIOGRAPHIES.................................................................................................................................................................... 177<br />

PICTURES .......................................................................................................................................................................... 180

2009<br />

2009<br />

2009<br />

<strong>contents</strong><br />

Foreword ...................................................................................................................................................................................... vii<br />

Keynote address abstract ............................................................................................................................................................. ix<br />

PLATFORM TECHNICAL PRESENTATIONS<br />

Reliability<br />

Investigation of SILC via energy resolved spin dependent tunneling spectroscopy<br />

J.T. Ryan, P.M. Lenahan, A.T. Krishnan, and S. Krishnan ...................................................................................................... 1<br />

New failure mechanism during high temperature storage testing and its application on SIV risk evaluation<br />

O. Aubel, W. Yao, M.A. Meyer, H.J. Engelmann, J. Poppe, F. Feustel, and C. Witt............................................................. 5<br />

Memory<br />

Electric field dependent switching and degradation of resistance random access memory<br />

K. Hosotani, S.-G. Park, and Y. Nishi ...................................................................................................................................... 11<br />

Threshold voltage (V t ) instability in high bit-count-per-cell floating-gate non-volatile memories<br />

G. Tao and J. Yang ..................................................................................................................................................................... 15<br />

A fast WLR test for the evaluation of EEPROM endurance<br />

A. Uhlemann, A. Aal, and H. Vogt ............................................................................................................................................ 20<br />

NBTI-1<br />

(Invited) Reassessing NBTI mechanisms by ultrafast charge pumping measurement<br />

D.S. Ang, Z.Q. Teo, and C.M. Ng .............................................................................................................................................. 25<br />

A study of NBTI by the statistical analysis of the properties of individual defects in pMOSFETS<br />

H. Reisinger, T. Grasser, and C. Schlünder............................................................................................................................. 30<br />

On the thermal activation of negative bias temperature instability<br />

R.G. Southwick III, W.B. Knowlton, B. Kaczer, and T. Grasser ............................................................................................ 36<br />

What triggers NBTI? An “On The Fly” electron spin resonance approach<br />

J.T. Ryan, P.M. Lenahan, T. Grasser,and H. Enichlmair ..................................................................................................... 42<br />

Future Technology–1<br />

(Invited) Interfacial engineering of InGaAs/high-k metal-oxide-semiconductor field effect<br />

transistors (MOSFETs)<br />

A.M. Sonnet, R.V. Galatage, M.N. Jivani, M. Milojevic, R A. Chapman, C.L. Hinkle, R. M. Wallace and E.M. Vogel ............46<br />

(Invited) Instabilities in oxide semiconductor transparent thin film transistors<br />

J.F. Conley, Jr............................................................................................................................................................................. 50<br />

Back-end Reliability<br />

Cu interconnect immortality criterion based on electromigration void growth saturation<br />

P. Lamontagne, L. Doyen, E. Petitprez, D. Ney, L. Arnaud, P. Waltz, and Y. Wouters ..........................................................56<br />

Comprehensive characterization of BEOL-TDDB performance using very fast voltage ramp dielectric<br />

breakdown tests<br />

O. Aubel, F. Feustel, T. Hoffmann, M. Majer, and K.Yiang......................................................................................................60<br />

iii

2009<br />

iv<br />

2009<br />

Transistor<br />

Application of fast wafer-level reliability PBTI tests for screening of high-k / metal gate process splits<br />

G. Krause, R. Geilenkeuser, M. Trentzsch, F. Graetsch, and L. Herrmann ............................................................................66<br />

Impact of instrumental current scatter on fast Bias Temperature Instability testing<br />

A. Kerber, K. Zhao, B.P. Linder, and E. Cartier .......................................................................................................................70<br />

A fast, simple wafer-level Hall-mobility measurement technique<br />

L.C. Yu, K.P. Cheung, V. Tilak, G. Dunne, K. Matocha, J.P. Campbell, J.S. Suehle, and K. Sheng ...................................73<br />

Comprehensive analysis of the degradation of a lateral DMOS due to hot carrier stress<br />

E. Riedlberger, C. Jungemann, A. Spitzer, M. Stecher, and W. Gustin................................................................................. 77<br />

Simulation of statistical aspects of reliability in nano CMOS<br />

M.F. Bukhori, A.R. Brown, S. Roy, and A. Asenov ....................................................................................................................82<br />

Bias stability of zinc-tin-oxide thin film transistors with Al O gate dielectrics<br />

2 3<br />

J. Triska, J.F. Conley, Jr., R. Presley, and J.F. Wager ............................................................................................................86<br />

NBTI-2<br />

A radically different model for NBTI in nitrided oxide MOSFETs<br />

P.M. Lenahan .............................................................................................................................................................................. 90<br />

Analytical solution of the switching trap model for negative bias temperature stress<br />

B. Bindu, W. Goes, B. Kaczer, and T. Grasser ........................................................................................................................ 93<br />

Future Technology-2<br />

Self-compensating the effect of defect generation for advanced CMOS substrates<br />

A.E. Islam and M.A. Alam.......................................................................................................................................................... 97<br />

The critical role of the defect structural relaxation for interpretation of noise measurements in MOSFETs<br />

D. Veksler, G. Bersuker, H. Park, C. Young, K. Y. Lim, W. Taylor, S. Lee, and H. Shin ..................................................... 102<br />

Back-end Reliability-2<br />

Capacitance variation under electrical stress of SiOCH low-k dielectrics for the advanced 45nm technology<br />

node and beyond<br />

M.Vilmay, D. Roy, S.Blonkowski, F. Volpi, and J-M. Chaix ................................................................................................ 106<br />

POSTER PRESENTATIONS—REFEREED<br />

The effect of Cu contamination on device reliability in DRAM<br />

J.W. Pyun, M.S. Jung, H.W. Kim, N.H. Cha, S.J. Hwang, J.S. Kang, and B.S. So ............................................................ 111<br />

Gate oxide integrity by initial gate current<br />

S. Park, S. Hwang, J. Kang, B. So, and D. Baek ................................................................................................................... 113<br />

Methodology for 3-dimensional high-density capacitor reliability evaluation<br />

G. Fiannaca, P. Gardes, L. Berneux, E. Bouyssou, and C. Anceau .................................................................................... 117<br />

Stress voltage dependence HCI induced traps distribution in 60V LDNMOS<br />

S.K. Samanta, N. Patel, K.N. ManjulaRani, and K. Jang ..................................................................................................... 120<br />

Hot-carrier reliability study and simulation methodology development for 65nm technology<br />

K.N. ManjulaRani, R.M. Mooraka, N. Patel, S. Samanta, G. Narasimhan, N. Lakshminarayanan, R. Kapre,<br />

and H. Puchner .......................................................................................................................................................................... 124<br />

The use of Taguchi method for process design of experiment to resolve gate oxide integrity issue<br />

T. Cahyadi, P.Y. Tan, M.T. Ng, T. Yeo, J.J. Boh, and B. Fun .............................................................................................. 128<br />

Effects of various applications on relative lifetime of processor cores<br />

T. Gupta, C. Bertolini, O. Heron, N. Ventroux, T. Zimmer, and F. Marc ............................................................................ 132

2009<br />

The Helium Ion Microscope for interconnect material imaging<br />

W. Thompson, S. Ogawa, L. Stern, L. Scipioni, and J. Notte ................................................................................................ 136<br />

Improvement on erase characteristics of SONOS flash memory by Bandgap Engineering of tunnel oxide<br />

D.H. Li and B.-G. Park ............................................................................................................................................................ 138<br />

fWLR supported process development based on V- and J-ramp stress tests<br />

A. Aal.......................................................................................................................................................................................... 141<br />

Correlation of electrical properties with interface structures of CVD oxide-based oxynitride tunnel dielectrics<br />

Z. Liu, H. Ishigaki, S. Ito, T. Ide, M. Makabe, M. Wilde, K. Fukutani, M. Kimura, V.A. Miha, and H. Yoshikawa ........ 145<br />

IMD stack thermal resistance effects on SiCr thin film resistor’s current density performance<br />

F. Downey .................................................................................................................................................................................. 148<br />

The investigation of the electro-thermal characteristics of a GTO thyristor at turn off using Silvaco Atlas<br />

J. Ciezki, G. Vineyard, T. Weatherford .................................................................................................................................. 151<br />

Effects of statistical thin-oxide thickness variations on the time-dependent dielectric breakdown (TDDB)<br />

parameters for wafer level reliability<br />

A.A. Keshavarz and L.F. Dion ................................................................................................................................................. 155<br />

TCAD analysis of self heating in AlGaN/GaN HEMTs under pulsed conditions<br />

T. Weatherford, Y. Wang, and S. Tracey ................................................................................................................................ 159<br />

An improved fast Id-Vg measurement technology with expanded application range<br />

C. Wang, L.C. Yu, J.P. Campbell, K.P. Cheung, Y. Xuan, P.D. Ye, J.S. Suehle, and D.W. Zhang ...................................... 163<br />

NBTI performance enhancement with process integration of high current fluorine incorporation and<br />

O 2 gas asher process in 45nm CMOS Technology<br />

S. Mahesh, X. Bin, M.F. Karim, S. Yongliang, Li Yu, Zeng Xu, Hung Odd, and Cheng Weihua ...................................... 166<br />

Effect of metal thickness variations on IC metal lifetime due to electromigration<br />

A.A. Keshavarz and L.F. Dion ................................................................................................................................................. 170<br />

TUTORIAL ABSTRACTS<br />

2009<br />

2009<br />

DNA Self-Assembled Nanostructures for Device Applications<br />

Bill Knowlton ............................................................................................................................................................................ 174<br />

International fWLR Monitoring Guideline<br />

Andreas Martin and Andreas Aal .......................................................................................................................................... 174<br />

ESD Protection Design and Qualification Challenges<br />

Charvaka Duvvury ................................................................................................................................................................... 174<br />

NBTI: Why Won’t This Thing Go Away?<br />

Jason P. Campbell ................................................................................................................................................................... 174<br />

BEOL Reliability Challenges and its Interaction with Process Integration<br />

Oliver Aubel .............................................................................................................................................................................. 174<br />

Three Dimensional Systems Integration - Concepts and Challenges<br />

Alan Mathewson ....................................................................................................................................................................... 175<br />

Reliability of Gate Dielectrics in MOSFETs:<br />

A Nanometer Scale Approach with Conductive Atomic Force Microscopy<br />

Montserrat Nafría and Marc Porti ........................................................................................................................................ 175<br />

Degradation and Reliability of Metal Gate / High-k CMOS Technologies<br />

Andreas Kerber ......................................................................................................................................................................... 175<br />

v

DISCUSSION GROUP (DG) SUMMARIES<br />

DG: NBTI .................................................................................................................................................................................... 176<br />

DG: Metal Gate / High-k ............................................................................................................................................................ 177<br />

DG: fast Wafer Level Reliability (fWLR) monitoring .............................................................................................................. 178<br />

DG: Product/Memory Reliability .............................................................................................................................................. 181<br />

BIOGRAPHIES ................................................................................................................................................................................ 182<br />

PICTURES ...................................................................................................................................................................................... 185<br />

2009<br />

vi<br />

2009<br />

2009

2008<br />

2008<br />

<strong>contents</strong><br />

Foreword ............................................................................................................................................................................................. vii<br />

Keynote address abstract ....................................................................................................................................................................ix<br />

PLATFORM TECHNICAL PRESENTATIONS<br />

NBTI–1<br />

The effect of recovery on NBTI characterization of thick non-nitrided oxides<br />

H. Reisinger, R.P. Vollertsen, P.J. Wagner, S. Aresu, W. Gustin, T. Grasser, C. Schlünder ................................................... 1<br />

Total recovery of defects generated by negative bias temperature instability<br />

C. Benard, J.-L. Ogier, and D. Goguenheim............................................................................................................................... 7<br />

Advanced On-The-Fly method with correction of initial values to characterize negative<br />

bias temperature instability reliability<br />

C. Benard, J.-L. Ogier, and D. Goguenheim..............................................................................................................................12<br />

Back-end Reliability<br />

Copper line topology impact on the reliability of SiOCH low-k dielectrics for the advanced<br />

45 nm technology node and beyond<br />

M. Vilmay, D. Roy, C. Monget, F. Volpi, J-M. Chaix ...............................................................................................................16<br />

Impact of oxygen vacancies profile and fringe effect on leakage current instability of tantalum pentoxide<br />

metal-insulator-metal (MIM) capacitors<br />

Vi. Martinez, C. Besset, F. Monsieur, L. Montès, G. Ghibaudo...............................................................................................21<br />

The influence of complex geometries and stress non-uniformity on reliability<br />

A. Aal.............................................................................................................................................................................................25<br />

Stress characterization for stress-induced voiding in Cu/Low K interconnects with geometry and upper<br />

cap layer dependences<br />

M. Lin, J.W. Liang, and K.C. Su .................................................................................................................................................32<br />

Reliability of Sensors/Memories<br />

Ageing under illumination of MOS transistors for active pixel sensors (APS) applications<br />

D. Lopez, F. Monsieur, S. Ricq, J.-M. Roux, and F. Balestra ..................................................................................................36<br />

Investigation of GIDL current Injection disturb mechanism in two-transistor-eNVM memory devices<br />

S.R. Kim, K.J. Han, J. Lee, P.Y. Lee, T. Zhou, K.-S. Lee, P. Liu, H.C. Tseng, B. Cronguist ...................................................40<br />

High-k Reliability<br />

Effect of substrate hot carrier stress on high-k gate stack<br />

H. Park, G. Bersuker, C. Y. Kang, C. Young, H-H Tseng, R. Jammy .......................................................................................44<br />

Temperature (6-300K) dependence comparison of HfO 2 /SiO 2 and SiO 2 MOS gate stacks<br />

R.G. Southwick III, J. Reed, C. Buu, H. Bui, G. Bersuker, W.B. Knowlton .............................................................................48<br />

Positive bias temperature instability effects in advanced high-k / metal gate NMOSFETs<br />

D.P. Ioannou, S. Mittl, G. LaRosa ..............................................................................................................................................55<br />

Breakdown mechanism for the thin EOT Dy 2 O 3 /HfO 2 dielectric<br />

T. Lee, S. Park, J. Lee, S. K. Banerjee ........................................................................................................................................58<br />

2008<br />

iii

iv<br />

2008<br />

2008<br />

NBTI–2<br />

Geometry effects on the NBTI degradation of PMOS transistors<br />

G. Math, C. Benard, J.-L. Ogier, D. Goguenheim .....................................................................................................................60<br />

Study of transistor and product NBTI lifetime distributions<br />

J. Qin, B. Yan, Y. Shoshany, D. Roy, H. Rahamim, J.B. Bernstein ...........................................................................................64<br />

Reliability of Compound Materials and Devices<br />

Interface traps in silicon carbide MOSFETs<br />

C.J. Cochrane, P.M. Lenahan, A.J. Lelis ...................................................................................................................................68<br />

Effect of threshold-voltage instability on SIC DMOSFET reliability<br />

A.J. Lelis, D. Habersat, R. Green, N. Goldsman ........................................................................................................................72<br />

Coupled approach for reliability study of fully self aligned SiGe:C 250 GHz HBTs<br />

M. Diop, N. Revil, M. Marin, F. Monsieur, T. Schwartzmann, G. Ghibaudo .........................................................................77<br />

fWLR Reliability<br />

Quantitative reliability assessment of plasma induced damage on product wafers with fast WLR measurements<br />

A. Martin, C. Bukethal, K.-H. Rydén, S. Baier, M. Schwerd ....................................................................................................81<br />

Negative bias temperature stress on PFETs within fast wafer level reliability monitoring<br />

R.-P. Vollertsen, H. Reisinger, C. Schlünder ............................................................................................................................86<br />

Late News<br />

Defect creation stimulated by thermally activated hole trapping as the driving force behind negative bias<br />

temperature instability in SiO , SiON, and high-k gate stacks<br />

2<br />

T. Grasser, B. Kaczer, T. Aichinger, W. Gös, and M. Nelhiebel ..............................................................................................91<br />

The effect of the subthreshold slope degradation on NBTI device characterization<br />

D. Brisbin and P. Chaparala ......................................................................................................................................................96<br />

Reliability guardband reduction by differential targeting of pMOS gate oxide thickness<br />

R. Geilenkeuser, K. Wieczorek, M. Trentzsch, F. Graetsch, B. Bayha, V. Samohvalov, T. Paetzold, and T. Schink ...... 100<br />

The origins of random telegraph noise in highly scaled SiON nMOSFETs<br />

J.P. Campbell, J. Qin, K.P. Cheung, L. Yu, J.S. Suehle, A. Oates, and K. Sheng ............................................................... 105<br />

POSTER PRESENTATIONS—REFEREED<br />

Repeatability and stress level dependence on ESD-CDM testing for microelectronic components<br />

Y. Satirakul, T. Butngam, and S. Phunyapinuant ................................................................................................................. 110<br />

Concept and implementation of an in-situ test structure for HTGS reliability testing of Power FETs on<br />

a wafer level basis<br />

S. Baier....................................................................................................................................................................................... 114<br />

Fully automatical test and qualification system for a high endurance embedded EEPROM module<br />

J. Fellner, G. Schatzberger, and A. Wiesner .......................................................................................................................... 118<br />

A robust single event upset hardened clock distribution network<br />

A.S. Mallajosyula and P. Zarkesh-Ha .................................................................................................................................... 121<br />

Reliability simulation and design consideration of high speed ADC circuits<br />

B. Yan, J. Qin, J. Dai, Q. Fan, and J.B. Bernstein.................................................................................................................. 125<br />

Dispersion and the worst case of thermal fatigue life of solder joints in vehicle electronic devices<br />

T. Maruoka, Q. Yu, T. Shibutani, and H. Miyauchi ............................................................................................................... 129<br />

A comparison between V-ramp TDDB techniques for reliability evaluation<br />

A. Aal.......................................................................................................................................................................................... 133<br />

An electrically-detected magnetic resonance study of the atomic-scale effects of fluorine on the<br />

negative bias temperature instability<br />

J.T. Ryan, P.M. Lenahan, A.T. Krishnan, S. Krishnan, J.P. Campbell ............................................................................... 137<br />

2008

2008<br />

Oxide reliability of SiC MOS devices<br />

L. Yu, K.P. Cheung, J. Campbell, J.S. Suehle, and K. Sheng ............................................................................................... 141<br />

TUTORIAL ABSTRACTS<br />

Circuit Failure Prediction for Robust System Design in Scaled CMOS<br />

Subhasish Mitra. ....................................................................................................................................................................... 145<br />

Measurement Issues for High-k Technology including NBTI<br />

Chadwin Young ........................................................................................................................................................................ 145<br />

JEDEC Overview<br />

Alvin Strong .............................................................................................................................................................................. 145<br />

Toward Understanding Negative Bias Temperature Instability<br />

Tibor Grasser ............................................................................................................................................................................ 145<br />

eFuse Design and Reliability<br />

William Tonti ............................................................................................................................................................................. 145<br />

Reliability of “Future” Devices<br />

Wilfried Haensch ....................................................................................................................................................................... 145<br />

DISCUSSION GROUP (DG) REPORTS<br />

2008<br />

DG: fast Wafer Level Reliability (fWLR) monitoring .............................................................................................................. 146<br />

DG: NVM reliability ................................................................................................................................................................... 150<br />

DG: NBTI .................................................................................................................................................................................... 151<br />

DG: Dielectric electrical characterization ................................................................................................................................. 152<br />

DG: Product reliability............................................................................................................................................................... 153<br />

BIOGRAPHIES ................................................................................................................................................................................ 154<br />

PICTURES ...................................................................................................................................................................................... 157<br />

2008<br />

v

2007<br />

2007<br />

<strong>contents</strong><br />

Foreword ............................................................................................................................................................................................. vii<br />

Keynote address abstract .................................................................................................................................................................... ix<br />

PLATFORM TECHNICAL PRESENTATIONS<br />

A new smart V th -extraction methodology considering recovery and mobility degradation due to NBTI<br />

C. Schlünder, M. Hoffmann, R.-P. Vollertsen, G. Schindler, W. Heinrigs, W. Gustin, H. Reisinger .............................................1<br />

A rigorous study of measurement techniques for negative bias temperature instability<br />

T. Grasser, P.-J Wagner, P. Hehenberger, W. Gös, B. Kaczer ...........................................................................................................6<br />

Atomic-scale defects involved in NBTI in plasma-nitrided pMOSFETs<br />

J.P. Campbell, P.M. Lenahan, A.T. Krishnan, S. Krishnan ............................................................................................................ 12<br />

Effect of NBTI degradation on transistor variability in advanced technologies<br />

S. Pae, J. Maiz, C. Prasad .................................................................................................................................................................. 18<br />

Enhanced PMOS NBTI degradation due to halo implant channeling in a DGO CMOS process<br />

D. Brisbin, J. Yang, S. Bahl, C. Parker ............................................................................................................................................ 22<br />

Charging and discharging of oxide defects in reliability issues<br />

W. Gös, T. Grasser ............................................................................................................................................................................... 27<br />

SRAM stability analysis considering gate oxide SBD, NBTI and HCI<br />

J. Qin, X. Li, J.B. Bernstein ................................................................................................................................................................ 33<br />

Investigation of NBTI recovery induced by conventional measurements for pMOSFETs<br />

with ultra-thin SiON gate dielectrics<br />

L. Jin, M. Xu ........................................................................................................................................................................................ 38<br />

Charge-gain program disturb mechanism in split-gate flash memory cell<br />

V. Markov, K. Korablev, A. Kotov, X. Liu, Y.B. Jia, T.N. Dang, A. Levi ....................................................................................... 43<br />

Scaling tunneling oxide to 50Å in floating-gate logic NVM at 65nm and beyond<br />

B. Wang, M. Niset, Y. Ma, H. Nguyen, R. Paulsen........................................................................................................................... 48<br />

A simple and accurate method to extract neutral threshold voltage of floating gate flash devices<br />

and its application to flash reliability characterization<br />

G. Tao, H. Chauveau, D. Boter, D. Dormans, R. Verhaar ............................................................................................................... 52<br />

New approach for the assessment of the effect of plasma induced damage on MOS devices<br />

and subsequent design manual rules<br />

A. Martin.............................................................................................................................................................................................. 57<br />

Charge pumping revisited – the benefits of an optimized constant base level charge pumping<br />

technique for MOS-FET analysis<br />

T. Aichinger, M. Nelhiebel ................................................................................................................................................................. 63<br />

Characterization and analysis of gate-induced-drain-leakage current in 45nm CMOS technology<br />

X. Yuan, J.-E. Park, J. Wang, E. Zhao, D. Ahlgren, T. Hook, J. Yuan, V. Chan, H. Shang, C.-H. Liang,<br />

R. Lindsay, S. Park, H. Choo ............................................................................................................................................................. 70<br />

Electromigration multistress pattern technique for copper drift velocity and Black’s parameters extraction<br />

L. Doyen, X. Federspiel,L. Arnaud, F. Terrier, Y. Wouters, V. Girault .......................................................................................... 74<br />

2007<br />

iii

iv<br />

Optimized structure design for wafer level electromigration tests<br />

X. Federspiel, D. Ney, G. Sers, L. Doyen........................................................................................................................................... 79<br />

Programming conditions for silicided poly-Si or copper electrically programmable fuses<br />

H. Suto, S. Mori, M. Kanno, N. Nagashima ..................................................................................................................................... 84<br />

Reliability investigation of NiPtSi electrical fuse with different programming mechanism<br />

C. Tian, D. Moy, B. Messenger, C. Kothandaraman, J. Safran, S. Wu, N. Robson, S.S. Iyer ....................................................... 90<br />

Defects in the interfacial layer of SiO 2 -HfO 2 gate stacks: Depth distribution and identification<br />

O. Ghobar, D. Bauza, B. Guillaumot................................................................................................................................................. 94<br />

Charge trapping of ultra-thin ZrHfO x /RuO x /ZrHfO x high-k stacks<br />

R. Wan, C.-H. Lin, Y. Kuo, W. Kuo ..................................................................................................................................................... 99<br />

New defect generation in nitrogen contented nMOS high-k devices<br />

D. Heh, P.D. Kirsch, C.D. Young, C.Y. Kang, G. Bersuker .............................................................................................................103<br />

Direct observation of electrically active interfacial layer defects which may cause threshold voltage<br />

instabilities in HfO 2 based MOSFETs<br />

J.T. Ryan, P.M. Lenahan ...................................................................................................................................................................107<br />

Characterization of interface and bulk oxide traps in SiC MOSFETs with epitaxialy grown and implanted channels<br />

M. Gurfinkel, J. Kim, S. Potbhare, H.D. Xiong, K.P. Cheung, J. Suehle, J.B. Bernstein, Y. Shapira, A.J. Lelis,<br />

D. Habersat, N. Goldsman ................................................................................................................................................................. 111<br />

POSTER PRESENTATIONS—REFEREED<br />

2007<br />

2007<br />

Investigation of substrate injection disturb mechanism in high density flash FPGA devices<br />

S.R. Kim, N. Chan, B. Sharokhi, H. Micael, J. Yaonan, S. Samiee, K.J. Han, B. Cronquist ......................................................114<br />

Fast wafer level reliability assessment of ultra thick oxides under impact ionization conditions<br />

A. Aal .................................................................................................................................................................................................117<br />

80V HVDMOS reliability characterization for 0.6µm and 0.35µm technologies<br />

C. Heffernan, M. Forde ..................................................................................................................................................................... 121<br />

Comparison of line stress predictions with measured electromigration failure times<br />

R.R. Morusupalli, W.D. Nix, J.R. Patel ...........................................................................................................................................124<br />

Comprehensive hot carrier mechanism investigation of 40V LDNMOS transistor<br />

Y.-C. Wang, Y.-P. Chen, J.-S. Li , K.-C. Su .....................................................................................................................................128<br />

Optimized reliability guardbands using variation aware junction temperature models<br />

P. Pereira, D. Kim, P. O’Shea .......................................................................................................................................................... 132<br />

Process variabilities and performances in a 90nm embedded SRAM<br />

M.Y.S. Min, P. Maurine, M. Bastian, M. Robert............................................................................................................................. 135<br />

A reliability study in p-channel punchthrough for ASIC CMOS I/O buffer leakage<br />

E. Spory.............................................................................................................................................................................................. 139<br />

Impact of DRAM process technology on neutron-induced soft errors<br />

L. Borucki, G. Schindlbeck, C. Slayman ........................................................................................................................................ 143<br />

DC bias effects on data retention at room temperature in SONOS nonvolatile memory devices<br />

J.-M. Hwang, T. Wallinger ............................................................................................................................................................... 147<br />

2007

TUTORIAL ABSTRACTS<br />

Detection of atomic scale defects in MOS reliability problems<br />

P.M. Lenahan ............................................................................................................................................................................ 150<br />

Current issues in SRAM reliability<br />

B. Woolery.................................................................................................................................................................................. 150<br />

Reliability of floating-gate flash memories<br />

N. Mielke ................................................................................................................................................................................... 151<br />

Reliability assessment methodology for high-k gate stacks<br />

G. Bersuker ................................................................................................................................................................................ 151<br />

Beam-based defect localization in ICs<br />

E.I. Cole Jr. ................................................................................................................................................................................ 152<br />

Semiconductor device scaling: general trends and reliability implications for space<br />

A. Johnston ................................................................................................................................................................................ 152<br />

DISCUSSION GROUP (DG) REPORTS<br />

DG: NBTI .................................................................................................................................................................................... 153<br />

DG: High-k dielectric stacks...................................................................................................................................................... 155<br />

DG: Interconnects ..................................................................................................................................................................... 156<br />

DG: Product reliability............................................................................................................................................................... 157<br />

SPECIAL INTEREST GROUP (SIG) REPORT<br />

2007<br />

2007<br />

SIG: fast Wafer Level Reliability (fWLR) Monitoring ............................................................................................................ 159<br />

BIOGRAPHIES ................................................................................................................................................................................ 161<br />

PICTURES ...................................................................................................................................................................................... 164<br />

2007<br />

v

2006<br />

2006<br />

<strong>contents</strong><br />

Foreword ....................................................................................................................................................................................... vi<br />

PLATFORM TECHNICAL PRESENTATIONS<br />

On the impact of the NBTI recovery phenomenon on lifetime prediction of modern p-MOSFETs<br />

C. Schlunder, W. Heinrigs, W. Gustin, H. Reisinger................................................................................................................. 1<br />

Modeling of dispersive transport in the context of negative bias temperature instability<br />

T. Grasser, W. Gos, B. Kaczer .................................................................................................................................................... 5<br />

Negative bias stressing interface trapping centers in metal gate hafnium oxide field effect transistors<br />

using spin dependent recombination<br />

C.J. Cochrane, P.M. Lenahan, J.P. Campbell, G. Bersuker, P. Lysaght, A. Neugroschel ................................................ 11<br />

Effects of delay time and AC factors on negative bias temperature instability of PMOSFETs<br />

J-S. Li, M Chen, P. Juan, and K. Su ......................................................................................................................................... 16<br />

Bias stress induced conduction mechanism evolution in silica based inter-metal dielectrics<br />

Y. Li, G. Groeseneken, K. Maex, Z Tõkei ................................................................................................................................. 20<br />

Dynamics of resistance evolution during electromigration<br />

X. Federspiel, D. Ney, L. Doyen, V. Girault .......................................................................................................................... 24<br />

Stress migration phenomena in narrow copper lines<br />

H. Matsuyama et al..................................................................................................................................................................... 28<br />

Impact of TiN plasma post-treatment on alumina electron trapping<br />

A. Bajolet, S. Bruyère, M. Proust, L. Montès, G. Ghibaudo .................................................................................................. 31<br />

Constant-current stressing of SiCr-based thin film resistors: Initial “wearout” investigation<br />

R. Brynsvold, K. Manning .......................................................................................................................................................... 37<br />

Effect of photo misalignment on N-LDMOS hot carrier device reliability<br />

D. Brisbin, P. Lindorfer, P. Chaparala .................................................................................................................................... 44<br />

Ultra-fast measurements of V th instability in SiC MOSFETs due to positive and negative constant bias stress<br />

M. Gurfinkel, J. Suehle, J. Bernstein, Y. Shapira, A.J. Lelis, D. Habersat, N. Goldsman .................................................. 49<br />

Effect of self-heating on HCI lifetime prediction in SOI technologies<br />

J.M. Roux, X. Federspiel, D. Roy .............................................................................................................................................. 54<br />

Reliability characterizations of a 150GHz Ft/Fmax Si/SiGeC heterjunction bipolar transistor<br />

under reverse, forward and mixed-mode stress<br />

M. Ruat, J. Bourgeat, M. Marin, G. Ghibaudo, N. Revil, G. Pananakakis........................................................................... 59<br />

Impact of hot carrier degradation modes on I/O nMOSFETS aging prediction<br />

C. Guerin, V. Huard, A. Bravaix, M. Denais ........................................................................................................................... 63<br />

Reliability issues related to fast charge loss mechanism in embedded non volatile memories<br />

P. Mora, S. Renard, G. Bossu, P. Waltz, G. Pananakakis, G. Ghibaudo ............................................................................. 68<br />

Flash oxide scalability model and impact of program/erase method<br />

A. Haggag, P. Kuhn, P. Ingersoll, C. Li, T. Harp, A. Hoefler, D. Burnett, K. Baker, K. Chang ................................................... 73<br />

Experimental study of temperature dependence of program/erase endurance of embedded Flash<br />

memories with 2T-FNFN device architecture<br />

G. Tao, H. Chauveau, S. Nath ................................................................................................................................................... 76<br />

A critical failure source in 65nm-MLC NOR flash memory incorporating Co-salicidation process<br />

J. Han, B. Lee, J. Han, W. Kwon, C. Chang, S. Sim, C. Park, and K. Kim........................................................................... 80<br />

2006<br />

iii

iv<br />

2006<br />

2006<br />

Study of electrically programmable fuses through series of I-V measurements<br />

H. Suto, S. Mori, M. Kanno, N. Nagashima ............................................................................................................................. 83<br />

NiSi polysilicon fuse reliability in 65nm logic CMOS technology<br />

B. Ang, S. Tumakha, J. Im, S. Paak........................................................................................................................................... 89<br />

Non-Arrhenius temperature acceleration and stress-dependent voltage acceleration for<br />

semiconductor device involving multiple failure mechanisms<br />

J. Qin, J. Bernstein ..................................................................................................................................................................... 93<br />

Fast productive WLR characterization methods of plasma induced damage of thin and thick MOS gate oxides<br />

A. Martin, C. Siol, C. Schlünder................................................................................................................................................ 98<br />

Practical considerations for wafer-level electromigration monitoring in high volume production<br />

O. Aubel, T.D. Sullivan, D. Massey, T.C. Lee, T. Merrill, S. Polchlopek, A. Strong ......................................................... 105<br />

Spatial probing of traps in nMOSFETs with ALD HfO 2 /SiO 2 stacks using low frequency noise characteristics<br />

H. Xiong, J. Suehle ................................................................................................................................................................... 111<br />

New insight on the origin of Stress Induced Leakage Current for SiO 2 /HfO 2 dielectric stacks<br />

M. Rafik, G. Ribes, D. Roy, S. Kalpat, G. Ghibaudo............................................................................................................. 116<br />

Fast and slow charge trapping/detrapping processes in high-k nMOSFETs<br />

D. Heh, R. Choi, C. D. Young, and G. Bersuker .................................................................................................................. 120<br />

Influence of stress-induced-leakage-current on reliability of HfSiO x with EOT>1.5nm and TiN gate<br />

S. Jakschik, T. Kauerauf, R. Degreave, Y.N. Hwang, R. Duschl, M. Kerber, A. Avelan, S. Kudelka .............................. 125<br />

Leakage current variation with time in Ta 2 O 5 MIM and MIS capacitors<br />

J-P. Manceau, S. Bruyere, S. Jeannot, A. Sylvestre, P. Gonon............................................................................................ 129<br />

POSTER PRESENTATIONS—REFEREED<br />

Residual resistivity model and its application<br />

L. Doyen, X. Fererspiel, D. Ney, G. Sers, V. Girault, L. Arnaud, Y. Wouters....................................................................... 134<br />

Ultra-fast NBTI monitoring and end-of-life projection<br />

C. Wang, W. Chang, W. Ke, K. Su ............................................................................................................................................. 136<br />

Impact of monitoring voltage on the lifetime extrapolation during the accelerated degradation tests<br />

F. Duan, S. Cooper, A. Marathe, J. Zhang, S. K. Jayanarayanan ...................................................................................... 139<br />

Oxide reliability: a new methodology for reliability evaluation at parametric testing<br />

R. Bottini, A. Sebastiani, N. Galbiati, C. Scozzri, G. Ghidini ................................................................................................... 142<br />

Preliminary study of the breakdown strength of TiN/HfO 2 /SiO 2 /Si MOS gate stacks<br />

R. Southwick, M.C. Elgin, G. Bersuker, R. Choi, W.B. Knowlton ...................................................................................... 146<br />

Cryogenic performance & reliability of GaAs CHFETs<br />

R. Leon & Y. Chen .................................................................................................................................................................... 148<br />

Lithography CD variation effects on LFNDMOS transistor hot carrier degradation<br />

M.Thomason, C.A. Billman, B. Greenwood, B. Williams, C. Belisle, F. Bauwens .............................................................. 152<br />

Product reliability trends, derating considerations and failure mechanisms with scaled CMOS<br />

M White, D. Vu, D. Nguyen, R. Ruiz, Y. Chen, J.B. Bernstein ............................................................................................. 156<br />

Modeling and characterization of bias stress-induced instability of SiC MOSFETs<br />

A.J. Lelis, S. Potbhare, D. Habersat, G. Pennington, N. Goldsman ................................................................................... 160<br />

Temperature effects on the hot-carrier induced degradation of pMOSFETs<br />

S-Y. Chen, C-H. Tu, J-C. Lin, P-W. Kao, W-C. Lin, Z-W. Jhou, S. Chou, J. Ko, H-S. Haung ......................................... 163<br />

ESD robustness of 40-V CMOS devices with/without drift implant<br />

W-J. Chang, M-D. Ker, T-H. Lai, R. Choi,T-H. Tang, K-C. Su ........................................................................................... 167<br />

Burn-in acceleration considerations in 90nm system LSI<br />

N. Wakai, Y. Kobira, T. Oishi, S. Yamasaki, H. Egawa ........................................................................................................ 171<br />

Reliability of strain-Si FPGA product fabricated by novel ultimate spacer process<br />

2006<br />

Y.H. Luo, D. Nayak, J. Lee, D. Gitlin, C.T.Tsai .................................................................................................................... 175

2006<br />

2006<br />

The correlation of interface defect density and power-law exponent factor on ultra-thin gate dielectric reliability<br />

J.Y.C. Yang, C-L. Lin, C-Y. Hu, J-P. Chen, C-J. Kao, K.C. Su............................................................................................ 179<br />

Fast prediction of gate oxide reliability – Application of the cumulative damage principle for transforming<br />

V-ramp breakdown distributions into TDDB failure distributions<br />

A. Aal .......................................................................................................................................................................................... 182<br />

Ultra-thin gate oxide lifetime projection and degradation mechanism beyond 90 nm CMOS technology<br />

C.-L. Lin, T. Kao, J-P. Chen, J.Y.C. Yang, K.C. Su .............................................................................................................. 186<br />

Impact of error correction code and dynamic memory reconfiguration on high reliability/low cost server memory<br />

C. Slayman, M. Ma, S. Lindley ................................................................................................................................................ 190<br />

Blowing polysilicon fuses: What conditions are best?<br />

Y. Li and A. Tang ...................................................................................................................................................................... 194<br />

A new mechanism of poly-silicon crater defect induced from Al tiny particle charging effect during water rinse<br />

in oxide patterning process<br />

L.J. Duan, H.H. Au, M. Kuan, P.S. Quek, K.S. Pey .............................................................................................................. 198<br />

Wafer reliability evaluation and monitoring for InGaAsP devices<br />

D.E. Verbitsky ........................................................................................................................................................................... 201<br />

Surface roughness enhanced current in defectively stressing poly-oxide-poly capacitors<br />

L. Sheng, E. DeBacker, D. Wojciechowski, J. DeGreve, K. Dhondt, S. Boonen, D. Malschaert, E. Snyder................... 205<br />

Retention reliability improvement of SONOS non-volatile memory with N 2 O oxidation tunnel oxide<br />

J.-L. Wu, C-H. Kao, H-C. Chien, T-K. Tsai, C-Y. Lee, C-W. Liao, C-Y. Chou, M-I. Yang ............................................... 209<br />

Surface morphology change of titanium nitride film after metal layer photolithography rework<br />

causing oxide film de-lamination<br />

H.T. Chiew, J. Tan, S. Lim, K.S. Lee, L.Y. Ren, B.C. Lee, P.S. Quek, K.S. Pey ................................................................. 213<br />

TUTORIAL ABSTRACTS<br />

Reliability of on-the-shelf stored image sensors<br />

A.J.P. Theuwissen ..................................................................................................................................................................... 215<br />

New Challenges and requirements to reliability research and development in semiconductor technology evolution<br />

Y. Ma .......................................................................................................................................................................................... 215<br />

Phase change memory reliability<br />

S.J. Ahn ...................................................................................................................................................................................... 216<br />

Stategy of future reliability qualification<br />

A. Preussger .............................................................................................................................................................................. 216<br />