Yoshio NISHI - Fondation Nanosciences

Yoshio NISHI - Fondation Nanosciences Yoshio NISHI - Fondation Nanosciences

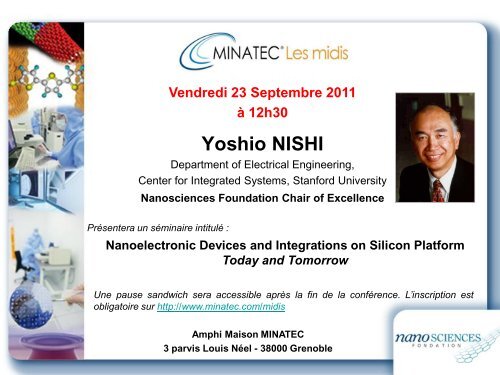

Vendredi 23 Septembre 2011 à 12h30 Yoshio NISHI Department of Electrical Engineering, Center for Integrated Systems, Stanford University Nanosciences Foundation Chair of Excellence Présentera un séminaire intitulé : Nanoelectronic Devices and Integrations on Silicon Platform Today and Tomorrow Une pause sandwich sera accessible après la fin de la conférence. L’inscription est obligatoire sur http://www.minatec.com/midis Amphi Maison MINATEC 3 parvis Louis Néel - 38000 Grenoble

- Page 2 and 3: Nanoelectronic Devices and Integrat

Vendredi 23 Septembre 2011<br />

à 12h30<br />

<strong>Yoshio</strong> <strong>NISHI</strong><br />

Department of Electrical Engineering,<br />

Center for Integrated Systems, Stanford University<br />

<strong>Nanosciences</strong> Foundation Chair of Excellence<br />

Présentera un séminaire intitulé :<br />

Nanoelectronic Devices and Integrations on Silicon Platform<br />

Today and Tomorrow<br />

Une pause sandwich sera accessible après la fin de la conférence. L’inscription est<br />

obligatoire sur http://www.minatec.com/midis<br />

Amphi Maison MINATEC<br />

3 parvis Louis Néel - 38000 Grenoble

Nanoelectronic Devices and Integrations on Silicon Platform<br />

Today and Tomorrow<br />

There is widely shared concern today that as we approach future technology nodes of CMOS<br />

beyond sub-20nm, diminishing return in device performance and density combined with<br />

serious increase in on-chip power consumption would force us to seek for possible<br />

alternatives beyond simple scaling of the minimum geometry.<br />

Applications of mechanical strain to MOSFET channel for improved transport characteristics,<br />

material alternatives for conductive channel of MOSFET such as germanium and/or III-V<br />

semiconductor, intensive study for partial replacement of on-chip interconnects with optical<br />

interconnect, new nonvolatile memory phenomena thereby feasibility of new memory devices<br />

such as resistive switching are only a part of such efforts in addition to global trend of going<br />

3D devices and integration. Also mentioned should include a variety of “nano” materials such<br />

as carbon nanotube, graphene, topological insulator etc, which might capture unique positions<br />

in integrated circuit technology arsenal with further in-depth understanding and technological<br />

break-through for controlling their characteristics.<br />

This talk will discuss a perspective of a variety of nanoelectronic devices to be integrated on<br />

silicon platform, and where they would likely be heading toward.

Biography of <strong>Yoshio</strong> <strong>NISHI</strong><br />

<strong>Yoshio</strong> Nishi received BS in material science and PhD in electronics engineering from<br />

Waseda University and University of Tokyo, respectively. He joined Toshiba R&D Center<br />

where he studied silicon process technology and MOS device physics, resulting in a variety<br />

of achievements including discovery of Si-SiO2 interface paramagnetic PB center, the<br />

structural origin of interface states.<br />

Later he led the development of the world first 1Mbit CMOSDRAM, 16bit SOS<br />

microprocessor. He joined Hewlett-Packard Laboratories in 1986 as director of silicon<br />

process laboratory for high performance CMOS R&D, followed by joinning Texas Instruments<br />

as senior vice president and director of R&D in 1995. Since 2002 he has been professor of<br />

electrical engineering, Stanford University, where he serves as director of research for Center<br />

for Integrated Systems, director, Stanford Site of National Nanotechnology Infrastructure<br />

Network.<br />

His research activities cover resistive switching nonvolatile memory, high performance<br />

alternative material channel MOSFETs, Ge and Si optical transmitter and graphene research.<br />

He published more than 250 papers and conference presentations and hold more than 50<br />

patents in Japan and US. He is IEEE Fellow, and recipients of 1995 IEEE Jack Morton<br />

Award, 2002 IEEE Robert Noyce Medal, 2007 Technology Management award, 2008 SEMI<br />

Lifetime achievements award.<br />

<strong>Yoshio</strong> <strong>NISHI</strong><br />

Email: nishiy@stanford.edu