QDK PIC24/dsPIC-XC16 - Quantum Leaps

QDK PIC24/dsPIC-XC16 - Quantum Leaps

QDK PIC24/dsPIC-XC16 - Quantum Leaps

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>QDK</strong><br />

<strong>PIC24</strong>/<strong>dsPIC</strong>-<strong>XC16</strong><br />

www.state-machine.com/pic<br />

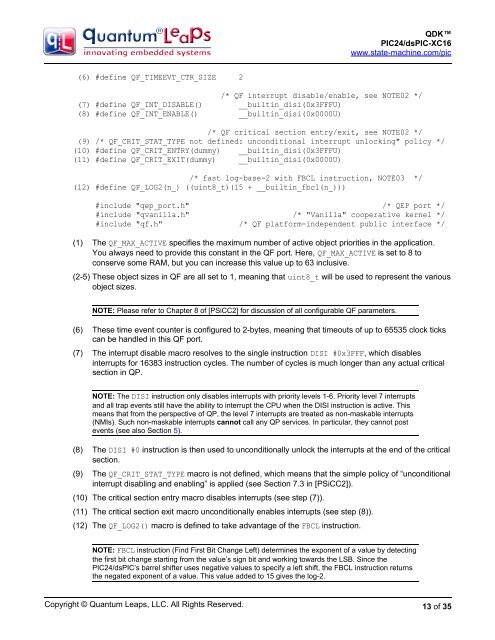

(6) #define QF_TIMEEVT_CTR_SIZE 2<br />

/* QF interrupt disable/enable, see NOTE02 */<br />

(7) #define QF_INT_DISABLE() __builtin_disi(0x3FFFU)<br />

(8) #define QF_INT_ENABLE() __builtin_disi(0x0000U)<br />

/* QF critical section entry/exit, see NOTE02 */<br />

(9) /* QF_CRIT_STAT_TYPE not defined: unconditional interrupt unlocking" policy */<br />

(10) #define QF_CRIT_ENTRY(dummy) __builtin_disi(0x3FFFU)<br />

(11) #define QF_CRIT_EXIT(dummy) __builtin_disi(0x0000U)<br />

/* fast log-base-2 with FBCL instruction, NOTE03 */<br />

(12) #define QF_LOG2(n_) ((uint8_t)(15 + __builtin_fbcl(n_)))<br />

#include "qep_port.h" /* QEP port */<br />

#include "qvanilla.h" /* "Vanilla" cooperative kernel */<br />

#include "qf.h" /* QF platform-independent public interface */<br />

(1) The QF_MAX_ACTIVE specifies the maximum number of active object priorities in the application.<br />

You always need to provide this constant in the QF port. Here, QF_MAX_ACTIVE is set to 8 to<br />

conserve some RAM, but you can increase this value up to 63 inclusive.<br />

(2-5) These object sizes in QF are all set to 1, meaning that uint8_t will be used to represent the various<br />

object sizes.<br />

NOTE: Please refer to Chapter 8 of [PSiCC2] for discussion of all configurable QF parameters.<br />

(6) These time event counter is configured to 2-bytes, meaning that timeouts of up to 65535 clock ticks<br />

can be handled in this QF port.<br />

(7) The interrupt disable macro resolves to the single instruction DISI #0x3FFF, which disables<br />

interrupts for 16383 instruction cycles. The number of cycles is much longer than any actual critical<br />

section in QP.<br />

NOTE: The DISI instruction only disables interrupts with priority levels 1-6. Priority level 7 interrupts<br />

and all trap events still have the ability to interrupt the CPU when the DISI instruction is active. This<br />

means that from the perspective of QP, the level 7 interrupts are treated as non-maskable interrupts<br />

(NMIs). Such non-maskable interrupts cannot call any QP services. In particular, they cannot post<br />

events (see also Section 5).<br />

(8) The DISI #0 instruction is then used to unconditionally unlock the interrupts at the end of the critical<br />

section.<br />

(9) The QF_CRIT_STAT_TYPE macro is not defined, which means that the simple policy of “unconditional<br />

interrupt disabling and enabling” is applied (see Section 7.3 in [PSiCC2]).<br />

(10) The critical section entry macro disables interrupts (see step (7)).<br />

(11) The critical section exit macro unconditionally enables interrupts (see step (8)).<br />

(12) The QF_LOG2() macro is defined to take advantage of the FBCL instruction.<br />

NOTE: FBCL instruction (Find First Bit Change Left) determines the exponent of a value by detecting<br />

the first bit change starting from the value’s sign bit and working towards the LSB. Since the<br />

<strong>PIC24</strong>/<strong>dsPIC</strong>’s barrel shifter uses negative values to specify a left shift, the FBCL instruction returns<br />

the negated exponent of a value. This value added to 15 gives the log-2.<br />

Copyright © <strong>Quantum</strong> <strong>Leaps</strong>, LLC. All Rights Reserved.<br />

13 of 35