You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>:<br />

Facts vs. Fiction<br />

DesignCon 2006<br />

TecPreview<br />

Jim Nadolny<br />

Corey Kimble<br />

Slide 1<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

Outline<br />

• Background<br />

• <strong>Samtec</strong> Model Requests<br />

• Simulation Tools<br />

• <strong>Connector</strong> <strong>Models</strong><br />

– SPICE vs. <strong>IBIS</strong> vs. S-parameter<br />

• Syntax differences<br />

• Example connector<br />

• <strong>Connector</strong> analysis<br />

– PSPICE vs. Allegro PCB SI<br />

• Conclusion<br />

• Resources<br />

Slide 2<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

Background<br />

• High speed (>1 Gb/s) serial<br />

data is mainstream<br />

– PCI Express<br />

– Fibre Channel<br />

– XAUI<br />

• Analysis is required for<br />

– System timing (jitter)<br />

– Amplitude margin (eye<br />

opening)<br />

Slide 3<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

Background<br />

Tools<br />

– Cadence, Mentor, Synopsys, etc.<br />

– Analysis only as good as the models used<br />

– Need models for drivers, receivers and interconnect path<br />

– <strong>Connector</strong>s can be a dominant crosstalk and reflection<br />

mechanism in the interconnect path so “good”<br />

connector models are required<br />

– What syntax should be used for the connector model,<br />

and where do you get them?<br />

• To answer the syntax question, we need to review the<br />

simulation tools used for high speed digital analysis<br />

and look at what customers ask for…<br />

Slide 4<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Samtec</strong> Model Requests<br />

<strong>Samtec</strong> Perspective<br />

– Emphasis is on customer service [easy]<br />

• we logged 1500 SI service requests in 2005<br />

– Requests are for SPICE, <strong>IBIS</strong> or S-parameter<br />

models<br />

– We have learned to ask a few more questions<br />

when a customer requests an “<strong>IBIS</strong> model”<br />

Slide 5<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Samtec</strong> Model Requests<br />

<strong>Samtec</strong> Perspective<br />

– Customers request “<strong>IBIS</strong>” models<br />

– <strong>Samtec</strong> customers are using simulation tools that import<br />

<strong>IBIS</strong> models for drivers/receivers but do not import <strong>IBIS</strong> ICM<br />

connector models<br />

– When you dig deeper you find that customers are looking<br />

for models that import directly into their tools:<br />

• Mentor Graphics, HyperLynx, ICX/TAU<br />

• Cadence, Allegro PCB SI<br />

• This is not an endorsement for these tools, rather<br />

it is what our customer base is generally using (in<br />

addition to Synopsys HSPICE)<br />

Slide 6<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Samtec</strong> Model Requests<br />

Information Required for a <strong>Samtec</strong> Model<br />

• What are the part numbers of the MATED connector?<br />

• What is the model structure needed? Single-line? Single<br />

differential pair? Multi-line?<br />

• What is the simulation tool that you are using?<br />

• Information on the performance requirements of your<br />

application<br />

– signal specification<br />

– wiring pattern<br />

Slide 7<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

Simulation Tools<br />

Mentor Graphics<br />

– HyperLynx GHz, EXT<br />

• Import models in .slm or .sp format (spice-like)<br />

– ICX/TAU<br />

• Import models in .mmf format or <strong>IBIS</strong> 4.1 EBD<br />

format<br />

– Note that EBD format is an RLC network useful for<br />

timing but not crosstalk<br />

– EBD is a “creative workaround” to obtain a<br />

connector model from an electrical board<br />

description<br />

Slide 8<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

Simulation Tools<br />

Cadence<br />

– Allegro PCB SI 210/230<br />

• Import models in .dml format (spice like)<br />

– format supports single line models (no crosstalk) or<br />

multi-line models (includes crosstalk)<br />

– Allegro PCB SI 630<br />

• Import models in .dml format or S-parameter<br />

format.<br />

Slide 9<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Connector</strong> <strong>Models</strong><br />

• SPICE<br />

– .cir (PSpice)<br />

– .sp (HSPICE)<br />

• SPICE-like<br />

– .sp (ELDO)<br />

Minor syntax differences from SPICE<br />

– .dml (eSpice)<br />

• <strong>IBIS</strong><br />

– .icm<br />

Significant syntax differences from<br />

• <strong>IBIS</strong>–like<br />

SPICE, uses keywords<br />

– .mmf (ICX)<br />

• S-parameters<br />

Frequency<br />

– .s4p (Touchstone)<br />

domain representation<br />

(must be passive, causal)<br />

Slide 10<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Connector</strong> <strong>Models</strong><br />

SPICE vs. <strong>IBIS</strong> syntax differences<br />

SPICE<br />

• Comments preceded by “*”<br />

• Subcircuit definition begins<br />

with .subckt and ends with<br />

.ends<br />

• Model elements connected<br />

to nodes<br />

• Comment<br />

– Developed for IC’s<br />

<strong>IBIS</strong> (ICM)<br />

• Comments preceded by “|”<br />

• Subcircuit definition begins<br />

with [Begin_ICM_Section]<br />

and ends with [End ICM<br />

Section]<br />

• Model elements are<br />

inductance and<br />

capacitance matrices<br />

• Syntax driven by keywords<br />

• Comment<br />

– Developed for connectors<br />

Slide 11<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

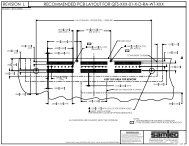

Example<br />

<strong>Samtec</strong> QTE/QSE <strong>Connector</strong><br />

• 0.8mm pitch<br />

• 5mm-30mm stacking height<br />

•

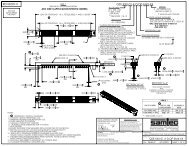

Example<br />

Available QTE/QSE <strong>Connector</strong> <strong>Models</strong><br />

All models represent the QTE/QSE 5mm stack height<br />

connector.<br />

• DM5_QTE_QSE.dml = Cadence DML ESPICE multi-line<br />

• DM5_QTE_QSE.sp = ELDO model for HyperLynx<br />

• slm_g_qte01_qse01.icm = <strong>IBIS</strong> ICM single-line general<br />

• MM5_QTE_QSE.MMF = Mentor Graphics ICX MMF<br />

format multi-line<br />

• MQTE1QSE1.mlm = SPICE multi-line<br />

We also can do single-line in DML, ELDO, and MMF<br />

Slide 13<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Connector</strong> Analysis<br />

PSPICE vs. Allegro PCB SI<br />

Cadence Allegro PCB SI (.dml format) vs. Cadence<br />

PSPICE (.cir format)<br />

– perform connector analysis<br />

• crosstalk, impedance, input and output waveform<br />

– Compare results (sim. time, ease of analysis)<br />

– Use QTE/QSE 5mm model<br />

• multi-line model with 1:1 S/G ratio<br />

– Include footprint parasitics in the analysis<br />

– 100ps risetime source<br />

Slide 14<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Connector</strong> Analysis<br />

PSPICE vs Allegro PCB SI<br />

3.00E-01<br />

PSPICE vs Allegro PCB SI<br />

2.50E-01<br />

Voltage (volts)<br />

2.00E-01<br />

1.50E-01<br />

1.00E-01<br />

5.00E-02<br />

Input Side of <strong>Connector</strong> Allegro PCB SI<br />

Input Side of <strong>Connector</strong> -PSPICE<br />

0.00E+00<br />

-5.00E-02<br />

0.0E+00<br />

5.0E-10<br />

1.0E-09<br />

time (s)<br />

1.5E-09<br />

2.0E-09<br />

2.5E-09<br />

Slide 15<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Connector</strong> Analysis<br />

PSPICE vs. Allegro PCB SI<br />

3.00E-01<br />

PSPICE vs Allegro PCB SI<br />

2.50E-01<br />

Voltqage (volts)<br />

2.00E-01<br />

1.50E-01<br />

1.00E-01<br />

5.00E-02<br />

Output Side of <strong>Connector</strong> Allegro PCB SI<br />

Output Side of <strong>Connector</strong> -PSPICE<br />

0.00E+00<br />

-5.00E-02<br />

0.0E+00<br />

5.0E-10<br />

1.0E-09<br />

time (s)<br />

1.5E-09<br />

2.0E-09<br />

2.5E-09<br />

Slide 16<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Connector</strong> Analysis<br />

PSPICE vs. Allegro PCB SI<br />

4.00E-03<br />

PSPICE vs Allegro PCB SI<br />

3.00E-03<br />

NEXT PSPICE<br />

NEXT Allegro PCB SI<br />

NEXT (v)<br />

2.00E-03<br />

1.00E-03<br />

0.00E+00<br />

-1.00E-03<br />

0.00E+00<br />

5.00E-10<br />

1.00E-09<br />

time (s)<br />

1.50E-09<br />

2.00E-09<br />

2.50E-09<br />

Slide 17<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

<strong>Connector</strong> Analysis<br />

PSPICE vs. Allegro PCB SI<br />

3.00E-03<br />

PSPICE vs Allegro PCB SI<br />

2.00E-03<br />

FEXT PSPICE<br />

FEXT Allegro PCB SI<br />

FEXT (v)<br />

1.00E-03<br />

0.00E+00<br />

-1.00E-03<br />

0.00E+00<br />

5.00E-10<br />

1.00E-09<br />

1.50E-09<br />

2.00E-09<br />

2.50E-09<br />

time (s)<br />

Slide 18<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

Analysis Results<br />

Runtimes<br />

• Allegro PCB SI – 1 minute 23 seconds<br />

• PSPICE – 50 seconds<br />

Ease of Use<br />

• PCB SI graphs buffer voltages, internal nodes not<br />

accessible<br />

• Required creative use of “ESpice” device for graphing<br />

and for 100 ps source<br />

Slide 19<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

Conclusion<br />

• <strong>IBIS</strong> connector models are well defined but are not<br />

widely incorporated into SI tools<br />

• Syntax changes are required to convert SPICE<br />

models into SPICE-like formats required by SI tools<br />

• <strong>Samtec</strong> has performed these syntax conversions so<br />

that connector models can be incorporated<br />

directly into SI tools.<br />

– Less work required by the customer [easy]<br />

– Equivalent performance regardless of tool used<br />

Slide 20<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

Resources<br />

• All <strong>Samtec</strong> connector models available at<br />

http://www.samtec.com<br />

• Information on <strong>IBIS</strong> models<br />

http://www.eda.org/pub/ibis/connector/<br />

• Translating SPICE models to .dml format for Cadence<br />

Allegro PCB SI<br />

http://www.cadence.com/community/allegro/pcb_si/tr.<br />

aspx?type=Modeling<br />

• Any SI questions? sig@samtec.com<br />

Slide 21<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction

Acknowledgments<br />

• Kim Helliwell (consultant) performed the<br />

comparisons between PSPICE and Cadence<br />

Allegro PCB SI<br />

Slide 22<br />

DesignCon 2006<br />

<strong>IBIS</strong> <strong>Connector</strong> <strong>Models</strong>, Fact vs. Fiction