Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

OUTL<br />

LINE<br />

1. HP's memristor and applications<br />

2. Models of resistance switching<br />

3. Volatility speed tradeo<br />

ffs<br />

4. 3D circuit architectures<br />

5. Proposal for evaluation framework

HP’S MEMRISTOR<br />

memristor = memory + resistor<br />

Dmitri <strong>Strukov</strong>, <strong>UC</strong>SB<br />

SRC/NSF/A*STAR forum<br />

October 2009<br />

HP’s memristor = TiO 2 resistance change due to oxygen vacancy migration<br />

circuit theory<br />

+<br />

TiO 2 devices<br />

=<br />

HP’s memristor<br />

L.Chua, S.Kang<br />

several groups,<br />

R.S.Williams<br />

T.W.Hickmott first<br />

L .Chua, IEEE Trans. Circuit Theory<br />

18 507 (1971); L.Chua et al. Proc.<br />

IEEE 64 209 (1976)<br />

“pure memristor”<br />

vs.<br />

“memristive”<br />

small subset: T.W.Hickmott JAP 33 2669 (1962); R.Meyer et al. APL<br />

86 112904 (2005); B.J.Choi et al. JAP 98 033715 (2005); C.Yoshida<br />

et al. APL 91 223510 (2007); K.M.Kim et al. APL 91 012907 (2007);<br />

K.Tsunoda et al. APL 90 113501 (2007)<br />

v = R(w) i<br />

dw/dt = i<br />

unipolar/bipolar l RRAM, CBRAM, PCR<br />

RAM etc. are all memristive devices<br />

no simple dynamical model so far for experimental devices<br />

still okay for most applications (using feedback)<br />

applications: memories, FPGAs, electronic synapse, analog circuits (trimming)<br />

just a small biased subset (the&exp) for mem: Baek et al. IEDM (2005); D.<strong>Strukov</strong> et<br />

al. J. Nanoscience&Nanotechnol. 7 151 (2007); J.Green et al. Nature 445 414 (2007);<br />

S.H.Jo Nano Letters 9 870 (2009); FPGAs: D.<strong>Strukov</strong> et al. Nanotechnol .16 888 (2005); D.<strong>Strukov</strong> et al. IEEE Tran.Nanotechnol. 6 696 (2007); Q.Xia et al. Nano Letters<br />

(2009); ANNs: K.Likharev et al. Ann. New York Acad. Sci. 1006 146-163 (2003); G.Snider Nanotechnology 18 365202 (2007); analog: S.Shin et al. Proc. ICCCAS (2009)<br />

starting<br />

point<br />

(t=0)<br />

R<br />

3 >> 2 >> 1<br />

resistance<br />

change<br />

range<br />

R.S.Williams IEEE Spectrum (2008);<br />

J.Yang et al. Nature Nano 3 429 (2008);<br />

D.<strong>Strukov</strong> et al. Nature 453 80 (2008)<br />

3 0<br />

v = R(w,i,t) i<br />

i= sin[ t]<br />

2<br />

dw/dt = f(w,i,t)<br />

, , )<br />

q<br />

1<br />

0<br />

3 >> 2 >> 1<br />

i-v collapses to straight line at high frequencies for pure memristors<br />

nonlinear i-v with no hysteresis (i.e. at small biases) & nonlinear ionic drift = not a pure memristor<br />

good starting point:<br />

M.Pickett et al. JAP<br />

106 074508 (2009)<br />

J.Borghetti (priv.comm.)<br />

i<br />

t<br />

v

BULK vs INTERFACE BIPOLAR RESIST<br />

TIVE SWITCHING<br />

Dopant N D (x)/N DO<br />

bulk theory<br />

semiconductor with N A fixed<br />

and N D (x) mobile ions<br />

ON: n<br />

w<br />

+ ‐n‐n +<br />

10 ‐1 OFF: n + ‐n‐p‐n n p n<br />

+<br />

10 ‐2<br />

10 ‐3 10 ‐4 10 ‐3 10 ‐2<br />

time t/t 0<br />

N A<br />

D.<strong>Strukov</strong> et<br />

al. Small 5<br />

1058 (2009)<br />

inte<br />

erface<br />

OFF<br />

ON<br />

Dmitri <strong>Strukov</strong>, <strong>UC</strong>SB<br />

SRC/NSF/A*STAR forum<br />

October 2009<br />

ONOFF<br />

I. barrier height/leakage modulation<br />

TO<br />

CMO<br />

e.g. two layer system: R.Meyer et al. Proc. NVMTS (2008)<br />

tial ‐φ/(E G /e)<br />

Poten<br />

0.2<br />

0<br />

Current<br />

v<br />

t<br />

Voltage<br />

0 Length x/L 1<br />

1D model …<br />

but initial<br />

conditions for<br />

3D (i.e. after<br />

forming) are<br />

hard to<br />

simulate…<br />

… and experiment<br />

H.Yang et al.<br />

Nature Mat. 8<br />

585 (2009)<br />

IIa. barrier width/bridging due to radial ion motion<br />

Ag<br />

H 2 O<br />

Pt<br />

Ag<br />

H 2 O<br />

Pt<br />

e.g. in CBRAM: X.Guo et al. APL 91 1 (2007)<br />

chalcogenide electrolytes: M.N.Kozicki<br />

et al. J Non-Crys. Solids 352 567 (2006)<br />

IIb. barrier width/bridging due to vertical ion motion<br />

Co oncentration (log sc cale)<br />

gap profile<br />

Barrier width<br />

1<br />

0.8<br />

0.6<br />

0.4<br />

0.2<br />

grossly simplified picture, mix of all mechanisms in reality…<br />

E=10,1,0.1 MV/cm<br />

10 -8 10 -6 10 -4 10 -2 10 0<br />

time, s<br />

D.<strong>Strukov</strong> et al. (preliminary data)

WRITE SPEED VS. RETENTION<br />

linear ionic transport<br />

<br />

<br />

store<br />

~<br />

write<br />

( v 0)<br />

( v V )<br />

I<br />

V <br />

D<br />

nonlinear<br />

effect<br />

due to temperature<br />

and/or electric field<br />

e.g. temperature only:<br />

U A<br />

store<br />

V k T<br />

<br />

<br />

write<br />

I<br />

V<br />

V<br />

T<br />

U<br />

k T<br />

B store B write<br />

~ ( e e )<br />

V<br />

T<br />

D.<strong>Strukov</strong> et al. Appl.Phys.A 94 515 (2009)<br />

A<br />

Dmitri <strong>Strukov</strong>, <strong>UC</strong>SB<br />

SRC/NSF/A*STAR forum<br />

October 2009<br />

other sources of nonlinearity?<br />

Buttler Volmer reactions<br />

R.Waser et al. Adv.Mat 21<br />

2632 (2009)<br />

Electrochemical effects…<br />

e/ write<br />

store<br />

10 7<br />

10 4 3<br />

10 3<br />

L=100 nm<br />

30 nm<br />

10 nm<br />

3 nm<br />

10 1<br />

ionic<br />

10<br />

A B<br />

conductor<br />

mobile<br />

0.1 0.2<br />

U B (eV)<br />

0.3 0.5<br />

interacting ions<br />

D.<strong>Strukov</strong> (unpublished)<br />

Joule heating<br />

M.Janousch et al.<br />

Adv.Mat 19 2232<br />

(2007)<br />

XRF map<br />

infrared<br />

curre ent, mA<br />

8<br />

6 1000 K<br />

4<br />

2<br />

0 900 K -2<br />

-4<br />

-2.0 -1.0 0.0 1.0<br />

voltage, V<br />

map<br />

temperature on I-V<br />

perform 3D<br />

coupled<br />

electrothermal<br />

simulations<br />

fit experimental<br />

data using<br />

equivalent<br />

circuit<br />

J.Borghetti<br />

et al.JAP<br />

(2009)<br />

to appear<br />

strong nonlinearity in ionic transport required for high retention, even more for half select<br />

1100 K<br />

TiO 2<br />

(ρ I ,κ I )<br />

OFF state<br />

d OUT<br />

w OFF<br />

d C<br />

metallic<br />

channel<br />

(ρ C ,κ C )<br />

electrode (ρ E ,κ E )<br />

L<br />

v<br />

R C<br />

r<br />

R ON<br />

ON state<br />

extract<br />

geometry<br />

from fitting<br />

z<br />

0<br />

d ON<br />

w ON<br />

D.<strong>Strukov</strong> et al. MRS (2009)<br />

)<br />

Temperature (K)<br />

Local<br />

mA)<br />

I (<br />

15<br />

10<br />

5<br />

0<br />

290K<br />

140K<br />

3K<br />

INTERMEDIATE<br />

ON<br />

OFF<br />

‐5<br />

‐1.0 ‐0.5 0.0 0.5 1.0<br />

V (V)<br />

600<br />

500<br />

400<br />

300<br />

0<br />

ON<br />

Domain fitted on data<br />

Extrapolation<br />

OFF<br />

10 20<br />

I (mA)<br />

SHORT<br />

30

3D STACKING FOR CMOL CIRCUITS<br />

peripheral<br />

layer addr<br />

ess<br />

word address<br />

read/write<br />

drive<br />

word<br />

line<br />

decoder<br />

layer<br />

decoder<br />

layer<br />

predecoder<br />

Dmitri <strong>Strukov</strong>, <strong>UC</strong>SB<br />

SRC/NSF/A*STAR forum<br />

October 2009<br />

d d hybrid<br />

stack of<br />

thin film<br />

crossbar arrays<br />

(m layers)<br />

n<br />

wires<br />

main idea: area + peripheral interface<br />

word line<br />

decoder<br />

switching layers<br />

1 st 2 nd 3 rd<br />

layer decoder<br />

control<br />

lines<br />

layer decoder<br />

layer<br />

predecoder<br />

area distributed<br />

N 4<br />

data<br />

lines<br />

1 st 2 nd<br />

layer layer<br />

just<br />

few examples:<br />

M.-J.Lee IEDM 85 (2008) M.Johnson IEEE J Solid State Circuits 38 1920 (2003)<br />

crossbar<br />

layers<br />

CMOS<br />

layer<br />

tilted crossbar<br />

area interface<br />

2F<br />

2F<br />

N<br />

N<br />

2 N<br />

theory: K.Likharev Interface 14 43 (2005); D.<strong>Strukov</strong> et al. PNAS (2009)<br />

3 rd<br />

layer<br />

virtual<br />

crossbar<br />

xpoint in 1 st layer<br />

crossbar<br />

wire via<br />

drive/sense<br />

data<br />

xpoint in 2 nd layer<br />

layer<br />

address<br />

D.<strong>Strukov</strong><br />

(unpublished)<br />

N 4<br />

via<br />

bit line sense/driver<br />

CMOS layer<br />

xpoint<br />

element<br />

less semi-selected devices for read op.<br />

parallel write for current controlled devices<br />

less maximum current density<br />

… but less dense<br />

D.<strong>Strukov</strong> (unpublished)<br />

total<br />

..<br />

but<br />

CMOS only CMOS +xbar<br />

(N) 2<br />

only<br />

per<br />

layer<br />

xbar<br />

nanowire<br />

layer 2<br />

switching layer<br />

nanowire<br />

layer 1<br />

CMOS layer<br />

…and exp with just one xbar layer: Q.Xia et al. Nano Letters (2009)

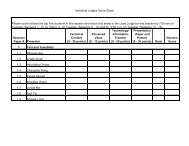

PROPOSAL FOR EVALUATION METRIC<br />

intrinsic<br />

circuit and device tradeoffs<br />

electromigration<br />

issues in wires, smaller<br />

blocks (less dense), and<br />

low throughput smaller<br />

readout margins etc<br />

potentially volatile<br />

device<br />

resistance<br />

low<br />

high<br />

switching<br />

speed<br />

slow<br />

fast<br />

e.g. reset current scaling<br />

thKW<br />

(K/W)<br />

V RESET (V)<br />

V R<br />

0.001 0.01 0.1 1<br />

10<br />

0.01<br />

L=30 nm<br />

1<br />

0.1<br />

3 nm<br />

0.001<br />

c =20 K/W-m (e.g. Ti)<br />

10 4<br />

0.001 0.01R/L<br />

0.1 1<br />

RL<br />

slow RC<br />

likely volatile<br />

and/or large switching<br />

voltages<br />

low endurance,<br />

bad repeatability<br />

e.g. due to higher<br />

electric field and<br />

temperatures<br />

axial<br />

radial<br />

=6 K/W m<br />

(e.g. TiO 2 )<br />

=1 K/W-m<br />

(e.g. SiO 2 )<br />

3 100<br />

=6 K/W-m<br />

1 30<br />

=6 K/W-m<br />

c =20 K/W-m<br />

ΔT =0,<br />

c =0.8-cm<br />

10<br />

0.3 L=3 nm<br />

0.01 0.1<br />

I RESET (mA)<br />

1<br />

D.<strong>Strukov</strong><br />

(in preparation)<br />

proposa<br />

al for software<br />

framework<br />

electronic device characterization:<br />

(1) nonlinearity in I-V shape; (2) nonlinearity<br />

in switching; (3) nature of the switching<br />

compliance for reset and set; (4) polarity of<br />

switching; (5) asymmetry of switching<br />

threshold voltages; (6) switching speed; (7)<br />

retention; (8) nominal set/reset voltage/current<br />

values; (9) variations in I-V shape upon<br />

cycling (repeatability); (10) endurance; (11)<br />

device yield; (12) forming step, etc.<br />

design constrains:<br />

density, cost, speed, power<br />

power density, throughput<br />

fabrication consideration:<br />

design rules<br />

s, electromigration specs,<br />

electorode thermal and electrical<br />

resistivity, manufacturing cost<br />

main<br />

goals<br />

Dmitri <strong>Strukov</strong>, <strong>UC</strong>SB<br />

SRC/NSF/A*STAR forum<br />

October 2009<br />

material device<br />

characterization<br />

published<br />

device data<br />

OPTIMAL CIRCUIT<br />

ARHCITECTURE<br />

via parametric search:<br />

circuit architecture,<br />

block size, sensing/<br />

biasing scheme, voltage<br />

scaling, def. tolerance<br />

scheme etc.<br />

explore for more then drop-in replacement<br />

expose important missing device and circuit information<br />

help in focusing on the most important issues