Specification of RTRM08 Transceiver Module Easywave I2C - ELDAT

Specification of RTRM08 Transceiver Module Easywave I2C - ELDAT

Specification of RTRM08 Transceiver Module Easywave I2C - ELDAT

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Specification</strong><br />

Index 1.01<br />

Project No.<br />

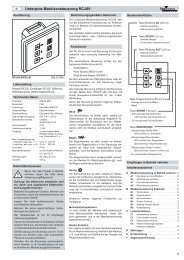

RF-Products, Controller <strong>RTRM08</strong> <strong>Transceiver</strong> <strong>Module</strong> Easw I 2 C Page 5<br />

Development<br />

Production S. Schreiber 2007-08-24<br />

Pin number Signal name Signal direction Description<br />

1 VCC - Power supply (2.1 V ...5.25 V).<br />

2 GND - Ground.<br />

3 / RESET in Reset. Active low.<br />

4 SDA bidirectional (open-drain) I 2 C serial data I/O.<br />

5 SCL bidirectional (open-drain) I 2 C synchronous serial clock I/O.<br />

6 / REQ out (open-drain) Request output. It indicates whether an<br />

<strong>Easywave</strong> telegram could be received and<br />

whether a received <strong>Easywave</strong> telegram is<br />

over. Active low.<br />

7 - 12 (NC) - Pins are not allowed to connect to any circuit.<br />

There are options for the antenna available, for example, coaxial connectors or an antenna via the module's<br />

connector. Please contact <strong>ELDAT</strong>.<br />

2.2 Power up and Reset<br />

The module's / RESET signal is not allowed to be high until the power supply is in the operational range. The<br />

module is in inactive state subsequently; it can be controlled via the I 2 C-bus.<br />

The / REQ output <strong>of</strong> the module goes to (active) low until the module's rx mode is altered.<br />

The module also can be reset at any time independent from its former state by asserting the / RESET signal.<br />

2.3 I 2 C-bus<br />

The SCL and the SDA pin are the I 2 C-bus as defined in the “THE I 2 C-BUS SPECIFICATION VERSION 2.1“<br />

(January 2000), document order number 9398 393 40011 by Philips.<br />

A short discussion <strong>of</strong> the I 2 C-bus follows in this section. If both this specification <strong>of</strong> the <strong>RTRM08</strong> transceiver<br />

module and the referred “THE I 2 C-BUS SPECIFICATION VERSION 2.1“ document define a specific detail,<br />

the specification <strong>of</strong> the <strong>RTRM08</strong> transceiver module has informational characteristics only.<br />

The I 2 C clock rate <strong>of</strong> the transceiver module can be up to 100 kHz (Standard Mode).<br />

Signal Lines <strong>of</strong> the I 2 C-bus<br />

The I 2 C-bus is a 2-wire bus; it has a bidirectional serial clock line SCL and a bidirectional serial data line SDA.<br />

Both SCL and SDA are combined inputs and open-drain outputs. There must be one pullup-resistor on each<br />

<strong>of</strong> the SCL and the SDA line. The <strong>RTRM08</strong> transceiver module I 2 C PHY does not include these pullupresistors.<br />

A device connected to a bus can be either a master or a slave. A master device is able to acquire the I 2 C-bus<br />

and initiate a transfer from (read) or to (write) a specified slave. The master generates the clock on the SCL<br />

line in order to transfer the serial data bits. The slave can slow down the transfer if it can't transmit or receive<br />

data bytes fast enough (clock stretching, see below). The master has to terminate the transfer and release<br />

the I 2 C-bus either successfully or due to a fail.<br />

The SDA line is driven by the device which transmits data bits: it is either a master or a slave.<br />

One or more master devices can be connected to the I 2 C-bus. This specification covers examples with one<br />

master only, but the transceiver module also works on I 2 C-busses with more than one master (multi-master).<br />

7007