Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Circuit Descriptions, Abbreviation List, and IC Data Sheets <strong>LC7.1E</strong> PA 9. EN 81<br />

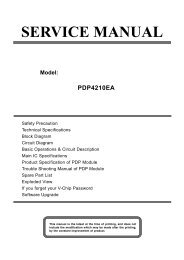

9.10.5 Diagram B07, Type TDA8932T (IC7A01), Audio Amplifier<br />

Block Diagram<br />

OSCREF<br />

OSCIO<br />

VDDA<br />

10<br />

31<br />

8<br />

28<br />

BOOT1<br />

IN1P<br />

IN1N<br />

2<br />

3<br />

OSCILLATOR<br />

V SSD<br />

PWM<br />

MODULATOR<br />

CTRL<br />

DRIVER<br />

HIGH<br />

DRIVER<br />

LOW<br />

29<br />

27<br />

26<br />

V DDP1<br />

OUT1<br />

V SSP1<br />

INREF<br />

12<br />

MANAGER<br />

21<br />

BOOT2<br />

IN2P<br />

IN2N<br />

DIAG<br />

15<br />

14<br />

4<br />

PROTECTIONS:<br />

OVP, OCP, OTP,<br />

UVP, TF, WP<br />

PWM<br />

MODULATOR<br />

CTRL<br />

DRIVER<br />

HIGH<br />

DRIVER<br />

LOW<br />

V DDA<br />

STABILIZER 11 V<br />

V SSP1<br />

20<br />

22<br />

23<br />

25<br />

V DDP2<br />

OUT2<br />

V SSP2<br />

STAB1<br />

CGND<br />

7<br />

V DDA<br />

STABILIZER 11 V<br />

V SSP2<br />

24<br />

STAB2<br />

POWERUP<br />

6<br />

REGULATOR 5 V<br />

18<br />

DREF<br />

MODE<br />

V SSD<br />

ENGAGE<br />

5<br />

V DDA<br />

11<br />

HVPREF<br />

30<br />

HVP1<br />

TEST<br />

13<br />

TDA8932<br />

V SSA<br />

19<br />

HVP2<br />

HALF SUPPLY VOLTAGE<br />

Pin Configuration<br />

9<br />

V SSA<br />

1, 16, 17, 32<br />

V SSD(HW)<br />

V SSD(HW) 1<br />

32 V SSD(HW)<br />

IN1P 2<br />

31 OSCIO<br />

IN1N 3<br />

30 HVP1<br />

DIAG<br />

4<br />

29 VDDP1<br />

ENGAGE 5<br />

28 BOOT1<br />

POWERUP 6<br />

27 OUT1<br />

CGND<br />

7<br />

26 VSSP1<br />

V DDA 8<br />

25 STAB1<br />

TDA8932T<br />

V SSA 9<br />

24 STAB2<br />

OSCREF 10<br />

23 V SSP2<br />

HVPREF 11<br />

22 OUT2<br />

INREF 12<br />

21 BOOT2<br />

TEST<br />

13<br />

20 VDDP2<br />

IN2N 14<br />

19 HVP2<br />

IN2P 15<br />

18 DREF<br />

V SSD(HW) 16<br />

17 V SSD(HW)<br />

G_16860_045.eps<br />

300107<br />

Figure 9-15 Internal block diagram and pin configuration