EI0312 VLSI - SRM University

EI0312 VLSI - SRM University

EI0312 VLSI - SRM University

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Course Code : EI0310<br />

Course Title : <strong>VLSI</strong> and Embedded Systems<br />

Year& Semester : 06<br />

Course duration : Jan-May 2012 (Even semester)<br />

Location : Tech park<br />

Faculty Details:<br />

<strong>SRM</strong> UNIVERSITY<br />

Faculty of Engineering and Technology<br />

DEPARTMENT OF EIE<br />

Name of the staff Section Office Office Mail ID<br />

Hours<br />

Mrs. G.Deiva Durga<br />

EIE-A<br />

EIE -B<br />

Tech Park 8.30-4 pm deivadurga.g@ktr.srmuniv.ac.in<br />

Required Text Books:<br />

• Wayne Wolf, Modern <strong>VLSI</strong> Design (System on Silicon), Prentice Hall PTR 2000<br />

• Michael John Sabestian Smith, Application Specific Integrated circuits, 2002<br />

• Douglas Pucknell, Basic <strong>VLSI</strong> Design Systems and Circuits, Prentice Hall PTR 2000<br />

• Neil Weste & Kamran Eshrangian, Principles of CMOS <strong>VLSI</strong> Design, Addison Wesley, 2nd edition 1998<br />

• Jacob Baker, Harry, David E.Boyce, CMOS Circuit Design, Layout and Simulation, Prentice Hall India 1998<br />

Web Resource:<br />

Objective:<br />

www.en.wikipedia.org/wiki/<strong>VLSI</strong>_engineering<br />

The students will be able to understand the techniques<br />

• MOS device operation, fabrication and designing gates<br />

• Circuits using MOS transistors<br />

• Basics of Sequential system design<br />

• Introduction to ASIC<br />

• Introduction to fault models and testing<br />

Tentative test details and portions:<br />

Cycle Test – I : UNIT-I & II (4.02.2013)<br />

Cycle Test –II : UNIT-III & IV (4.03.2013)<br />

Model Exam : ALL 5 UNITS (15.04.2013)

Assessment details:<br />

Cycle test-I<br />

10 points<br />

Cycle test-II<br />

10 points<br />

Model exam<br />

10 points<br />

Surprise test<br />

5 points<br />

Attendance<br />

5 points<br />

Total 50<br />

Outcomes:<br />

Students who have successfully completed this course<br />

Study of MOS technology and circuits.<br />

Gain knowledge of Layout and digital Circuits.<br />

Understanding of ASIC<br />

Purpose FPGA<br />

Knowledge of Faults<br />

The students will be able to understand the types<br />

of MOS, their properties and their design with<br />

stick diagrams<br />

The Students will be able to analyze scaling in<br />

MOS, pass transistor, Supper Buffer, Clocking<br />

Strategies, PLA and PAL design.<br />

The students will have a broad knowledge in<br />

Floor planning, Placement and routing.<br />

The Students will be able to acquire knowledge<br />

about FPGA<br />

The students can acquire a clear knowledge of<br />

testability, controllability and observability of the<br />

model,<br />

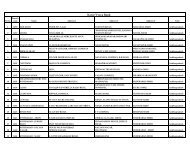

Detailed Session Plan:<br />

DAY NAME OF THE TOPICS REFERENCE<br />

UNIT-I<br />

1 Digital systems and <strong>VLSI</strong><br />

2 CMOS Technology<br />

3 Bipolar technologies<br />

MOS circuits electrical properties<br />

4 Integrated Circuit Design Techniques<br />

5 Transistors and Layout<br />

6 Fabrication Process of nMOS<br />

7 Fabrication process of CMOS<br />

8 Stick diagram and Layout<br />

9 Design Rules<br />

UNIT-II<br />

10 Introduction to Logic Gates<br />

11 Combinational Logic Functions and Static<br />

Complementary Gates<br />

12 Wires and Delays, Switch Logic<br />

1. Douglas A. Pucknell,<br />

Basic <strong>VLSI</strong> Design<br />

Systems and Circuits,<br />

Prentice Hall of India,<br />

1993<br />

2. Wayne Wolf, Modern<br />

<strong>VLSI</strong> Design (System on Silicon),<br />

Prentice Hall PTR 2000<br />

1. Douglas A. Pucknell,<br />

Basic <strong>VLSI</strong> Design<br />

Systems and Circuits,<br />

Prentice Hall of India,<br />

1993

13 Alternative Gate Circuits 2. Wayne Wolf, Modern<br />

14 Combinational Logic Networks<br />

<strong>VLSI</strong> Design (System on Silicon),<br />

Prentice Hall PTR 2000<br />

15 Layout Design Methods<br />

16 Combinational Network Delay<br />

17 Cross Talk - Power Optimization<br />

18 Switch Logic Networks - Combinational Logic<br />

Testing.<br />

UNIT-III<br />

19 Sequential Machines<br />

20 Latches and Flipflops<br />

21 Sequential system and Clocking discipline<br />

22 Sequential System Design - Power Optimization<br />

23 Design Validation - Sequential Testing<br />

24 Subsystem design - Combinational Shifters<br />

25 Adders- ALU - Multipliers<br />

26 High Density Memory<br />

UNIT-IV<br />

27 Application Specific Integrated Circuits<br />

28 Types of ASIC<br />

29 Design Flow of <strong>VLSI</strong><br />

30 Types of Simulation<br />

31 Programmable ASIC<br />

32 Floor planning - Placement<br />

33 Partitioning - Routing<br />

UNIT-V<br />

34 Types of PLD, FPLA<br />

35 FPGA Architecture<br />

36 Fault Models - Stuck-at-Faults<br />

37 Design for testability<br />

38 Design for controllability<br />

39 Design for absorvability<br />

40 LFSR - Boundary Scan Techniques.<br />

1. Douglas A. Pucknell,<br />

Basic <strong>VLSI</strong> Design<br />

Systems and Circuits,<br />

Prentice Hall of India,<br />

1993<br />

2. Wayne Wolf, Modern<br />

<strong>VLSI</strong> Design (System on Silicon),<br />

Prentice Hall PTR 2000<br />

1. Wayne Wolf, Modern <strong>VLSI</strong><br />

Design (System on Silicon),<br />

Prentice Hall PTR 2000<br />

2. Michael John Sabestian Smith,<br />

Application Specific Integrated<br />

circuits, 2002<br />

1. Michael John Sabestian Smith,<br />

Application Specific Integrated<br />

circuits, 2002