Preliminary - Reptips

Preliminary - Reptips

Preliminary - Reptips

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

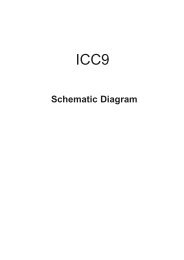

DIGITAL BLOCK DIAGRAM<br />

0<br />

2<br />

DIGITAL<br />

VIDEO IF<br />

DDR RAM<br />

TO<br />

JUNCTION<br />

(VIDEO)<br />

CN7108<br />

CN1002<br />

AO_IEC958, AI_D[0], A_MUTE2[H], K_BUS_CLK<br />

K_BUS_REQ, SYS_RESET[L], K_BUS_IN/OUT<br />

SW5V, SW12V, D5V, D3.3V<br />

D2.5V, D1.8V, V3.3V<br />

SDRAM_DQ[0-15]<br />

RA1609<br />

to<br />

RA1612<br />

DDR_DQ[0-15]<br />

IC1601<br />

IC1603<br />

DDR SDRAM<br />

SDRAM_DQ[16-31]<br />

RA1613<br />

to<br />

RA1616<br />

DDR_DQ[16-31]<br />

IC1602<br />

IC1604<br />

DDR SDRAM<br />

AO_SCLK, AO_MCLKO, AO_FSYNC, DAC_RST[L]<br />

DAC_SCL, DAC_SDA, AO_D[0], A_DAC_CS<br />

DDR_A[0-12]<br />

TO<br />

JUNCTION<br />

(VIDEO)<br />

CN7109<br />

CN1001<br />

CIN<br />

VYIN<br />

YV_OUT<br />

C_OUT<br />

CB_OUT<br />

CR_OUT<br />

Y<br />

C<br />

Cb<br />

Cr<br />

Y<br />

C<br />

Q1008<br />

SW<br />

Y<br />

Q1002 to Q1005<br />

BUF<br />

IC1001<br />

Video<br />

Controller<br />

IC1002<br />

SDRAM<br />

VI_D[2-9], VIDEO_RST[L]<br />

VO_D[0-15], SPI_MOSI<br />

VIDEO_27M, VIDEO_CS<br />

VIDEO_MUTE[H], SPI_CLK<br />

VIDEO_RXD<br />

AP, A0 to A9,DQ0 to DQ15<br />

UDQM, WE,CAS, RAS<br />

VI_D[2-9]<br />

VO_D[0-15]<br />

VIDEO_27M<br />

SDRAM_A[0-12]<br />

SDRAM_A[14-17]<br />

SDRAM_CKE<br />

SDRAM_RAS_L<br />

SDRAM_CAS_L<br />

SDRAM_WE_L<br />

RA1625<br />

to<br />

RA1628<br />

R1601<br />

to<br />

R1604<br />

DDR_BA[0]<br />

DDR_BA[1]<br />

DDR_CS[0]<br />

DDR_CKE<br />

DDR_RAS_L<br />

DDR_CAS_L<br />

DDR_WE_L<br />

SDRAM_CLK[0]<br />

DDR_CLK[0]<br />

TO<br />

JUNCTION<br />

(VIDEO)<br />

CN7105<br />

OPEN<br />

CN1404<br />

CN1403<br />

MEDIA PROCESSOR<br />

JLIP_TX<br />

JLIP_RX<br />

UART2_TX<br />

UART2_RX<br />

VI_D[2-9], VO_D[0-15]<br />

SDRAM_DQ[0- 31]<br />

SDRAM_A[0-12]<br />

SDRAM_A[14-17]<br />

SDRAM_DQS[0] to [3]<br />

SDRAM_DQM[0] to [3]<br />

SDRAM_CLK[0], SDRAM_CLK[1]<br />

SDRAM_CLK_L[0], SDRAM_CLK_L[1]<br />

SDRAM_CKE, SDRAM_RAS_L<br />

SDRAM_CLK[1]<br />

SDRAM_CLK_L[0]<br />

SDRAM_CLK_L[1]<br />

SDRAM_DQM[0] to [3]<br />

SDRAM_DQS[0] to [3]<br />

R1613<br />

to<br />

R1616<br />

RA1653<br />

to<br />

R1660<br />

DDR_CLK[1]<br />

DDR_CLK_L[0]<br />

DDR_CLK_L[1]<br />

DDR_DQM[2],[3]<br />

DDR_DQS[2],[3]<br />

DDR_DQM[0],[1]<br />

DDR_DQS[0],[1]<br />

SDRAM_CAS_L, SDRAM_WE_L<br />

1394<br />

J4112<br />

3 6<br />

JACK<br />

CN4104<br />

CN1801<br />

1394PFY<br />

TPA+<br />

TPA-<br />

TPB+<br />

TPB-<br />

IC1801<br />

IEEE1394<br />

Controller<br />

PHY_RESET[L]<br />

PHY_LREQ<br />

PHY_CLK<br />

PHY_CNA<br />

PHY_CTL[0]<br />

PHY_CTL[1]<br />

PHY_DATA[0-7]<br />

PHY_LPS<br />

PHY_LINK_ON<br />

IC1401<br />

Media<br />

Processor<br />

VIDEO_RXD, VIDEO_CS<br />

VIDEO_27M, AO_SCLK, AO_FSYNC<br />

AO_MCLKO, AO_IEC958, AO_D[0]<br />

AI_D[0], SPI_MOSI, SPI_CLK<br />

DAC_SCL, DAC_SDA, A_DAC_CS<br />

DAC_RST[L], VIDEO_RST[L], VIDEO_MUTE[H]<br />

IC1404<br />

3.3V --> 5.0V<br />

A_MUTE2[H]<br />

K_BUS_CLK<br />

K_BUS_REQ<br />

ATAPI IF<br />

FOR JIG<br />

CN1404<br />

FLASH<br />

IC1201<br />

Flash<br />

memory<br />

IC1203<br />

IC1204<br />

Transparent<br />

MADD[1-5]<br />

MADD[6-22]<br />

E5_RESET[L]<br />

LH_AR[6] to LH_AR[21]<br />

MADD[6-21]<br />

ALE<br />

MADD[1-5]<br />

MADD[6-22]<br />

E5_RESET[L]<br />

UART2_TX, UART2_RX<br />

RD/WR[L]<br />

OE[L]/LDS[L]<br />

CS[0]<br />

MADD[1-5]<br />

RD/WR[L]<br />

OE[L]/LDS[L]<br />

CS[0]<br />

MADD[1-5]<br />

ALE<br />

IC1405<br />

5.0V --> 3.3V<br />

ATA_RESET, ATA_DAT[0-15], ATA_DMARQ<br />

ATA_IORDY, ATA_INTRQ, ATA_DIOW[L]<br />

ATA_DIOR[L], ATA_DMAACK[L], ATA_ADD[0] to [4]<br />

SYS_RESET[L]<br />

K_BUS_IN/OUT<br />

ATA_RESET<br />

ATA_DAT[0-15]<br />

ATA_DIOW[L]<br />

ATA_DIOR[L]<br />

ATA_DMAACK[L]<br />

ATA_ADD[0] to [4]<br />

ATA_DMARQ<br />

ATA_IORDY<br />

ATA_INTRQ<br />

RA2201<br />

to<br />

RA2205<br />

RA2206<br />

RA2207<br />

HD_AT[0] to [15]<br />

RSTATA<br />

DMARQ, DIOW, DIOR<br />

IORDY, DMACK, INT_ATA<br />

ATA_A0, ATA_1,ATA_A2<br />

CS1FX, CS3FX<br />

CN2201<br />

TO<br />

DVD<br />

Recorder<br />

Unit<br />

2-63 2-64