State Algorithm - Ra.informatik.tu-darmstadt.de

State Algorithm - Ra.informatik.tu-darmstadt.de

State Algorithm - Ra.informatik.tu-darmstadt.de

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

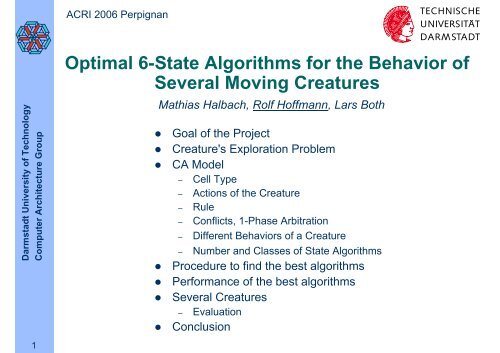

ACRI 2006 Perpignan<br />

Optimal 6-<strong>State</strong> <strong>Algorithm</strong>s for the Behavior of<br />

Several Moving Crea<strong>tu</strong>res<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

Mathias Halbach, Rolf Hoffmann, Lars Both<br />

• Goal of the Project<br />

• Crea<strong>tu</strong>re's Exploration Problem<br />

• CA Mo<strong>de</strong>l<br />

– Cell Type<br />

– Actions of the Crea<strong>tu</strong>re<br />

– Rule<br />

– Conflicts, 1-Phase Arbitration<br />

– Different Behaviors of a Crea<strong>tu</strong>re<br />

– Number and Classes of <strong>State</strong> <strong>Algorithm</strong>s<br />

• Procedure to find the best algorithms<br />

• Performance of the best algorithms<br />

• Several Crea<strong>tu</strong>res<br />

– Evaluation<br />

• Conclusion<br />

1

Goal of the Project in general<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

• Challenge<br />

– Automatically <strong>de</strong>tecting optimal rules for given CA problems, in<br />

particular problems with moving crea<strong>tu</strong>res/agents/robots<br />

– Why: <strong>State</strong> Explosion, Very time consuming<br />

• Solution<br />

– Find efficient algorithms for<br />

• selection of relevant rules<br />

• simulation<br />

• evaluation<br />

– Hardware Support<br />

• Applications<br />

– Artificial Worlds<br />

– Mo<strong>de</strong>ls of Real Worlds<br />

– Computational Tasks<br />

2

Crea<strong>tu</strong>re's Exploration Problem<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

• The Problem<br />

– Given is a 2D-CA with obstacles and<br />

moving crea<strong>tu</strong>res.<br />

– Goal:<br />

Find an optimal local rule for the<br />

crea<strong>tu</strong>res to visit a maximum<br />

number of empty cells with a<br />

minimum number of time steps for a<br />

given set of initial configurations.<br />

• Applications<br />

– Mowing a lawn in shortest time<br />

– Vacuum cleaning a room by a robot<br />

– Exploring an unknown environment<br />

3

The Actions of the Crea<strong>tu</strong>res<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

L<br />

R<br />

Lm<br />

Rm<br />

(<strong>tu</strong>rn Left)<br />

(<strong>tu</strong>rn Right)<br />

(<strong>tu</strong>rn Left and move)<br />

move forward and<br />

simultaneously <strong>tu</strong>rn left<br />

(<strong>tu</strong>rn Right and move)<br />

move forward and<br />

simultaneously <strong>tu</strong>rn right<br />

4

The Rule for the Crea<strong>tu</strong>res<br />

FrontCell<br />

Legend<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

(a1) if (obstacle or crea<strong>tu</strong>re) then<br />

(a2) if (collision) then<br />

<strong>tu</strong>rn (L/R)<br />

<strong>tu</strong>rn (L/R)<br />

obstacle or<br />

crea<strong>tu</strong>re<br />

irrelevant<br />

5<br />

(b) if not((a1) or (a2)) then <strong>tu</strong>rn and move(Lm/Rm)<br />

crea<strong>tu</strong>re<br />

in one<br />

out of two<br />

directions

CA: Cell Type<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

Type<br />

CREATURE<br />

EMPTY<br />

Direction r<br />

toNorth, toEast,<br />

toSouth, toWest<br />

(irrelevant)<br />

control state s<br />

0, 1, ... (N-1)<br />

OBSTACLE<br />

(irrelevant)<br />

6

CA: Rule<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

Rule for My.Type = CREATURE<br />

(a1) {CASE free}<br />

if (My.FrontCell.Type = EMPTY) and (My.FrontCell.SignalsFree) then<br />

• My.Type := EMPTY // <strong>de</strong>lete, because of moving<br />

else<br />

(b) {CASE not free}<br />

• My.Direction:= TurnRight/Left (My.Direction) // only <strong>tu</strong>rn R, L<br />

Rule for My.Type = EMPTY<br />

(a2) {CASE free}<br />

n = Number of crea<strong>tu</strong>res with direction to MY<br />

if (n=1) then<br />

• My.Type := CREATURE // create (move by copy)<br />

• My.Direction := TurnRight/Left (My.NeighborCrea<strong>tu</strong>re.Direction) // new direction<br />

Coupled Action<br />

In case a1 and a2 where a crea<strong>tu</strong>re can move, it changes its own type<br />

to EMPTY (case a1) and at the same time the empty cell changes its<br />

type to CREATURE (case a2).<br />

7<br />

In case b where the cell cannot move, it will <strong>tu</strong>rn only right or left.

Conflict Resolution<br />

cell in conflict<br />

(front cell)<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

• More than one crea<strong>tu</strong>re wants to move to the same cell<br />

• Result of conflict resolution in general<br />

– either no crea<strong>tu</strong>re can move, or<br />

– one crea<strong>tu</strong>re is selected to move<br />

• Implementations<br />

– 2-phase arbitration<br />

(1) check for conflict and select one crea<strong>tu</strong>re<br />

(2) the selected crea<strong>tu</strong>re will move<br />

– 1-phase arbitration (our solution, see next sli<strong>de</strong>)<br />

8

1-Phase Arbitration<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

request i<br />

grant i<br />

front<br />

cell<br />

feed-back<br />

logic<br />

• front cell contains a feed-back logic for the arbitration<br />

• evaluates the number Q of requests<br />

• if (Q>1) then grant = 0 else grant = 1<br />

• grant is computed within the current clock cycle<br />

9

Different Behaviors of a Crea<strong>tu</strong>re<br />

• Mo<strong>de</strong>led by a changdable Control Machine and a fixed Output-Machine<br />

• Control Machine implements <strong>State</strong> <strong>Algorithm</strong><br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

grant signal from neighbor in front (front cell)<br />

m<br />

0 0<br />

0 1<br />

0 2<br />

0 3<br />

0 4<br />

0 5<br />

1 0<br />

1 1<br />

1 2<br />

1 3<br />

1 4<br />

1 5<br />

1 L<br />

2 L<br />

0 L<br />

4 R<br />

5 R<br />

3 R<br />

3 Lm<br />

1 Rm<br />

5 Lm<br />

0 Rm<br />

4 Lm<br />

2 Rm<br />

s'<br />

d<br />

s<br />

v<br />

r<br />

s control state<br />

r direction<br />

d action<br />

v(r,d) new direction<br />

m crea<strong>tu</strong>re can move<br />

L/R <strong>tu</strong>rn left/R if (m=1)<br />

Lm/Rm <strong>tu</strong>rn left/R and move if (m=0)<br />

if d=1 then<br />

r:=r+1 (<strong>tu</strong>rn right)<br />

else<br />

r:=r-1 (<strong>tu</strong>rn left)<br />

10<br />

MEALY-<br />

Control-Machine<br />

MOORE-<br />

Output-Machine

Representation of a <strong>State</strong> <strong>Algorithm</strong><br />

• state/output-table state/output-graph<br />

m<br />

6-state algorithm<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

11<br />

0 0<br />

0 1<br />

0 2<br />

0 3<br />

0 4<br />

0 5<br />

1 0<br />

1 1<br />

1 2<br />

1 3<br />

1 4<br />

1 5<br />

1 L<br />

2 L<br />

0 L<br />

4 R<br />

5 R<br />

3 R<br />

3 Lm<br />

1 Rm<br />

5 Lm<br />

0 Rm<br />

4 Lm<br />

2 Rm<br />

s<br />

action<br />

d<br />

• string repesentation<br />

0 2<br />

blocked, m=0<br />

move, m=1<br />

1L2L0L4R5R3R-3Lm1Rm5Lm0Rm4Lm2Rm<br />

= 1L2L0L4R5R3R-3L1R5L0R4L2R simplified<br />

L<br />

1<br />

3 5<br />

4<br />

Rm<br />

Rm Lm Rm Lm<br />

R<br />

R<br />

Lm<br />

R<br />

L

Number of <strong>State</strong> <strong>Algorithm</strong>s<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

• M = Number of all control algorithms (Mealy state<br />

machines), represented by a state table<br />

– #s: number of states<br />

– #x: number of input values (blocked or free e.g. 2)<br />

– #y: number of actions (<strong>tu</strong>rn left or right e.g. 2)<br />

• M = (#s #y) (#s #x) (2#s) (2#s)<br />

12

Classes of <strong>State</strong> <strong>Algorithm</strong>s<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

• P (without prefix)<br />

– Each state reachable from initial state 0 is able to re<strong>tu</strong>rn to the initial state.<br />

• N (normalized)<br />

– Equivalent algorithms which only differ in their state encodings are represented<br />

in a unique form. Only the representatives are in this class.<br />

• R (irreducible)<br />

– <strong>Algorithm</strong>s in this class are true n-state algorithms which cannot be reduced to<br />

algorithms with less than n states.<br />

• V (all reachable)<br />

– All states can be reached from the initial state 0 for each algorithm in this class.<br />

• Relevant <strong>Algorithm</strong>s<br />

– Q = P ∩ N ∩ V ∩ R<br />

13

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

14<br />

N<br />

3 states, 2 inputs, 2 outputs<br />

R<br />

12 36 99 49<br />

1124 3228 8124 1348<br />

1124 3228 8124 1348<br />

1260 2148 10653 4751<br />

P<br />

all algorithms M = 46 656<br />

V

Relevant algorithms for #x = #y = 2<br />

states<br />

All algorithms<br />

Relevant<br />

#s<br />

M<br />

<strong>Algorithm</strong>s<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

2<br />

3<br />

4<br />

5<br />

6<br />

4 4 = 256<br />

6 6 = 46 656<br />

8 8 = 16 777 216<br />

10 10 = 10 * 10 9<br />

12 12 = 8.92 * 10 12<br />

108<br />

[42.2 %]<br />

8 124<br />

[17.4 %]<br />

798 384<br />

[4.8 %]<br />

98 869 740<br />

[1 %]<br />

14 762 149 668<br />

[0.2 %]<br />

15

Procedure to find the best algorithms<br />

generate next algorithm (state table)<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

∀ algorithms<br />

discard irrelevant algorithms<br />

∀ initial configurations: simulate and evaluate behavior<br />

discard alg. with poor performance<br />

store set of candidates with good performance<br />

<strong>de</strong>tailed evalutation and statistics<br />

i<strong>de</strong>ntify best algorithms<br />

test for robustness with further initital configurations<br />

FPGA Hardware<br />

Software<br />

16<br />

testing the performance with more than one crea<strong>tu</strong>re

5 Initial Configurations: The First Test Set<br />

1 2 3 4 5<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

17

Further 21 initial configurations for robustness test<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

• Robustness : crea<strong>tu</strong>re behaves also well un<strong>de</strong>r other<br />

conditions (initial cofigurations)<br />

Samples<br />

Config. 16<br />

Config. 15<br />

18

Performance of the best algorithms<br />

successful<br />

(100 % crossed)<br />

unsuccessful<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

AL<br />

GO<br />

RIT<br />

HM<br />

A6<br />

B6<br />

C6<br />

D6<br />

E6<br />

F6<br />

1<br />

2<br />

3<br />

4<br />

5<br />

26 Configuration (Test set)<br />

6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2<br />

0 1 2 3 4 5 6 7 8 9 0 1<br />

2<br />

2<br />

2<br />

3<br />

2<br />

4<br />

2<br />

5<br />

2<br />

6<br />

Success<br />

23<br />

24<br />

23<br />

22<br />

24<br />

24<br />

Crossing<br />

Perform.<br />

99.07<br />

99.92<br />

99.29<br />

98.63<br />

99.12<br />

97.94<br />

Speed<br />

.136<br />

.252<br />

.259<br />

.251<br />

.223<br />

.238<br />

G6<br />

24<br />

99.92<br />

.260<br />

x<br />

H6<br />

21<br />

98.91<br />

.169<br />

I6<br />

21<br />

98.91<br />

.193<br />

J6<br />

16<br />

78.55<br />

.299<br />

K6<br />

23<br />

99.87<br />

.268<br />

19

The two best 6-<strong>State</strong>-<strong>Algorithm</strong>s<br />

Rm<br />

Lm<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

Rm<br />

1<br />

L<br />

L<br />

R interchanged with L<br />

1<br />

R<br />

R<br />

0 2<br />

0 2<br />

L<br />

R<br />

Rm<br />

Lm<br />

Lm<br />

Lm<br />

Lm<br />

Rm<br />

R<br />

L<br />

3 5<br />

3 5<br />

R<br />

4<br />

R<br />

L<br />

4<br />

L<br />

Rm<br />

Lm<br />

Rm<br />

20<br />

<strong>Algorithm</strong> G6<br />

behaves slighty better for the 26 configs.<br />

<strong>Algorithm</strong> B6

Speed of 6-<strong>State</strong> <strong>Algorithm</strong>s for Config. 15<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

J6<br />

B6<br />

G6<br />

D6<br />

B6: 2599<br />

G6: 2592<br />

Speed <strong>de</strong>pends on algorithm<br />

and configuration<br />

Alg.<br />

A6<br />

B6<br />

C6<br />

D6<br />

E6<br />

F6<br />

G6<br />

1/speed<br />

5.9<br />

4.9<br />

5.9<br />

3.7<br />

6.4<br />

6.4<br />

4.9<br />

speed<br />

.168<br />

.205<br />

.170<br />

.271<br />

.157<br />

.156<br />

.205<br />

H6<br />

6.9<br />

.144<br />

I6<br />

6.1<br />

.162<br />

J6<br />

(2.3)<br />

(.433)<br />

J6 fast at the beginning<br />

but is not succesful<br />

21

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

22<br />

Config. 7, Alg. B6<br />

first cyclic path<br />

2 cells can not be reached<br />

second cyclic path

Several Crea<strong>tu</strong>res<br />

Initial configurations used to evaluate the behavior of several crea<strong>tu</strong>res<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

1 2 4 8 16<br />

23

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

24<br />

Generations and Speed using n Crea<strong>tu</strong>res<br />

Generations to visit all empty cells with n crea<strong>tu</strong>res<br />

33 times faster<br />

(with 16 crea<strong>tu</strong>res)

Generations and Speed using n Crea<strong>tu</strong>res<br />

Definition:<br />

Speed = empty cells / generations<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

Speed per crea<strong>tu</strong>re = Speed / n<br />

Four crea<strong>tu</strong>res with algorithm A6 work relatively faster<br />

than one crea<strong>tu</strong>re with the best algorithm J6<br />

(0.52 0.53)<br />

25

Conclusion<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

• Crea<strong>tu</strong>re's Exploration<br />

Problem was mo<strong>de</strong>led by CA<br />

• Conflicts are solved using a<br />

new 1-phase arbitration logic<br />

• Behavior of a crea<strong>tu</strong>re is<br />

mo<strong>de</strong>led by a Mealy-Control-<br />

Machine and an Output-<br />

Machine<br />

• <strong>State</strong> <strong>Algorithm</strong>s were or<strong>de</strong>red<br />

into classes.<br />

• Relevant algorithms<br />

– 6 states:<br />

14 762 149 668 [0,2 %]<br />

• Procedure to find best alg.<br />

1. hardware computes<br />

candidates<br />

2. software selects best alg. and<br />

tests for robustness<br />

3. software tests behavior of<br />

several crea<strong>tu</strong>res<br />

• Several crea<strong>tu</strong>res can perform<br />

the work more efficiently (in<br />

terms of speed per crea<strong>tu</strong>re)<br />

than only one.<br />

26

Hardware Platform<br />

Darmstadt University of Technology<br />

Computer Architec<strong>tu</strong>re Group<br />

• FPGA Altera Cyclone<br />

EP1C20F324C7<br />

• Altera Quar<strong>tu</strong>s II Tools<br />

– VERILOG FPGA-Logic<br />

• USB Module<br />

– connected to a PC<br />

– for control and data<br />

communication<br />

• Computation in Hardware<br />

– algorithm search, simulation and<br />

evaluation (5 configs in parallel)<br />

– Hardware/Software Speed-Up:<br />

100 to 10 000 <strong>de</strong>pending on<br />

FPGA<br />

27