Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>STM32W108C8</strong><br />

Serial interfaces<br />

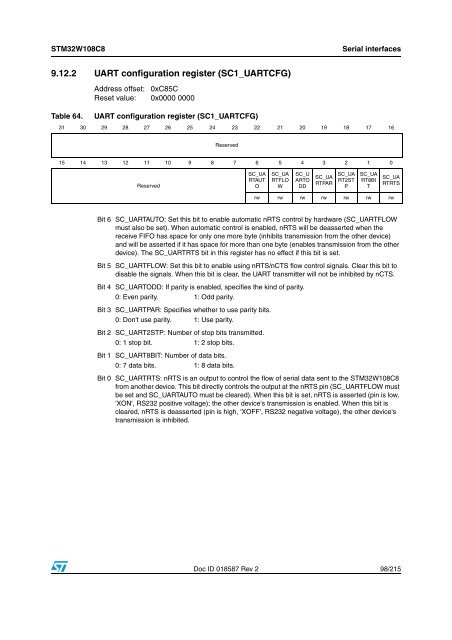

9.12.2 UART configuration register (SC1_UARTCFG)<br />

Table 64.<br />

Address offset: 0xC85C<br />

Reset value: 0x0000 0000<br />

UART configuration register (SC1_UARTCFG)<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16<br />

Reserved<br />

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br />

Reserved<br />

SC_UA<br />

RTAUT<br />

O<br />

SC_UA<br />

RTFLO<br />

W<br />

SC_U<br />

ARTO<br />

DD<br />

SC_UA<br />

RTPAR<br />

SC_UA<br />

RT2ST<br />

P<br />

SC_UA<br />

RT8BI<br />

T<br />

SC_UA<br />

RTRTS<br />

rw rw rw rw rw rw rw<br />

Bit 6 SC_UARTAUTO: Set this bit to enable automatic nRTS control by hardware (SC_UARTFLOW<br />

must also be set). When automatic control is enabled, nRTS will be deasserted when the<br />

receive FIFO has space for only one more byte (inhibits transmission from the other device)<br />

and will be asserted if it has space for more than one byte (enables transmission from the other<br />

device). The SC_UARTRTS bit in this register has no effect if this bit is set.<br />

Bit 5 SC_UARTFLOW: Set this bit to enable using nRTS/nCTS flow control signals. Clear this bit to<br />

disable the signals. When this bit is clear, the UART transmitter will not be inhibited by nCTS.<br />

Bit 4 SC_UARTODD: If parity is enabled, specifies the kind of parity.<br />

0: Even parity. 1: Odd parity.<br />

Bit 3 SC_UARTPAR: Specifies whether to use parity bits.<br />

0: Don't use parity. 1: Use parity.<br />

Bit 2 SC_UART2STP: Number of stop bits transmitted.<br />

0: 1 stop bit. 1: 2 stop bits.<br />

Bit 1 SC_UART8BIT: Number of data bits.<br />

0: 7 data bits. 1: 8 data bits.<br />

Bit 0 SC_UARTRTS: nRTS is an output to control the flow of serial data sent to the <strong>STM32W108C8</strong><br />

from another device. This bit directly controls the output at the nRTS pin (SC_UARTFLOW must<br />

be set and SC_UARTAUTO must be cleared). When this bit is set, nRTS is asserted (pin is low,<br />

'XON', RS232 positive voltage); the other device's transmission is enabled. When this bit is<br />

cleared, nRTS is deasserted (pin is high, 'XOFF', RS232 negative voltage), the other device's<br />

transmission is inhibited.<br />

Doc ID 018587 Rev 2 98/215