Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Serial interfaces<br />

<strong>STM32W108C8</strong><br />

9.12 Universal asynchronous receiver / transmitter (UART)<br />

registers<br />

Refer to the SPI Master mode section for a description of the SCx_DATA register.<br />

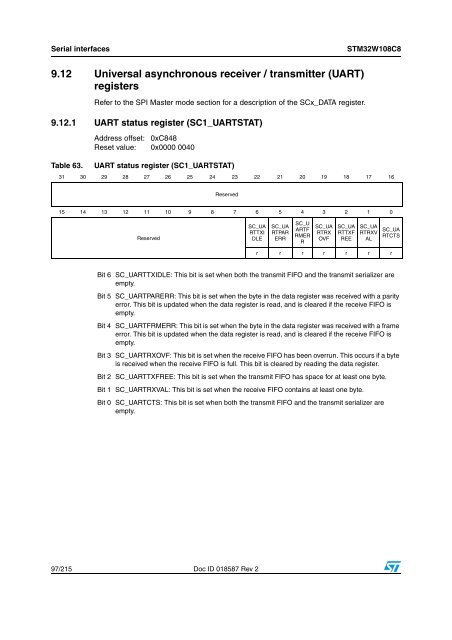

9.12.1 UART status register (SC1_UARTSTAT)<br />

Table 63.<br />

Address offset: 0xC848<br />

Reset value: 0x0000 0040<br />

UART status register (SC1_UARTSTAT)<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16<br />

Reserved<br />

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br />

Reserved<br />

SC_UA<br />

RTTXI<br />

DLE<br />

SC_UA<br />

RTPAR<br />

ERR<br />

SC_U<br />

ARTF<br />

RMER<br />

R<br />

SC_UA<br />

RTRX<br />

OVF<br />

SC_UA<br />

RTTXF<br />

REE<br />

SC_UA<br />

RTRXV<br />

AL<br />

SC_UA<br />

RTCTS<br />

r r r r r r r<br />

Bit 6 SC_UARTTXIDLE: This bit is set when both the transmit FIFO and the transmit serializer are<br />

empty.<br />

Bit 5 SC_UARTPARERR: This bit is set when the byte in the data register was received with a parity<br />

error. This bit is updated when the data register is read, and is cleared if the receive FIFO is<br />

empty.<br />

Bit 4 SC_UARTFRMERR: This bit is set when the byte in the data register was received with a frame<br />

error. This bit is updated when the data register is read, and is cleared if the receive FIFO is<br />

empty.<br />

Bit 3 SC_UARTRXOVF: This bit is set when the receive FIFO has been overrun. This occurs if a byte<br />

is received when the receive FIFO is full. This bit is cleared by reading the data register.<br />

Bit 2 SC_UARTTXFREE: This bit is set when the transmit FIFO has space for at least one byte.<br />

Bit 1 SC_UARTRXVAL: This bit is set when the receive FIFO contains at least one byte.<br />

Bit 0 SC_UARTCTS: This bit is set when both the transmit FIFO and the transmit serializer are<br />

empty.<br />

97/215 Doc ID 018587 Rev 2