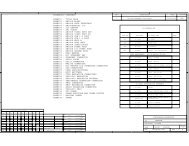

5 5 4 4 3 3 2 2 1 1 <strong>Spectrum</strong> <strong>Digital</strong>, Inc NOTE: DIMENSIONS AND LOCATIONS OF THESE CONNECTORS MUST MEET SPECIFICATION FOR INTERFACE MODULES D D P1 P2 1 2 1 2 MMC1_DATA0 2 3 4 2,17 UART_RTS 3 4 MMC1_DATA1 2 5 6 RTC_CLKOUT 5 6 MMC1_DATA2 2 V3.3 7 8 I2S1_DX_CC 2 2,17 UART_RX 7 8 MMC1_DATA3 2 9 10 I2S1_RX_CC 2 GPIO4 C 2,17 UART_TX 9 10 GPIO4 2 I2S1_FS_CC 11 12 C GPIO5 2,14,15,17,18,19 I2C_SDA 11 12 GPIO5 2 GPIO12 13 14 2,14,15,17,18,19 I2C_SCL 13 14 SPI_ALT_CS1 2 GPIO14_CC 15 16 MMC1_CLK 15 16 SPI_ALT_CLK 2 I2S1_CLK_CC 17 18 UART_CTS 2,17 MMC1_CMD 17 18 SPI_ALT_DX 2 19 20 GPIO13 2 19 20 SPI_ALT_RX 2 HEADER 10X2 HEADER 10X2 B B A SPECTRUM DIGITAL INCORPORATED A Title: <strong>TMS320C5515</strong> EVALUATION MODULE Page Contents: CC BOARD INTERFACE Revision: Size: B DWG NO 512702-0001 A Date: Sheet o f Monday, February 01, 2010 5 20 2 2 2 2 2 2 2 A-6 <strong>TMS320C5515</strong> <strong>EVM</strong> Technical Reference

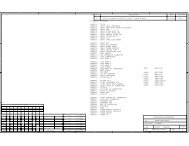

1 2 3 4 5 1 2 3 4 5 <strong>Spectrum</strong> <strong>Digital</strong>, Inc D RN5 RPACK8-22 U13C D 7,9 7,8,9 8,9 7,9 RN7 RPACK8-22 CPU_A5 D1 CPU_SDRAS R151 0 SDRAS A2 CPU_A2 CPU_A4 EM_A[5] SDRASn A6 CPU_SDCAS SDCAS SDRAS 7 C 7,9 A2 8 9 C1 R152 22 C A5 CPU_A5 CPU_A3 EM_A[4] SDCASn B4 SDCAS 7 7,9 A5 7 10 D2 A3 CPU_A3 CPU_A2 EM_A[3] 7,9 A3 6 11 E1 CPU_SDCLK R159 22 SDCLK A4 CPU_A4 CPU_A1 EM_A[2] EM_SDCLK M3 SDCLK 7 7,9 A4 5 12 C2 7,9 A0 A0 CPU_A0 CPU_A0 EM_A[1] 4 13 B2 CPU_SDCKE SDCKE A1 CPU_A1 CPU_BA1 EM_A[0] SDCKE N2 R158 22 SDCKE 7 7,9 A1 3 14 B1 7,9 BA0 BA0 2 15 CPU_BA0 CPU_BA0 EM_BA[1] A1 CPU_SDCE0 R150 22 SD_CEXn BA1 CPU_BA1 EM_BA[0] SD_CE0n B3 SD_CEXn 7 7,9 BA1 1 16 R283 NO-POP SD_CE1n A4 CPU_EM_CS2n R153 22 EM_CS2n EM_CS2n C5 CPU_EM_CS3n EM_CS2n 9 R17 R15 EM_CS3n M4 CPU_EM_CS4n R154 22 EM_CS4n 10K 10K EM_CS4n C3 CPU_EM_CS5n EM_CS4n 8 DVDDEMIF EM_CS5n A3 B B A SPECTRUM DIGITAL INCORPORATED A 9 9 9 9 9 9 9 9 8 8 9 D15 A15 CPU_A15 CPU_A20 EM_D[15] J4 D15 7,9 A15 7 10 J3 D14 A14 CPU_A14 CPU_A19 EM_A[20]/GP[26] EM_D[14] K3 D14 7,9 A14 6 11 G4 D13 A10 CPU_A10 CPU_A18 EM_A[19]/GP[25] EM_D[13] K4 D13 7,9 A10 5 12 G2 D12 D12 7,9 A13 CPU_A13 CPU_A17 EM_A[18]/GP[24] EM_D[12] L3 A13 4 13 F2 D11 D11 7,9 A11 A11 CPU_A11 CPU_A16 EM_A[17]/GP[23] EM_D[11] C4 3 14 E2 D10 D10 7,9 A12 A12 CPU_A12 CPU_A15 EM_A[16]/GP[22] EM_D[10] D3 2 15 N1 D9 D9 7,9 A9 A9 CPU_A9 CPU_A14 EM_A[15]/GP[21] EM_D[9] F4 1 16 M1 D8 EM_A[14] EM_D[8] E3 D8 7,9 7,9 9 7,9 7,9 RN6 RPACK8-22 A8 A8 8 9 CPU_A8 CPU_A13 L1 D7 A20 CPU_A20 CPU_A12 EM_A[13] EM_D[7] H3 D7 7,8,9 A20 7 10 K1 D6 A7 CPU_A7 CPU_A11 EM_A[12]/(CLE) EM_D[6] K5 D6 7,8,9 A7 6 11 K2 D5 A19 CPU_A19 CPU_A10 EM_A[11]/(ALE) EM_D[5] M2 D5 7,8,9 A19 5 12 L2 D4 D4 7,8,9 A18 A18 CPU_A18 CPU_A9 EM_A[10] EM_D[4] L4 4 13 J2 D3 D3 7,8,9 A17 A17 3 CPU_A17 CPU_A8 EM_A[9] EM_D[3] D4 14 J1 D2 D2 7,8,9 A6 A6 2 15 CPU_A6 CPU_A7 EM_A[8] EM_D[2] F3 H2 D1 D1 7,8,9 A16 A16 1 16 CPU_A16 CPU_A6 EM_A[7] EM_D[1] E5 F1 D0 EM_A[6] EM_D[0] G3 D0 7,8,9 CPU_DQM1 R119 22 DQM1 DQM1 7 EM_DQM1 P1 CPU_DQM0 R118 22 DQM0 EM_DQM0 B5 DQM0 7 CPU_RnW EM_WAIT2 EM_R/Wn B6 EM_WAIT2 D5 EM_WAIT3 EM_WAIT2 K6 CPU_WE R156 22 WE EM_WAIT4 EM_WAIT3 EM_WEn H1 WE 7,8,9 EM_WAIT4 G1 EM_WAIT5 EM_WAIT4 H4 CPU_OE OE EM_WAIT5 EM_OEn E4 R155 22 OE 8,9 <strong>TMS320C5515</strong> Title: <strong>TMS320C5515</strong> EVALUATION MODULE Page Contents: <strong>TMS320C5515</strong> EMIF Revision: Size: B DWG NO 512702-0001 A Date: Sheet o f Monday, February 01, 2010 6 20 A-7

- Page 1:

TMS320C5515 Evaluation Module (EVM)

- Page 4 and 5:

IMPORTANT NOTICE Spectrum Digital,

- Page 6 and 7: 2.4 C5515 EVM Switches . . . . . .

- Page 8 and 9: Table 1: Hardware History Revision

- Page 10 and 11: Spectrum Digital, Inc 1.1 Key Featu

- Page 12 and 13: Spectrum Digital, Inc 1.4 C5515 GPI

- Page 14 and 15: Spectrum Digital, Inc Table 1: C551

- Page 16 and 17: Spectrum Digital, Inc 1.6 C5515 I 2

- Page 18 and 19: Spectrum Digital, Inc Topic Page 2.

- Page 20 and 21: Spectrum Digital, Inc Figure 2-2 sh

- Page 22 and 23: Spectrum Digital, Inc 2.2.1 J1, RS-

- Page 24 and 25: Spectrum Digital, Inc 2.2.4 J4, Hea

- Page 26 and 27: Spectrum Digital, Inc 2.2.8 J8, Ext

- Page 28 and 29: Spectrum Digital, Inc 2.2.12 J12, S

- Page 30 and 31: Spectrum Digital, Inc 2.2.15 J15, M

- Page 32 and 33: Spectrum Digital, Inc 2.2.18 J19, D

- Page 34 and 35: Spectrum Digital, Inc 2.2.21.2 P2,

- Page 36 and 37: Spectrum Digital, Inc 2.4.3 SW4, LD

- Page 38 and 39: Spectrum Digital, Inc 2.5 Jumpers T

- Page 40 and 41: Spectrum Digital, Inc The factory i

- Page 42 and 43: Spectrum Digital, Inc 2.5.1.3 JP5,

- Page 44 and 45: Spectrum Digital, Inc 2.5.1.7 JP39,

- Page 46 and 47: Spectrum Digital, Inc The remaining

- Page 48 and 49: Spectrum Digital, Inc Figure below

- Page 50 and 51: Spectrum Digital, Inc The table bel

- Page 52 and 53: 1 2 4 5 5 6 7 8 9 A A 4 4 3 3 A 2 2

- Page 54 and 55: 1 2 3 4 5 1 2 3 4 5 Spectrum Digita

- Page 58 and 59: 5 5 4 4 3 3 2 2 1 1 Spectrum Digita

- Page 60 and 61: 5 5 4 4 3 3 2 2 1 1 Spectrum Digita

- Page 62 and 63: 5 5 4 4 3 3 2 2 1 1 Spectrum Digita

- Page 64 and 65: 5 5 4 4 3 3 2 2 1 1 Spectrum Digita

- Page 66 and 67: 5 5 4 4 3 3 2 2 1 1 Spectrum Digita

- Page 68 and 69: 5 5 4 4 3 3 2 2 1 1 Spectrum Digita

- Page 70 and 71: 5 5 + 0 4 4 3 3 0 0 2 2 0 0 0 0 1 1

- Page 72 and 73: Spectrum Digital, Inc A-22 TMS320C5

- Page 74: Spectrum Digital, Inc THIS DRAWING