Intel PXA250 and PXA210 Applications Processors

Intel PXA250 and PXA210 Applications Processors

Intel PXA250 and PXA210 Applications Processors

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

SA-1110/<strong>Applications</strong> Processor Migration<br />

— <strong>Intel</strong>® XScale microarchitecture<br />

—Debugging<br />

- Cache attributes<br />

- Other Features<br />

- Conclusion<br />

A.1 SA-1110 Hardware Migration Issues<br />

A.1.1<br />

Hardware Compatibility<br />

The majority of the features provided in the SA-1110 are also provided in the <strong>PXA250</strong> applications<br />

processor. However, with the additional functionality of the <strong>PXA250</strong> applications processor, the<br />

two devices are not pin compatible <strong>and</strong> cannot occupy the same socket.<br />

There has been an effort to ensure Companion Devices that take advantage of SA-1110 memory<br />

interface access works with the <strong>PXA250</strong> applications processor. The memory controls for taking<br />

over the memory bus such as those exercised by the SA-1111, are included in the <strong>PXA250</strong><br />

applications processor memory bus interface however, there are some issues.<br />

One difference in particular is the way <strong>PXA250</strong> applications processor toggles the A1 <strong>and</strong> A0<br />

address lines. The SA-1110 toggled A1 <strong>and</strong> A0 regardless of the size of the data bus. With<br />

<strong>PXA250</strong>, if the data bus is set to 16-bit, then A0 does not toggle <strong>and</strong> if the data bus is set to 32-bit,<br />

then neither A1 nor A0 toggles.<br />

There is a big difference in manufacturing technology between the SA-1110 <strong>and</strong> the <strong>PXA250</strong><br />

applications processors. The most significant change being from a 0.35 micron CMOS technology<br />

to a finer lithography of 0.18 microns. Aside from a potential impact to signal edge rates this<br />

allows for lower applications processor voltage operation.<br />

A.1.2<br />

Signal Changes<br />

There are two pins that control SA-1110 boot-up:<br />

• ROM select pin that selects a 16 or 32-bit interface<br />

• Synchronous Mask ROM enable pin that selects a synchronous or asynchronous ROM access<br />

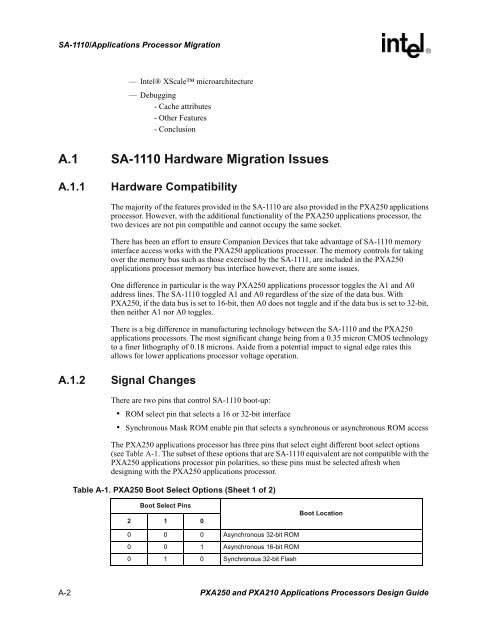

The <strong>PXA250</strong> applications processor has three pins that select eight different boot select options<br />

(see Table A-1. The subset of these options that are SA-1110 equivalent are not compatible with the<br />

<strong>PXA250</strong> applications processor pin polarities, so these pins must be selected afresh when<br />

designing with the <strong>PXA250</strong> applications processor.<br />

Table A-1. <strong>PXA250</strong> Boot Select Options (Sheet 1 of 2)<br />

Boot Select Pins<br />

2 1 0<br />

Boot Location<br />

0 0 0 Asynchronous 32-bit ROM<br />

0 0 1 Asynchronous 16-bit ROM<br />

0 1 0 Synchronous 32-bit Flash<br />

A-2 <strong>PXA250</strong> <strong>and</strong> <strong>PXA210</strong> <strong>Applications</strong> <strong>Processors</strong> Design Guide