Intel PXA250 and PXA210 Applications Processors

Intel PXA250 and PXA210 Applications Processors

Intel PXA250 and PXA210 Applications Processors

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

JTAG/Debug Port 9<br />

9.1 Description<br />

The JTAG/Debug port is essentially several shift registers, with the destination controlled by the<br />

TMS pin <strong>and</strong> data I/O with TDI/TDO. nTRST provides initialization of the test logic. JTAG is<br />

testable via the IEEE 1149.1. Many use JTAG to control the address/data bus for Flash<br />

programming. JTAG is also a hardware debug port.<br />

9.2 Schematics<br />

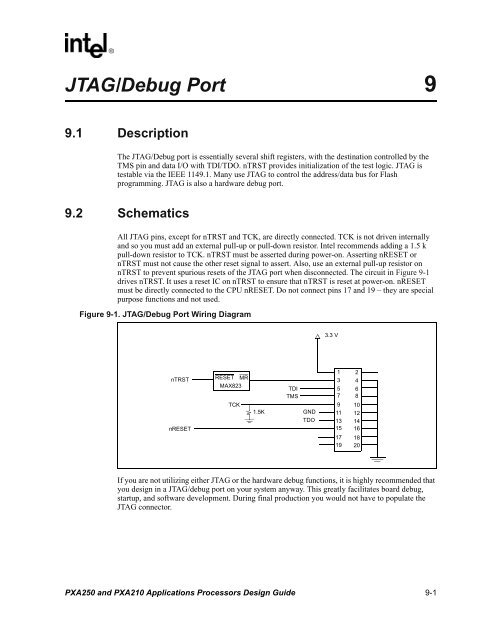

All JTAG pins, except for nTRST <strong>and</strong> TCK, are directly connected. TCK is not driven internally<br />

<strong>and</strong> so you must add an external pull-up or pull-down resistor. <strong>Intel</strong> recommends adding a 1.5 k<br />

pull-down resistor to TCK. nTRST must be asserted during power-on. Asserting nRESET or<br />

nTRST must not cause the other reset signal to assert. Also, use an external pull-up resistor on<br />

nTRST to prevent spurious resets of the JTAG port when disconnected. The circuit in Figure 9-1<br />

drives nTRST. It uses a reset IC on nTRST to ensure that nTRST is reset at power-on. nRESET<br />

must be directly connected to the CPU nRESET. Do not connect pins 17 <strong>and</strong> 19 – they are special<br />

purpose functions <strong>and</strong> not used.<br />

Figure 9-1. JTAG/Debug Port Wiring Diagram<br />

3.3 V<br />

nTRST<br />

RESET MR<br />

MAX823<br />

TDI<br />

TMS<br />

1<br />

3<br />

5<br />

7<br />

2<br />

4<br />

6<br />

8<br />

nRESET<br />

TCK<br />

1.5K<br />

GND<br />

TDO<br />

9<br />

11<br />

13<br />

15<br />

10<br />

12<br />

14<br />

16<br />

17<br />

19<br />

18<br />

20<br />

If you are not utilizing either JTAG or the hardware debug functions, it is highly recommended that<br />

you design in a JTAG/debug port on your system anyway. This greatly facilitates board debug,<br />

startup, <strong>and</strong> software development. During final production you would not have to populate the<br />

JTAG connector.<br />

<strong>PXA250</strong> <strong>and</strong> <strong>PXA210</strong> <strong>Applications</strong> <strong>Processors</strong> Design Guide 9-1