Direct Torque Control with Space Vector Modulation (DTC-SVM) of ...

Direct Torque Control with Space Vector Modulation (DTC-SVM) of ...

Direct Torque Control with Space Vector Modulation (DTC-SVM) of ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

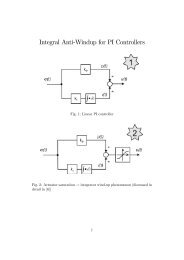

Voltage source PWM inverter for PMSM supply<br />

As a consequence when the phase current I sA<br />

is positive, the output voltage is reduced,<br />

and when the current I<br />

sA<br />

is negative the output voltage is increased (see Fig. 3.11).<br />

U0<br />

I<br />

sA<br />

> 0<br />

ideal voltage<br />

real voltage<br />

U I < 0<br />

0<br />

sA<br />

U DC<br />

2<br />

U DC<br />

2<br />

−U DC<br />

2<br />

deacresing<br />

−U DC<br />

2<br />

increasing<br />

Figure 3.11 Dead time effect on the inverter output voltage: (fat line real voltage, doted line<br />

ideal voltage).<br />

Voltage drop across power devices<br />

In real voltage source inverter power switches do not conduct ideally. When they are<br />

conducting the voltage across them is not zero and equal the voltage drop on the<br />

conducted transistor V T<br />

. Also in blocking mode the power switches have voltage drop<br />

on the conducted diode V D<br />

. More details about real IGBT module you can find in<br />

Appendices.<br />

The voltage drop across the power devices is dependent on the direction <strong>of</strong> the phase<br />

current. It has influence on the output voltage, especially at low speed operation <strong>of</strong><br />

motor and high load current [17,20,27,30]. Fig. 3.12 shows the voltage drop influence<br />

on the output voltage. Also shows that the output voltage is asymmetric (<strong>with</strong> <strong>of</strong>fset)<br />

and the voltage drop decreases the output voltage when the phase current is positive and<br />

increases the output voltage when the phase current is negative.<br />

U 0<br />

I > 0<br />

sA<br />

U 0<br />

I < 0<br />

sA<br />

U DC<br />

2<br />

V T<br />

U DC<br />

2<br />

V D<br />

V D<br />

V T<br />

−U DC<br />

2<br />

−U DC<br />

2<br />

Figure 3.12 Output voltage in voltage source inverter due to voltage drop across the power<br />

devices a) for I<br />

sA<br />

> 0 , b) I<br />

sA<br />

< 0 (fat line real voltage, doted line ideal voltage).<br />

The influence <strong>of</strong> dead time effect and voltage drop across power devices on the output<br />

voltage from inverter is illustrated in block diagram (Fig. 3.13). The ideal reference<br />

*<br />

voltage components in stationary reference frame ( U α<br />

,<br />

_ ideal<br />

*<br />

U β _ ideal<br />

) are equal real<br />

40

![[TCP] Opis układu - Instytut Sterowania i Elektroniki Przemysłowej ...](https://img.yumpu.com/23535443/1/184x260/tcp-opis-ukladu-instytut-sterowania-i-elektroniki-przemyslowej-.jpg?quality=85)