IRFP4568PBF Datasheet

IRFP4568PBF Datasheet

IRFP4568PBF Datasheet

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

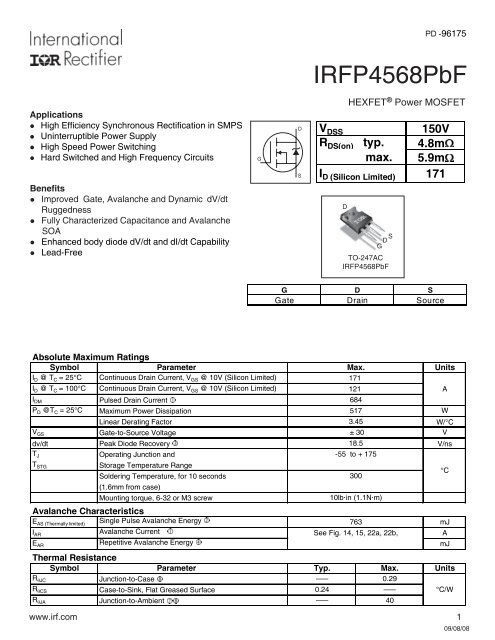

PD -96175<br />

IRFP4568PbF<br />

Applications<br />

l High Efficiency Synchronous Rectification in SMPS<br />

l Uninterruptible Power Supply<br />

l High Speed Power Switching<br />

l Hard Switched and High Frequency Circuits<br />

Benefits<br />

l Improved Gate, Avalanche and Dynamic dV/dt<br />

Ruggedness<br />

l Fully Characterized Capacitance and Avalanche<br />

SOA<br />

l Enhanced body diode dV/dt and dI/dt Capability<br />

l Lead-Free<br />

G<br />

D<br />

S<br />

V DSS<br />

HEXFET ® Power MOSFET<br />

150V<br />

R DS(on) typ.<br />

max.<br />

4.8m:<br />

5.9m:<br />

I D (Silicon Limited) 171<br />

D<br />

S<br />

D<br />

G<br />

TO-247AC<br />

IRFP4568PbF<br />

G D S<br />

Gate Drain Source<br />

Absolute Maximum Ratings<br />

Symbol Parameter Max.<br />

Units<br />

I D @ T C = 25°C Continuous Drain Current, V GS @ 10V (Silicon Limited)<br />

171<br />

I D @ T C = 100°C Continuous Drain Current, V GS @ 10V (Silicon Limited)<br />

121<br />

A<br />

I DM<br />

Pulsed Drain Current c<br />

684<br />

P D @T C = 25°C Maximum Power Dissipation 517<br />

W<br />

Linear Derating Factor<br />

3.45<br />

W/°C<br />

V GS Gate-to-Source Voltage ± 30<br />

V<br />

dv/dt Peak Diode Recovery e 18.5<br />

V/ns<br />

T J<br />

Operating Junction and<br />

-55 to + 175<br />

T STG<br />

Storage Temperature Range<br />

Soldering Temperature, for 10 seconds<br />

300<br />

°C<br />

(1.6mm from case)<br />

Mounting torque, 6-32 or M3 screw<br />

10lbxin (1.1Nxm)<br />

Avalanche Characteristics<br />

E AS (Thermally limited)<br />

Single Pulse Avalanche Energy d 763<br />

mJ<br />

I AR<br />

Avalanche Currentc See Fig. 14, 15, 22a, 22b,<br />

A<br />

E AR<br />

Repetitive Avalanche Energy f mJ<br />

Thermal Resistance<br />

Symbol Parameter Typ. Max. Units<br />

R θJC Junction-to-Case j ––– 0.29<br />

R θCS Case-to-Sink, Flat Greased Surface 0.24 –––<br />

R θJA Junction-to-Ambient ij ––– 40<br />

www.irf.com 1<br />

°C/W<br />

09/08/08

IRFP4568PbF<br />

Static @ T J = 25°C (unless otherwise specified)<br />

Symbol Parameter Min. Typ. Max. Units<br />

V (BR)DSS Drain-to-Source Breakdown Voltage 150 ––– ––– V<br />

∆V (BR)DSS /∆T J Breakdown Voltage Temp. Coefficient ––– 0.17 ––– V/°C<br />

R DS(on) Static Drain-to-Source On-Resistance ––– 4.8 5.9 mΩ<br />

V GS(th) Gate Threshold Voltage 3.0 ––– 5.0 V<br />

I DSS<br />

I GSS<br />

Drain-to-Source Leakage Current<br />

Gate-to-Source Forward Leakage<br />

–––<br />

–––<br />

–––<br />

–––<br />

20<br />

100<br />

Gate-to-Source Reverse Leakage<br />

–––<br />

–––<br />

–––<br />

–––<br />

250<br />

-100<br />

µA<br />

nA<br />

R G Internal Gate Resistance ––– 1.0 ––– Ω<br />

Dynamic @ T J = 25°C (unless otherwise specified)<br />

Symbol Parameter Min. Typ. Max. Units<br />

Conditions<br />

gfs Forward Transconductance 162 ––– ––– S V DS = 50V, I D = 103A<br />

Q g Total Gate Charge ––– 151 227 I D = 103A<br />

Q gs Gate-to-Source Charge ––– 52 –––<br />

Q gd Gate-to-Drain ("Miller") Charge ––– 55 –––<br />

Q sync Total Gate Charge Sync. (Q g - Q gd ) ––– 96 –––<br />

t d(on) Turn-On Delay Time ––– 27 –––<br />

t r Rise Time ––– 119 –––<br />

t d(off) Turn-Off Delay Time ––– 47 –––<br />

t f Fall Time ––– 84 –––<br />

C iss Input Capacitance ––– 10470 –––<br />

C oss Output Capacitance ––– 977 –––<br />

C rss Reverse Transfer Capacitance ––– 203 –––<br />

C oss eff. (ER) Effective Output Capacitance (Energy Related) h ––– 897 –––<br />

C oss eff. (TR) Effective Output Capacitance (Time Related)g ––– 1272 –––<br />

Diode Characteristics<br />

Symbol Parameter Min. Typ. Max. Units<br />

Conditions<br />

I S<br />

Continuous Source Current<br />

MOSFET symbol<br />

D<br />

––– ––– 171 A<br />

(Body Diode)<br />

showing the<br />

I SM<br />

Pulsed Source Current<br />

integral reverse<br />

G<br />

––– ––– 684 A<br />

(Body Diode)c<br />

S<br />

p-n junction diode.<br />

V SD Diode Forward Voltage ––– ––– 1.3 V T J = 25°C, I S = 103A, V GS = 0V f<br />

t rr Reverse Recovery Time ––– 110 ––– T J = 25°C V R = 100V,<br />

ns<br />

––– 133 ––– T J = 125°C I F = 103A<br />

Q rr Reverse Recovery Charge ––– 515 ––– T J = 25°C di/dt = 100A/µs f<br />

nC<br />

––– 758 ––– T J = 125°C<br />

I RRM Reverse Recovery Current ––– 8.8 ––– A T J = 25°C<br />

t on Forward Turn-On Time Intrinsic turn-on time is negligible (turn-on is dominated by LS+LD)<br />

nC<br />

ns<br />

pF<br />

Conditions<br />

V GS = 0V, I D = 250µA<br />

Reference to 25°C, I D = 5mAc<br />

V GS = 10V, I D = 103A f<br />

V DS = V GS , I D = 250µA<br />

V DS =150V, V GS = 0V<br />

V DS = 150V, V GS = 0V, T J = 125°C<br />

V GS = 20V<br />

V GS = -20V<br />

V DS = 75V<br />

V GS = 10V f<br />

I D = 103A, V DS =0V, V GS = 10V f<br />

V DD = 98V<br />

I D =103A<br />

R G =1.0Ω<br />

V GS = 10V f<br />

V GS = 0V<br />

V DS = 50V<br />

ƒ = 1.0MHz, (See Fig 5)<br />

V GS = 0V, V DS = 0V to 120V h(SeeFig.11)<br />

V GS = 0V, V DS = 0V to 120V g<br />

Notes:<br />

Repetitive rating; pulse width limited by max. junction<br />

temperature.<br />

‚ Limited by T Jmax , starting T J = 25°C, L = 0.144mH<br />

R G = 25Ω, I AS = 103A, V GS =10V. Part not recommended for use<br />

above this value.<br />

ƒ I SD ≤ 103A, di/dt ≤ 360A/µs, V DD ≤ V (BR)DSS , T J ≤ 175°C.<br />

„ Pulse width ≤ 400µs; duty cycle ≤ 2%.<br />

… C oss eff. (TR) is a fixed capacitance that gives the same charging time<br />

as C oss while V DS is rising from 0 to 80% V DSS .<br />

† C oss eff. (ER) is a fixed capacitance that gives the same energy as<br />

C oss while V DS is rising from 0 to 80% V DSS .<br />

‡ When mounted on 1" square PCB (FR-4 or G-10 Material). For recom<br />

mended footprint and soldering techniques refer to application note #AN-994.<br />

ˆ R θ is measured at T J approximately 90°C.<br />

2 www.irf.com

C, Capacitance (pF)<br />

I D , Drain-to-Source Current (A)<br />

I D , Drain-to-Source Current (A)<br />

V GS , Gate-to-Source Voltage (V)<br />

R DS(on) , Drain-to-Source On Resistance<br />

I D , Drain-to-Source Current (A)<br />

(Normalized)<br />

IRFP4568PbF<br />

1000<br />

100<br />

10<br />

VGS<br />

TOP 15V<br />

10V<br />

8.0V<br />

7.0V<br />

6.0V<br />

5.5V<br />

5.0V<br />

BOTTOM 4.5V<br />

1000<br />

100<br />

VGS<br />

TOP 15V<br />

10V<br />

8.0V<br />

7.0V<br />

6.0V<br />

5.5V<br />

5.0V<br />

BOTTOM 4.5V<br />

1<br />

0.1<br />

≤60µs PULSE WIDTH<br />

Tj = 25°C<br />

4.5V<br />

0.01<br />

0.1 1 10 100<br />

V DS , Drain-to-Source Voltage (V)<br />

10<br />

4.5V<br />

≤60µs PULSE WIDTH<br />

Tj = 175°C<br />

1<br />

0.1 1 10 100<br />

V DS , Drain-to-Source Voltage (V)<br />

Fig 1. Typical Output Characteristics<br />

Fig 2. Typical Output Characteristics<br />

1000<br />

100<br />

T J = 175°C<br />

3.0<br />

2.5<br />

I D = 103A<br />

V GS = 10V<br />

10<br />

T J = 25°C<br />

2.0<br />

1.5<br />

1<br />

V DS = 50V<br />

≤60µs PULSE WIDTH<br />

0.1<br />

3 4 5 6 7 8 9<br />

V GS , Gate-to-Source Voltage (V)<br />

Fig 3. Typical Transfer Characteristics<br />

1.0<br />

0.5<br />

-60 -40 -20 0 20 40 60 80 100120140160180<br />

T J , Junction Temperature (°C)<br />

Fig 4. Normalized On-Resistance vs. Temperature<br />

1000000<br />

100000<br />

10000<br />

V GS = 0V, f = 1 MHZ<br />

C iss<br />

= C gs<br />

+ C gd<br />

, C ds<br />

SHORTED<br />

C rss<br />

= C gd<br />

C oss<br />

= C ds<br />

+ C gd<br />

C iss<br />

0 50 100 150 200<br />

14.0<br />

12.0<br />

10.0<br />

8.0<br />

I D = 103A<br />

V DS = 120V<br />

V DS = 75V<br />

VDS= 30V<br />

1000<br />

100<br />

C oss<br />

C rss<br />

6.0<br />

4.0<br />

2.0<br />

10<br />

0.0<br />

1 10 100 1000<br />

V DS , Drain-to-Source Voltage (V)<br />

Q G , Total Gate Charge (nC)<br />

Fig 5. Typical Capacitance vs. Drain-to-Source Voltage Fig 6. Typical Gate Charge vs. Gate-to-Source Voltage<br />

www.irf.com 3

Drain Current (A)<br />

I D ,<br />

I SD , Reverse Drain Current (A)<br />

Energy (µJ)<br />

E AS , Single Pulse Avalanche Energy (mJ)<br />

I D , Drain-to-Source Current (A)<br />

Drain-to-Source Breakdown Voltage (V)<br />

V (BR)DSS ,<br />

IRFP4568PbF<br />

1000<br />

100<br />

T J = 175°C<br />

T J = 25°C<br />

10000<br />

1000<br />

100<br />

OPERATION IN THIS AREA<br />

LIMITED BY R DS (on)<br />

100µsec<br />

1msec<br />

10<br />

DC<br />

10<br />

10msec<br />

V GS = 0V<br />

1<br />

Tc = 25°C<br />

Tj = 175°C<br />

Single Pulse<br />

1.0<br />

0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8<br />

V SD , Source-to-Drain Voltage (V)<br />

Fig 7. Typical Source-Drain Diode<br />

Forward Voltage<br />

0.1<br />

0.1 1 10 100 1000<br />

V DS , Drain-to-Source Voltage (V)<br />

Fig 8. Maximum Safe Operating Area<br />

180<br />

160<br />

190<br />

185<br />

Id = 5mA<br />

140<br />

120<br />

100<br />

80<br />

60<br />

180<br />

175<br />

170<br />

165<br />

160<br />

155<br />

40<br />

150<br />

20<br />

145<br />

12.0<br />

10.0<br />

0<br />

25 50 75 100 125 150 175<br />

T C , Case Temperature (°C)<br />

Fig 9. Maximum Drain Current vs.<br />

Case Temperature<br />

8.0<br />

6.0<br />

140<br />

-60 -40 -20 0 20 40 60 80 100120140160180<br />

3500<br />

3000<br />

2500<br />

2000<br />

1500<br />

T J , Temperature ( °C )<br />

Fig 10. Drain-to-Source Breakdown Voltage<br />

I D<br />

TOP 21.5A<br />

29.3A<br />

BOTTOM 103A<br />

4.0<br />

2.0<br />

1000<br />

500<br />

0.0<br />

0 20 40 60 80 100 120 140 160<br />

V DS, Drain-to-Source Voltage (V)<br />

0<br />

25 50 75 100 125 150 175<br />

Starting T J , Junction Temperature (°C)<br />

Fig 11. Typical C OSS Stored Energy<br />

Fig 12. Maximum Avalanche Energy vs. DrainCurrent<br />

4 www.irf.com

E AR , Avalanche Energy (mJ)<br />

Avalanche Current (A)<br />

IRFP4568PbF<br />

1<br />

Thermal Response ( Z thJC ) °C/W<br />

0.1<br />

0.01<br />

0.001<br />

D = 0.50<br />

0.20<br />

0.10<br />

0.05<br />

0.02<br />

0.01<br />

SINGLE PULSE<br />

( THERMAL RESPONSE )<br />

τ J<br />

τ J<br />

τ 1 τ<br />

τ 2 τ 3<br />

1<br />

τ 2 τ 3<br />

Ci= τi/Ri<br />

Ci i/Ri<br />

R 1 R 2 R 3<br />

R 1 R 2 R 3<br />

0.0001<br />

1E-006 1E-005 0.0001 0.001 0.01 0.1<br />

t 1 , Rectangular Pulse Duration (sec)<br />

Fig 13. Maximum Effective Transient Thermal Impedance, Junction-to-Case<br />

τ C<br />

τ<br />

Ri (°C/W) τi (sec)<br />

0.06336 0.000278<br />

0.11088 0.005836<br />

0.11484 0.053606<br />

Notes:<br />

1. Duty Factor D = t1/t2<br />

2. Peak Tj = P dm x Zthjc + Tc<br />

1000<br />

100<br />

Duty Cycle = Single Pulse<br />

0.01<br />

Allowed avalanche Current vs avalanche<br />

pulsewidth, tav, assuming ∆Tj = 150°C and<br />

Tstart =25°C (Single Pulse)<br />

10<br />

0.05<br />

0.10<br />

1<br />

Allowed avalanche Current vs avalanche<br />

pulsewidth, tav, assuming ∆Τj = 25°C and<br />

Tstart = 150°C.<br />

0.1<br />

1.0E-06 1.0E-05 1.0E-04 1.0E-03 1.0E-02 1.0E-01<br />

tav (sec)<br />

Fig 14. Typical Avalanche Current vs.Pulsewidth<br />

900<br />

800<br />

700<br />

600<br />

500<br />

400<br />

300<br />

200<br />

100<br />

TOP Single Pulse<br />

BOTTOM 1.0% Duty Cycle<br />

I D = 103A<br />

Notes on Repetitive Avalanche Curves , Figures 14, 15:<br />

(For further info, see AN-1005 at www.irf.com)<br />

1. Avalanche failures assumption:<br />

Purely a thermal phenomenon and failure occurs at a temperature far in<br />

excess of T jmax . This is validated for every part type.<br />

2. Safe operation in Avalanche is allowed as long asT jmax is not exceeded.<br />

3. Equation below based on circuit and waveforms shown in Figures 16a, 16b.<br />

4. P D (ave) = Average power dissipation per single avalanche pulse.<br />

5. BV = Rated breakdown voltage (1.3 factor accounts for voltage increase<br />

during avalanche).<br />

6. I av = Allowable avalanche current.<br />

7. ∆T = Allowable rise in junction temperature, not to exceed T jmax (assumed as<br />

25°C in Figure 14, 15).<br />

t av = Average time in avalanche.<br />

D = Duty cycle in avalanche = t av ·f<br />

Z thJC (D, t av ) = Transient thermal resistance, see Figures 13)<br />

0<br />

25 50 75 100 125 150 175<br />

Starting T J , Junction Temperature (°C)<br />

Fig 15. Maximum Avalanche Energy vs. Temperature<br />

P D (ave) = 1/2 ( 1.3·BV·I av ) = DT/ Z thJC<br />

I av = 2DT/ [1.3·BV·Z th ]<br />

E AS (AR) = P D (ave)·t av<br />

www.irf.com 5

Gate threshold Voltage (V)<br />

V GS(th) ,<br />

I RR (A)<br />

Q RR (A)<br />

Q RR (A)<br />

I RR (A)<br />

IRFP4568PbF<br />

6.0<br />

5.5<br />

5.0<br />

4.5<br />

4.0<br />

60<br />

50<br />

40<br />

I F = 68A<br />

V R = 100V<br />

T J = 25°C<br />

T J = 125°C<br />

3.5<br />

30<br />

3.0<br />

2.5<br />

2.0<br />

1.5<br />

I D = 250µA<br />

I D = 1.0mA<br />

ID = 1.0A<br />

20<br />

10<br />

1.0<br />

-75 -50 -25 0 25 50 75 100 125 150 175<br />

T J , Temperature ( °C )<br />

Fig 16. Threshold Voltage vs. Temperature<br />

0<br />

0 200 400 600 800 1000<br />

di F /dt (A/µs)<br />

Fig. 17 - Typical Recovery Current vs. di f /dt<br />

70<br />

60<br />

50<br />

40<br />

I F = 103A<br />

V R = 100V<br />

T J = 25°C<br />

T J = 125°C<br />

3600<br />

3200<br />

2800<br />

2400<br />

I F = 68A<br />

V R = 100V<br />

T J = 25°C<br />

T J = 125°C<br />

30<br />

20<br />

2000<br />

1600<br />

1200<br />

10<br />

800<br />

0<br />

0 200 400 600 800 1000<br />

di F /dt (A/µs)<br />

Fig. 18 - Typical Recovery Current vs. di f /dt<br />

400<br />

0 200 400 600 800 1000<br />

di F /dt (A/µs)<br />

Fig. 19 - Typical Stored Charge vs. di f /dt<br />

4000<br />

3600<br />

3200<br />

2800<br />

I F = 103A<br />

V R = 100V<br />

T J = 25°C<br />

T J = 125°C<br />

2400<br />

2000<br />

1600<br />

1200<br />

800<br />

400<br />

0 200 400 600 800 1000<br />

di F /dt (A/µs)<br />

Fig. 20 - Typical Stored Charge vs. di f /dt<br />

6 www.irf.com

IRFP4568PbF<br />

+<br />

‚<br />

-<br />

D.U.T<br />

+<br />

ƒ<br />

-<br />

Circuit Layout Considerations<br />

• Low Stray Inductance<br />

• Ground Plane<br />

• Low Leakage Inductance<br />

Current Transformer<br />

-<br />

„<br />

+<br />

Reverse<br />

Recovery<br />

Current<br />

Driver Gate Drive<br />

Period<br />

P.W.<br />

D.U.T. I SD Waveform<br />

Body Diode Forward<br />

Current<br />

di/dt<br />

D.U.T. V DS Waveform<br />

Diode Recovery<br />

dv/dt<br />

D =<br />

P.W.<br />

Period<br />

V GS =10V<br />

V DD<br />

*<br />

R G<br />

• dv/dt controlled by RG<br />

• Driver same type as D.U.T.<br />

• I SD controlled by Duty Factor "D"<br />

• D.U.T. - Device Under Test<br />

V DD<br />

+<br />

-<br />

Re-Applied<br />

Voltage<br />

Body Diode<br />

Inductor Curent Current<br />

Forward Drop<br />

Ripple ≤ 5%<br />

I SD<br />

* V GS = 5V for Logic Level Devices<br />

Fig 21. Peak Diode Recovery dv/dt Test Circuit for N-Channel<br />

HEXFET ® Power MOSFETs<br />

15V<br />

tp<br />

V (BR)DSS<br />

L<br />

DRIVER<br />

R G<br />

20V V GS<br />

tp<br />

V DS<br />

+<br />

D.U.T<br />

IAS<br />

0.01Ω<br />

- V DD<br />

A<br />

I AS<br />

Fig 22a. Unclamped Inductive Test Circuit<br />

Fig 22b. Unclamped Inductive Waveforms<br />

V DS<br />

R D<br />

V DS<br />

V GS<br />

D.U.T.<br />

90%<br />

R G<br />

+<br />

-<br />

V DD<br />

V10V<br />

GS<br />

Pulse Width ≤ 1 µs<br />

Duty Factor ≤ 0.1 %<br />

10%<br />

V GS<br />

t d(on) t r t d(off) t f<br />

Fig 23a. Switching Time Test Circuit<br />

Fig 23b. Switching Time Waveforms<br />

Current Regulator<br />

Same Type as D.U.T.<br />

Vds<br />

Id<br />

50KΩ<br />

Vgs<br />

12V<br />

.2µF<br />

.3µF<br />

V GS<br />

D.U.T.<br />

+<br />

V<br />

- DS<br />

Vgs(th)<br />

3mA<br />

I G I D<br />

Current Sampling Resistors<br />

Qgs1 Qgs2 Qgd Qgodr<br />

Fig 24a. Gate Charge Test Circuit<br />

Fig 24b. Gate Charge Waveform<br />

www.irf.com 7

IRFP4568PbF<br />

TO-247AC Package Outline<br />

Dimensions are shown in millimeters (inches)<br />

TO-247AC Part Marking Information<br />

@Y6HQG@)<br />

UCDTDT6IDSAQ@"<br />

XDUC6TT@H7G`<br />

GPU8P9@$%$&<br />

6TT@H7G@9PIXX"$!<br />

DIUC@6TT@H7G`GDI@C<br />

I‚‡r)Qv h††r€iy’yv rƒ‚†v‡v‚<br />

v qvph‡r†GrhqA…rr<br />

DIU@SI6UDPI6G<br />

S@8UDAD@S<br />

GPBP<br />

6TT@H7G`<br />

GPU8P9@<br />

,5)3(<br />

+<br />

<br />

Q6SUIVH7@S<br />

96U@8P9@<br />

`@6S 2!<br />

X@@F"$<br />

GDI@C<br />

TO-247AC package is not recommended for Surface Mount Application.<br />

Note: For the most current drawing please refer to IR website at http://www.irf.com/package/<br />

Data and specifications subject to change without notice.<br />

This product has been designed and qualified for the Industrial market.<br />

Qualification Standards can be found on IR’s Web site.<br />

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105<br />

TAC Fax: (310) 252-7903<br />

Visit us at www.irf.com for sales contact information. 09/2008<br />

8 www.irf.com