PCIe Devices - PLX Technology

PCIe Devices - PLX Technology PCIe Devices - PLX Technology

Transaction Layer Provides End-to-End Service Host System Requestor (Completer) Completer (Requestor) PCIe Device Application Application Root Complex Transaction Layer Data Link Layer Physical Layer End-to-End Switch Transaction Layer Data Link Layer Physical Layer Data Link Layer Physical Layer Data Link Layer Physical Layer Copyright by Dashcourses, Inc. 2009 2-78

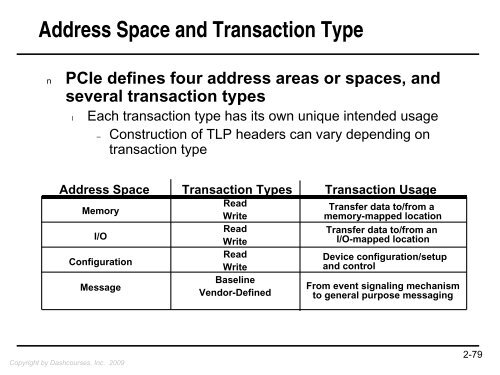

Address Space and Transaction Type n PCIe defines four address areas or spaces, and several transaction types l Each transaction type has its own unique intended usage – Construction of TLP headers can vary depending on transaction type Address Space Memory I/O Configuration Message Transaction Types Read Write Read Write Read Write Baseline Vendor-Defined Transaction Usage Transfer data to/from a memory-mapped location Transfer data to/from an I/O-mapped location Device configuration/setup and control From event signaling mechanism to general purpose messaging Copyright by Dashcourses, Inc. 2009 2-79

- Page 27 and 28: PCIe Transactions and Packets n PCI

- Page 29 and 30: PCI Devices n n n PCI is based on a

- Page 31 and 32: PCI Topology with Multiple Host/PCI

- Page 33 and 34: PCIe Device/Function PCIe Single Fu

- Page 35 and 36: PCIe System Fabric PCIe Root Comple

- Page 37 and 38: PCI/PCI-X/PCIe Bridges n Bridges ar

- Page 39 and 40: PCI/PCI-X Arbitration Example n n F

- Page 41 and 42: PCIe Processing and Priorities n PC

- Page 43 and 44: Mythical Example VC ID and Priority

- Page 45 and 46: PCIe Root Complex n A Root Complex

- Page 47 and 48: PCIe Root Complex Model Host system

- Page 49 and 50: PCIe Switch Structure Upstream Port

- Page 51 and 52: PCIe Interrupts Host System Bus Whe

- Page 53 and 54: PCIe Link is a Point-to-Point Conne

- Page 55 and 56: PCIe Differential Drivers n PCIe de

- Page 57 and 58: PCIe Link Attributes (continued) n

- Page 59 and 60: PCIe Can be Aggregated n PCIe devic

- Page 61 and 62: MBps vs. Gbps?? n Comparing data ra

- Page 63 and 64: PCI Configuration Header Types n Fi

- Page 65 and 66: PCI Configuration Header Type 0 PCI

- Page 67 and 68: Host PCI Bridge Discovery n n n Acc

- Page 69 and 70: PCIe Primary/Secondary Bus Scheme P

- Page 71 and 72: Optional Registers (continued) Last

- Page 73 and 74: PCIe Configuration Space DWord 1000

- Page 75 and 76: Key Aspects of Transaction Layer n

- Page 77: PCIe Transactions n Software will t

- Page 81 and 82: TLP size Varies n TLP construction

- Page 83 and 84: PCIe Transaction Movement Host Syst

- Page 85 and 86: TLP Packet Components n TLP packets

- Page 87 and 88: TLP Receiver Processing n Received

- Page 89 and 90: Message Codes n Messages are define

- Page 91 and 92: Section 3 PCIe Data Link Layer Copy

- Page 93 and 94: Key Aspects of Data Link Layer n At

- Page 95 and 96: Data Link Layer Created Packets - T

- Page 97 and 98: Data Link Layer Received Packets Pa

- Page 99 and 100: Data Link Layer Handling of TLPs n

- Page 101 and 102: Link Initialization and Flow Contro

- Page 103 and 104: Initialization n Example TS1/TS2 l

- Page 105 and 106: Flow Control n Example credit excha

- Page 107 and 108: Basic DLLP Header Fields n All Data

- Page 109 and 110: Transaction Layer Buffer Space and

- Page 111 and 112: PCIe Power Management Overview n PC

- Page 113 and 114: Link Training and Status State Mach

- Page 115 and 116: Normal Operations n Once the Link i

- Page 117 and 118: Sequence Number - Transmit Requesto

- Page 119 and 120: Section 4 PCIe Physical Layer Copyr

- Page 121 and 122: Physical Layer Overview n The PCIe

- Page 123 and 124: Physical Layer Packets Packet deliv

- Page 125 and 126: Scrambling n Scrambling is a techni

- Page 127 and 128: 8B/10B Signal Encoding Data Byte Na

Address Space and Transaction Type<br />

n<br />

<strong>PCIe</strong> defines four address areas or spaces, and<br />

several transaction types<br />

l<br />

Each transaction type has its own unique intended usage<br />

– Construction of TLP headers can vary depending on<br />

transaction type<br />

Address Space<br />

Memory<br />

I/O<br />

Configuration<br />

Message<br />

Transaction Types<br />

Read<br />

Write<br />

Read<br />

Write<br />

Read<br />

Write<br />

Baseline<br />

Vendor-Defined<br />

Transaction Usage<br />

Transfer data to/from a<br />

memory-mapped location<br />

Transfer data to/from an<br />

I/O-mapped location<br />

Device configuration/setup<br />

and control<br />

From event signaling mechanism<br />

to general purpose messaging<br />

Copyright by Dashcourses, Inc. 2009<br />

2-79