Sequential Logic Design Principles - Masaryk University

Sequential Logic Design Principles - Masaryk University

Sequential Logic Design Principles - Masaryk University

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

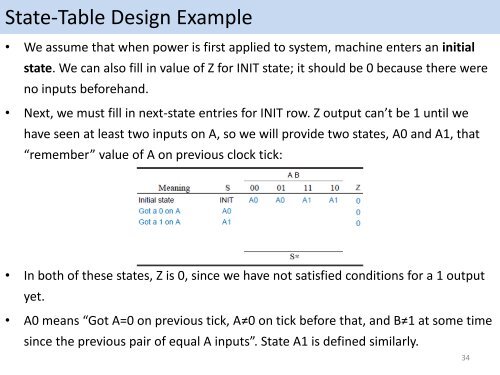

State-Table <strong>Design</strong> Example<br />

• We assume that when power is first applied to system, machine enters an initial<br />

state. We can also fill in value of Z for INIT state; it should be 0 because there were<br />

no inputs beforehand.<br />

• Next, we must fill in next-state entries for INIT row. Z output can’t be 1 until we<br />

have seen at least two inputs on A, so we will provide two states, A0 and A1, that<br />

“remember” value of A on previous clock tick:<br />

• In both of these states, Z is 0, since we have not satisfied conditions for a 1 output<br />

yet.<br />

• A0 means “Got A=0 on previous tick, A≠0 on tick before that, and B≠1 at some time<br />

since the previous pair of equal A inputs”. State A1 is defined similarly.<br />

34