AN4603 - Freescale Semiconductor

AN4603 - Freescale Semiconductor

AN4603 - Freescale Semiconductor

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Freescale</strong> <strong>Semiconductor</strong><br />

Application Note<br />

1 Purpose<br />

The present document is intended to teach the reader how to<br />

supply the power management to the i.MX50x family of<br />

processors using either the <strong>Freescale</strong> MC13892 or the<br />

MC34709 as the main power management device.<br />

2 Introduction<br />

The i.MX50x family of microprocessors requires complex<br />

power management distribution along with specific<br />

sequencing for proper power up. To supply integrated power<br />

management to the i.MX50 processors, <strong>Freescale</strong> provides<br />

two highly integrated PMICs solutions for different specific<br />

scenarios. The MC13892, provide a highly integrated solution<br />

which provides most of the required voltage rails as well as<br />

integrated battery charger, 10 bits ADC and backlight LED<br />

drivers. Likewise, the MC34709 is a reduced solution<br />

providing as well the majority of the required power rails for<br />

applications with less system requirements.<br />

© <strong>Freescale</strong> <strong>Semiconductor</strong>, Inc., 2012. All rights reserved.<br />

<br />

Document Number: <strong>AN4603</strong><br />

Rev. 1.0, 12/2012<br />

Power Management Design Guidelines for<br />

the i.MX50x Family of Microprocessors<br />

Contents<br />

1 Purpose . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1<br />

2 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . 1<br />

3 i.MX50 Microprocessor Overview . . . . . . . . 2<br />

4 i.MX50 Power Management Design with<br />

MC13892 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4<br />

5 i.MX50 Power Management Design with the<br />

MC34709 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23<br />

6 References . . . . . . . . . . . . . . . . . . . . . . . . . . 43<br />

7 Revision History . . . . . . . . . . . . . . . . . . . . . 44

i.MX50 Microprocessor Overview<br />

3 i.MX50 Microprocessor Overview<br />

The i.MX50 Applications Processors (i.MX50) is part of a growing family of multimedia-focused products, offering<br />

high performance processing optimized for lowest power consumption.<br />

The i.MX50 is optimized for portable multimedia applications and it features <strong>Freescale</strong>'s advanced implementation<br />

of the ARM Cortex-A8 core, which operates at speed as high as 800 MHz. The i.MX50 provides a powerful display<br />

architecture, including a 2D Graphics Processing Unit (GPU) and Pixel Processing Pipeline (ePXP). In addition,<br />

i.MX508 includes a complete integration of the electrophoretic display function. The i.MX50 supports DDR2,<br />

LPDDR2, and LPDDR1 DRAM at clock rate up to 266 MHz to enable a range of performance and power trade-offs.<br />

The flexibility of the i.MX50 architecture allows it to be used in a variety of applications. As the heart of the application<br />

chipset, the i.MX50 provides a rich set of interfaces for connecting peripherals, such as WLAN, Bluetooth, GPS,<br />

and displays.<br />

i.MX50 power requirements are summarized in Table 1.<br />

Table 1. i.MX50 Power requirements<br />

Voltage Domain Voltage Current<br />

Name Description TYP Units Max Units<br />

VDDGP 400< fARM ≤ 800 MHz 1.05 V 1250 mA<br />

167< fARM ≤ 400 MHz 0.95 V<br />

24< fARM ≤ 167 MHz 0.9 V<br />

Stop Mode 0.85 V<br />

VCC LPM 0.95 V 400 mA<br />

RPM 1.05 V<br />

HPM 1.225 V<br />

VDDA Run Mode 1.2 V 250 mA<br />

Stop Mode 0.95 V<br />

VDDAL1 Run Mode 1.2 V<br />

Stop Mode 0.95 V<br />

VDD3P0 Bandgap and 480 MHz PLL<br />

supply<br />

VDD2P5 Efuse, 24 MHz oscillator, 32 kHz<br />

oscillator mux supply<br />

3.0 V 10 mA<br />

2.5 V 150 mA<br />

VDD1P2 PLL digital supplies 1.8 V 10 mA<br />

VDD1P8 PLL analog supplies 1.8 V 10 mA<br />

NVCC_JTAG GPIO digital power supplies 1.875 or 2.775 V<br />

NVCC_EMI_DRAM DDR2/LPDDR1 1.8 V 350 mA<br />

LPDDR2 1.2 V<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

2 <strong>Freescale</strong> <strong>Semiconductor</strong>

VREF DRAM Reference Voltage Input 1/2<br />

NVCC_E<br />

MI_DRAM<br />

i.MX50 Microprocessor Overview<br />

V 0.004 mA<br />

VDDO25 EMI Pad Predriver supply 2.5 V 10 mA<br />

NVCC_NANDF<br />

NVCC_SD1<br />

NVCC_SD2<br />

NVCC_KEYPAD<br />

NVCC_EIM<br />

NVCC_EPDC<br />

NVCC_LCD<br />

NVCC_MISC<br />

NVCC_SPI<br />

NVCC_SSI<br />

NVCC_UART<br />

High voltage I/O (HVIO)<br />

supplies<br />

NVCC_SRTC SRTC core and I/O supply<br />

(LVIO)<br />

HVIO_L=1.875<br />

HVIO_H=3.0<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 3<br />

V<br />

1.2 V<br />

NVCC_RESET LVIO 1.875 or 2.775 V<br />

USB_H1_VDDA25<br />

USB_OTG_VDDA25<br />

USB_DDA33<br />

USB_OTG_VDA33<br />

Table 1. i.MX50 Power requirements<br />

Voltage Domain Voltage Current<br />

Name Description TYP Units Max Units<br />

USB_PHY analog supply 2.5 V 50 mA<br />

USB PHY I/O analog supply 3.3 V 16 mA

i.MX50 Power Management Design with MC13892<br />

3.1 i.MX50 Power-up/down Sequence<br />

VDDGP<br />

VDDA<br />

VDDAL1<br />

Figure 1. i.MX50 Power up Sequence<br />

NOTE<br />

• The POR_B input must be immediately asserted at power-up and remain<br />

asserted until after the last power rail is at its working voltage.<br />

• No power-up sequence dependencies exist between the supplies shown<br />

shaded in gray.<br />

3.2 Power-Down Sequence<br />

NVCC_SRTC<br />

The power-down sequence is recommended to be the opposite of the power-up sequence. In other words, the same<br />

power supply constraints exist while powering off as while powering on.<br />

4 i.MX50 Power Management Design with MC13892<br />

VCC<br />

VDD3P0 VDDO2P5<br />

VDD2P5<br />

VDD1P8 VDD1P2<br />

NVCC_EMI_DRAM<br />

VREF<br />

NVCC_EIM<br />

NVCC_EPDC<br />

NVCC_JTAG<br />

NVCC_KEYPAD<br />

NVCC_LCD<br />

NVCC_MISC<br />

NVCC_NANDF<br />

NVCC_RESET<br />

NVCC_SD1<br />

NVCC_SD2<br />

NVCC_SSI<br />

NVCC_UART<br />

USB_OTG_VDDA25<br />

USB_H1_VDDA25<br />

USB_OTG_VDDA33<br />

USB_H1_VDDA33<br />

The MC13892 is a power management IC that includes the necessary sources to supply the i.MX50. Its main<br />

features are:<br />

• Battery charger system for wall charging and USB charging<br />

• 10-bit ADC for monitoring battery and other inputs, plus a coulomb counter support module<br />

• Four adjustable output buck regulators for direct supply of the processor core and memory<br />

• 12 adjustable output LDOs with internal and external pass devices<br />

• Boost regulator for supplying RGB LEDs<br />

• Serial backlight drivers for displays and keypad, plus RGB LED drivers<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

4 <strong>Freescale</strong> <strong>Semiconductor</strong>

i.MX50 Power Management Design with MC13892<br />

• Power control logic with processor interface and event detection<br />

• Real time clock and crystal oscillator circuitry, with coin cell backup and support for external secure real time<br />

clock on a companion system processor IC<br />

• Touch screen interface<br />

• SPI/I2C bus interface for control and register access<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 5

i.MX50 Power Management Design with MC13892<br />

4.1 MC13892 Voltage supplies<br />

Supply Typical Application<br />

Table 2. MC13892 Voltage Supplies Summary<br />

4.2 MC13892 Power-up Sequence<br />

Output Voltage<br />

(in V)<br />

Load Capability<br />

(in mA)<br />

SW1 Buck regulators for processor core(s) 0.600-1.375 1050<br />

SW2 Buck regulators for processor SOG, etc. 0.600-1.375; 1.100-1.850 800<br />

SW3 Buck regulators for internal processor memory and<br />

peripherals<br />

SW4 Buck regulators for external memory and<br />

peripherals<br />

0.600-1.375; 1.100-1.850 800<br />

0.600-1.375; 1.100-1.850 800<br />

SWBST Boost regulator for USB OTG, Tri-color LED drivers 5.0 300<br />

VIOHI IO and Peripheral supply, eFuse support 2.775 100<br />

VPLL Quiet Analog supply (PLL, GPS) 1.2/1.25/1.5/1.8 50<br />

VDIG Low voltage digital (DPLL, GPS) 1.05/1.25/1.65/1.8 50<br />

VSD SD Card, external PNP 1.8/2.0/2.6/2.7/2.8/2.9/3.0/<br />

3.15<br />

VUSB2 External USB PHY supply 2.4/2.6/2.7/2.775 50<br />

VVIDEO TV DAC supply, external PNP 2.5/2.6/2.7/2.775 350<br />

VAUDIO Audio supply 2.3/2.5/2.775/3.0 150<br />

VCAM Camera supply, internal PMOS 2.5/2.6/2.75/3.0 65<br />

Camera supply, external PNP 2.5/2.6/2.75/3.0 250<br />

VGEN1 General peripherals supply #1, external PNP 1.2/1.5/2.775/3.15 200<br />

VGEN2 General peripherals supply #2, external PNP 1.2/1.5/1.6/1.8/2.7/2.8/3.0/<br />

3.15<br />

VGEN3 General peripherals supply #3, internal PMOS 1.8/2.9 50<br />

General peripherals supply #3, external PNP 1.8/2.9 250<br />

VUSB USB Transceiver supply 3.3 100<br />

The Power Up mode Select pins (PUMS1 and 2) are used to configure the startup characteristics of the regulators.<br />

Supply enabling and output level options are selected by hardwiring the PUMSx pins for the desired configuration.<br />

Tying the PUMSx pins to ground corresponds to 00, open to 01, VCOREDIG to 10, and VCORE to 11.<br />

The recommended power up strategy for end products is to bring up as little of the system as possible at booting,<br />

essentially sequestering just the bare essentials, to allow processor startup and software to run. With such a<br />

strategy, the startup transients are controlled at lower levels, and the rest of the system power tree can be brought<br />

up by software. This allows optimization of supply ordering where specific sequences may be required, as well as<br />

supply default values. Software code can load up all of the required programmable options to avoid sneak paths,<br />

under/over-voltage issues, startup surges, etc., without any change in hardware. For this reason, the Power Gate<br />

drivers are limited to activation by software rather than the sequencer, allowing the core(s) to startup before any<br />

peripheral loading is introduced.<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

6 <strong>Freescale</strong> <strong>Semiconductor</strong><br />

250<br />

350

i.MX50 Power Management Design with MC13892<br />

The power up defaults Table 3 shows the initial setup for the voltage level of the switching and LDO regulators,<br />

and whether they get enabled.<br />

Table 3. Power Up Defaults Table<br />

PUMS1 GND Open VCOREDIG VCORE GND Open<br />

PUMS2 Open Open Open Open GND GND<br />

SW1 (1)<br />

SW2 (1)<br />

SW3 (1)<br />

SW4 (1)<br />

0.775 1.050 1.050 0.775 1.200 1.200<br />

1.025 1.225 1.225 1.025 1.350 1.450<br />

1.200 1.200 1.200 1.200 1.800 1.800<br />

1.800 1.800 1.800 1.800 1.800 1.800<br />

SWBST Off Off Off Off 5.000 5.000<br />

VUSB 3.300 (2)<br />

3.300 (2)<br />

3.300 (2)<br />

3.300 (2)<br />

3.300 (4)<br />

3.300 (4)<br />

VUSB2 2.600 2.600 2.600 2.600 2.600 2.600<br />

VPLL 1.800 1.800 1.800 1.800 1.500 1.500<br />

VDIG 1.250 1.250 1.250 1.250 1.250 1.250<br />

VIOHI 2.775 2.775 2.775 2.775 2.775 2.775<br />

VGEN2 3.150 Off 3.150 Off 3.150 3.150<br />

VSD Off Off Off Off 3.150 3.150<br />

Not initialized during power-up<br />

VCAM Off Off Off Off Off Off<br />

VGEN1 Off Off Off Off Off Off<br />

VGEN3 Off Off Off Off Off Off<br />

VVIDEO Off Off Off Off Off Off<br />

VAUDIO Off Off Off Off Off Off<br />

Notes<br />

1. The SWx regulators are activated in PWM pulse skipping mode, but allowed when enabled by the startup sequencer.<br />

2. USB supply VUSB, is only enabled if 5.0 V is present on UVBUS.<br />

3. The following supplies are not included in the matrix since they are not intended for activation by the startup sequencer: VCAM, VGEN1,<br />

VGEN3, VVIDEO, and VAUDIO<br />

4. SWBST = 5.0 V powers up and does VUSB regardless of 5.0 V present on UVBUS. By default VUSB will be supplied by SWBST.<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 7

i.MX50 Power Management Design with MC13892<br />

The power up sequence is shown in Table 4. VCOREDIG, VSRTC, and VCORE are brought up in the pre-sequencer<br />

startup. Once VCOREDIG is activated (i.e., at the first-time power application), it will be continuously powered as<br />

long as a valid coin cell is present.<br />

Table 4. Power Up Sequence<br />

Tap x 2ms PUMS2 = Open PUMS2 = GND<br />

0 SW2 SW2<br />

1 SW4 VGEN2<br />

2 VIOHI SW4<br />

3 VGEN2 VIOHI, VSD<br />

4 SW1 SWBST, VUSB (7)<br />

5 SW3 SW1<br />

6 VPLL VPLL<br />

7 VDIG SW3<br />

8 - VDIG<br />

9 VUSB (6) , VUSB2 VUSB2<br />

Notes<br />

5. The following supplies are not included in the matrix since they are not intended for activation by the startup<br />

sequencer: VCAM, VGEN1, VGEN3, VVIDEO, and VAUDIO. SWBST is not included on the PUMS2 = Open column.<br />

6. USB supply VUSB, is only enabled if 5.0 V is present on UVBUS.<br />

7. SWBST = 5.0 V powers up and so does VUSB regardless of 5.0 V present on UVBUS. By default VUSB will be<br />

supplied by SWBST.<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

8 <strong>Freescale</strong> <strong>Semiconductor</strong>

SW2<br />

SW4<br />

VIOHI<br />

VGEN2<br />

SW1<br />

SW3<br />

VPLL<br />

VDIG<br />

VUSB<br />

VUSB2<br />

Power on event<br />

2ms 2ms 2ms 2ms 2ms 2ms 2ms 4ms<br />

i.MX50 Power Management Design with MC13892<br />

Figure 2. MC13892 Power up Sequence for i.MX50 processors.<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 9

i.MX50 Power Management Design with MC13892<br />

4.3 Interfacing the i.MX50 with the MC13892.<br />

Table 5, shows all the i.MX50 voltage rails, their power requirements and their associated MC13892 regulator. Most<br />

of the supply domains have flexible voltage and could be adjusted or supplied with a different regulator depending<br />

on each application needs<br />

Table 5. i,MX50 voltage domain supplies with the MC13892<br />

I.MX50 MC13892<br />

Power Rail of i.MX50 Power Domain TYP<br />

NVCCSRTC 32 kHz osc. power (when<br />

chip off)<br />

Associated<br />

Regulator<br />

Voltage<br />

PUM[4:0]=1110<br />

Current<br />

(mA)<br />

1.2 VSRTC 1.2 0.05 -<br />

VCC LP Transistor power 1.2 SW2 1.2 800 0<br />

VDDA Peripheral Memory + L2<br />

Cache power<br />

1.2 SW3 1.2 800 5<br />

VDDAL1 L1 Cache power 1.2 SW3 1.2 800 5<br />

VDDGP Core and G Transistor<br />

power<br />

1 SW1 1 1050 4<br />

VDDO2P5 Predriver for EMI pads 2.5 External LDO 2.5 250 -<br />

VDD2P5 Power to 24 MHz osc,<br />

efuse, xtalok,<br />

32 kHz osc. power mux<br />

2.5 External LDO 2.5 250 -<br />

NVCC_EMI_DRAM Power to EMI pins 1.2 External Buck 1.2 - -<br />

VREF DRAM Reference 0.9 Voltage divider 0.5<br />

x<br />

NVCC_EMI_DRA<br />

M<br />

NVCC EIM<br />

NVCC JTAG<br />

NVCC SPI<br />

NVCC SD<br />

NVCC NANDF<br />

NVCC SSI<br />

NVCC MISC<br />

NVCC KEYPAD<br />

ALL 3.3V IO NVCC<br />

NVCC EPDC<br />

NVCC LCD<br />

NVCC UART<br />

NVCC_SD2<br />

3.0 V I/Os 3<br />

3<br />

3<br />

3<br />

3<br />

3.0 V I/Os<br />

VDD3P0 VDD2P5 LDO input +<br />

power to Bandgap,<br />

DCDC predriver,<br />

tempsensor, 480 MHz PLL<br />

3.15<br />

3.15<br />

3.15<br />

3.15<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

10 <strong>Freescale</strong> <strong>Semiconductor</strong><br />

PUS<br />

1.2 * 0.5 250 -<br />

VGEN2 3.0 350 3<br />

External Buck<br />

VSD<br />

3.15<br />

3.15<br />

5000<br />

250<br />

3 VGEN2 3.0 350 3<br />

-<br />

-

i.MX50 Power Management Design with MC13892<br />

USB_OTG_VDDA33 Power to USB Host 3.3 VUSB 3.3 100 9<br />

USB_H1_VDDA33 Power to USB OTG 3.3 VUSB 3.3 100 9<br />

All 1.8 IO NVCC<br />

VDD DCDCI<br />

VDD DCDCO<br />

1.8 V I/Os<br />

NVCC_RESET (LVIO) Power to<br />

POR_B,RESET_IN_B,<br />

TESTMODE, &<br />

BOOTMODE[0:1]<br />

1.8<br />

Not used<br />

1.875 or<br />

2.775<br />

SW4 1.8 800 1<br />

VPLL 1.8 50 6<br />

USB_OTG_VDDA25 Power to USB Host 2.5 VUSB2 2.5 50 9<br />

USB_H1VDDA25 Power to USB OTG 2.5 VUSB2 2.5 50 9<br />

VDD1P8 Power to all PLLs 1.8 VPLL 1.8 50 6<br />

VDD1P2 Power to all PLL digital, 32<br />

kHz osc.<br />

(when chip on), much of<br />

analog, digital<br />

Table 5. i,MX50 voltage domain supplies with the MC13892<br />

I.MX50 MC13892<br />

Power Rail of i.MX50 Power Domain TYP<br />

Associated<br />

Regulator<br />

Voltage<br />

PUM[4:0]=1110<br />

Current<br />

(mA)<br />

1.2 VDIG 1.2 50 7<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 11<br />

PUS

i.MX50 Power Management Design with MC13892<br />

4.3.1 Interfacing Block Diagram<br />

The following block diagrams show all the power connections needed for the interface, as well as how the<br />

communication signals must be connected between the i.MX50 and MC13892.<br />

5.0V<br />

4.2V<br />

regulator<br />

VIN<br />

3.15V<br />

Buck<br />

regulator<br />

MC13892<br />

SW1<br />

SW2<br />

SW4B<br />

VUSB<br />

VUSB2<br />

VDIG<br />

VPLL<br />

VSW3<br />

VGEN2<br />

2.5V<br />

LDO<br />

2.5V<br />

LDO<br />

3.15V<br />

VDDGP<br />

VCC<br />

USB_VDDA33<br />

VDD2P5<br />

VDDO25<br />

Figure 3. i.MX50 Power Interface with MC13892 Block Diagram<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

12 <strong>Freescale</strong> <strong>Semiconductor</strong><br />

1.2V<br />

Buck<br />

i.MX50<br />

NVCC_EIM_DRAM<br />

USB_VDDA25<br />

VDD1P2<br />

VDD1P8<br />

NVCC_RESET<br />

VDDA<br />

VDDAL1<br />

VDD3P0<br />

NVCC_MISC<br />

NVCC_SPI<br />

NVCC_SD1<br />

NVCC_NANDF<br />

NVCC_KEYPAD<br />

NVCC_SSI<br />

NVCC_JTAG<br />

NVCC_UART<br />

NVCC_LCD<br />

NVCC_EPDC<br />

Peripherals<br />

CODEC<br />

HDMI<br />

ETHERNET<br />

3G PCIe<br />

RS-232

MC13892<br />

RESETBMCU<br />

RESETB<br />

STANDBY<br />

POWERON1<br />

WDI<br />

INT<br />

UID<br />

CKL<br />

MISO/SDA<br />

4.3.1.1 3.15 V Buck Regulator<br />

i.MX50 Power Management Design with MC13892<br />

Figure 4. i.MX50 Control Interface with MC34709 Block Diagram<br />

For system stability, it is recommended that you use an extra 3.15 V DCDC power supply to support large current<br />

requirements (for example a 3G module or Wi-Fi card). The MC34709 has limited 3.15 V output ability.<br />

4.3.1.2 1.2 V Buck Regulator<br />

SWx<br />

POR_B<br />

WDOG<br />

CLK32MCU CLK<br />

PUMS1<br />

PUMS2<br />

SWx<br />

SWx<br />

VCOREDIG<br />

GPIOX_X<br />

i.MX50<br />

RESET_IN_B<br />

PMIC_STBY_REQ<br />

PMIC_ON_REQ<br />

USB_OTG_ID<br />

CSPI_SCLK<br />

CSPI_MISO/MOSI<br />

A 1.2V Buck regulator is required to provide voltage to the 1.2V LPDDR2 module and the NVCC_EMI_DRAM<br />

domain in the i.MX50 processor. Regulator SW4 will supply the input of this regulator at 1.8V and will also be used<br />

as the 1.8V supply on the LPDDR2 Module as well.<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 13<br />

NC

i.MX50 Power Management Design with MC13892<br />

4.3.1.3 2.5 V LDO Regulators<br />

Due to the Power-up sequence dependency, two 2.5V LDO regulators are required to power up the VDD2P5 and<br />

VDDO25 domains in the i.MX processor. The first one is enabled by the SW2 voltage rail, while the second LDO is<br />

enabled with the VGEN2 voltage rail. See Figure 3.<br />

4.3.2 Interface Power-up Sequence<br />

The resulting power-up sequence of the interface is shown in the following figure<br />

VDD2P5<br />

NVCC_EMI<br />

_DRAM<br />

VDDO25<br />

3.3V NVCC<br />

I/O<br />

NVCC_EPDC<br />

NVCC_LCD<br />

NVCC UART<br />

USB_OTG_VDDA33<br />

USB_H1_VDDA33<br />

NVCCSRTC VSRTC<br />

VCC SW2<br />

1.8 NVCC I/O rails<br />

VDD DCDCI<br />

VDD DCDCO<br />

N/A<br />

VDD3P0<br />

NVCC EIM<br />

NVCC JTAG<br />

NVCC SPI<br />

NVCC SD<br />

NVCC NANDF<br />

NVCC SSI<br />

NVCC MISC<br />

NVCC KEYPAD<br />

VDDGP<br />

VDDA<br />

VDDAL1<br />

VDD1P8<br />

NVCC_RESET (LVIO)<br />

VDD1P2<br />

USB_OTG_VDDA25<br />

USB_H1VDDA25<br />

SD2<br />

2.5V<br />

LDO<br />

regulator<br />

1.2V<br />

DC-DC<br />

regulator<br />

2.5V<br />

LDO<br />

regulator<br />

Figure 5. Power up Sequence Flow Chart<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

14 <strong>Freescale</strong> <strong>Semiconductor</strong><br />

3.15V<br />

Buck<br />

regulator<br />

VUSB<br />

SW4<br />

VIOHI<br />

VGEN2<br />

SW1<br />

SW3<br />

VPLL<br />

VDIG<br />

VSD* Enabled via<br />

SPI<br />

VUSB2

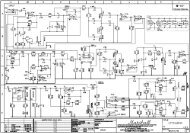

4.4 Application Example with the MC13892<br />

i.MX50 Power Management Design with MC13892<br />

The following schematic is simplified application example for interfacing the MC13892 with an i.MX50 processor.<br />

note that this schematic only includes the block related to the power section as well as power management<br />

controlling signals.<br />

U12E<br />

JP3<br />

HDR 1X2<br />

DNP<br />

PCIMX508DJV1A<br />

VDDGP<br />

3V_VGEN2<br />

SH4<br />

DNP<br />

VDD2P5<br />

1V8_ANA_PLL<br />

GND<br />

GND<br />

VDD3P0<br />

VDD2P5<br />

VDD1P8<br />

i.MX50 - POWER<br />

VDDGP_1<br />

C68<br />

C70 C86<br />

0.22UF<br />

0.22UF 0.22UF<br />

GND<br />

VCC<br />

1V2_SW2<br />

1V2_DIG GND<br />

VDD1P2<br />

C81 C82<br />

22UF 0.1UF<br />

C76<br />

C91 C78<br />

C80<br />

0.22UF<br />

0.22UF 0.22UF<br />

10UF<br />

GND<br />

1V2_SW3<br />

SH5<br />

0<br />

1V8_SW4<br />

GND<br />

VDDA<br />

C94<br />

SH9<br />

0<br />

SH6<br />

DNP<br />

C84<br />

VDD_DCDCI<br />

0.1UF<br />

0.1UF<br />

GND<br />

GND<br />

VDDA_L<br />

SH10<br />

0<br />

DNP<br />

TP11 2.2UH 2 L8 1 VDD_DCDCO<br />

GND<br />

GND<br />

SH11<br />

0<br />

VDDO2P5<br />

GND<br />

G8<br />

VDDGP_2 G9<br />

VDDGP_3 G10<br />

VDDGP_4 H8<br />

VDDGP_5 H9<br />

VCC_1 H14<br />

VCC_2 H15<br />

VCC_3 H16<br />

VCC_4 H17<br />

J17<br />

VCC_5 K14<br />

VCC_6 K15<br />

VCC_7<br />

P17<br />

VDDA_1<br />

VDDA_2 R17<br />

VDDGP_6 H10<br />

VDDGP_7<br />

K17<br />

VCC_8<br />

W5<br />

GND_DCDC<br />

H11<br />

J8<br />

VDDGP_8 K7<br />

VDDGP_9 K8<br />

VDDGP_10<br />

K10<br />

VDDGP_11 K11<br />

VDDGP_12 L8<br />

VDDGP_13 L10<br />

VDDGP_14 L11<br />

VDDGP_15<br />

L15<br />

VCC_9<br />

P15<br />

VDDAL_1<br />

VDDAL_2 R15<br />

Y6<br />

VDD_DCDCI<br />

Y5<br />

VDD_DCDCO<br />

VDDO25 N23<br />

SH8<br />

DNP<br />

C89<br />

C66<br />

0.1UF<br />

C74<br />

0.1UF<br />

C75<br />

AD3<br />

VDD3P0<br />

AD4<br />

VDD2P5<br />

AD7<br />

VDD1P8<br />

C67<br />

C69 C85<br />

C87 C71 C88 C72 C73 SH7<br />

0<br />

0.22UF<br />

0.22UF 0.22UF<br />

0.22UF 0.01UF 0.01UF 10UF 22UF<br />

JP2<br />

HDR 1X2<br />

DNP<br />

0.1UF 22UF<br />

AD6<br />

VDD1P2<br />

C90 C77<br />

C92 C79<br />

0.22UF 0.22UF<br />

0.01UF 0.01UF<br />

C93<br />

22UF<br />

C83<br />

0.1UF<br />

C95 C96<br />

0.1UF 0.1UF<br />

C98<br />

C97 DNP<br />

68uFDNP 0.1UF<br />

C99<br />

0.1UF<br />

3V_VGEN2<br />

SH12<br />

DNP<br />

3V_VGEN2<br />

SH14<br />

DNP<br />

DCDC_3V15<br />

SH15<br />

DNP<br />

3V_VGEN2<br />

SH17<br />

DNP<br />

DCDC_3V15<br />

SH19<br />

DNP<br />

3V_VGEN2<br />

SH21<br />

DNP<br />

3V15_VSD<br />

SH23<br />

DNP<br />

3V_VGEN2<br />

SH25<br />

DNP<br />

3V_VGEN2<br />

SH27<br />

DNP<br />

GND<br />

NVCC_KEYPAD<br />

C100<br />

0.1UF<br />

GND<br />

NVCC_LCD U11<br />

NVCC_LCD<br />

C128<br />

0.1UF<br />

GND<br />

NVCC_NANDF<br />

C131 C132<br />

0.1UF 0.1UF<br />

NVCC_SD2 U8<br />

NVCC_SD2<br />

C135<br />

0.1UF<br />

GND<br />

NVCC_SD1 T7<br />

NVCC_SD1<br />

C137<br />

0.1UF<br />

GND<br />

NVCC_SPI R7<br />

NVCC_SPI<br />

C145<br />

0.1UF<br />

GND<br />

N8<br />

NVCC_KEYPAD<br />

GND<br />

NVCC_MISC P8<br />

NVCC_MISC<br />

C113<br />

0.1UF<br />

GND<br />

NVCC_UART T8<br />

NVCC_UART<br />

C117<br />

0.1UF<br />

GND<br />

NVCC_SSI R8<br />

NVCC_SSI<br />

C127<br />

0.1UF<br />

V10<br />

V9<br />

NVCC_NANDF2<br />

NVCC_NANDF1<br />

AA2<br />

NGND_SRTC<br />

AC6<br />

GND1P2<br />

GND_KEL<br />

AA7<br />

AC3<br />

AC7 GND3P0<br />

AC4 GND1P8<br />

GND2P5<br />

GND<br />

A21<br />

NVCC_EMI_DRAM_1<br />

B21<br />

NVCC_EMI_DRAM_2<br />

NVCC_EMI_DRAM_3 D21<br />

NVCC_EMI_DRAM_4 D23<br />

NVCC_EMI_DRAM_5 D24<br />

K21<br />

NVCC_EMI_DRAM_6<br />

K23<br />

NVCC_EMI_DRAM7<br />

NVCC_EMI_DRAM9<br />

L7<br />

NVCC_EIM1<br />

R21<br />

NVCC_EMI_DRAM10 R23<br />

NVCC_EMI_DRAM11 R24<br />

K24<br />

NVCC_EMI_DRAM8<br />

AA21<br />

NVCC_EMI_DRAM12 AA23<br />

NVCC_EMI_DRAM13 AA24<br />

NVCC_EMI_DRAM14 AC21<br />

NVCC_EMI_DRAM15 AD21<br />

NVCC_EMI_DRAM16<br />

NVCC_EIM2 M7<br />

NVCC_EIM3 M8<br />

VSS1<br />

VSS2<br />

VSS3<br />

VSS4<br />

VSS5<br />

VSS6<br />

VSS7<br />

VSS8<br />

VSS9<br />

VSS10<br />

VSS11<br />

VSS12<br />

VSS13<br />

VSS14<br />

VSS15<br />

VSS16<br />

VSS17<br />

VSS18<br />

VSS19<br />

VSS20<br />

VSS21<br />

VSS22<br />

VSS23<br />

VSS24<br />

VSS25<br />

VSS26<br />

VSS27<br />

VSS28<br />

VSS29<br />

VSS30<br />

VSS31<br />

VSS32<br />

VSS33<br />

VSS34<br />

VSS35<br />

VSS36<br />

VSS37<br />

VSS38<br />

VSS39<br />

VSS40<br />

VSS41<br />

VSS42<br />

VSS43<br />

VSS44<br />

VSS45<br />

VSS46<br />

VSS47<br />

VSS48<br />

VSS49<br />

VSS50<br />

VSS51<br />

VSS52<br />

VSS53<br />

VSS54<br />

A1<br />

A18<br />

A24<br />

B18<br />

G20<br />

G21<br />

G23<br />

H12<br />

H13<br />

K12<br />

K13<br />

L12<br />

L13<br />

L14<br />

L17<br />

M11<br />

M14<br />

M15<br />

M17<br />

M18<br />

M20<br />

M21<br />

N11<br />

N14<br />

N15<br />

N17<br />

P11<br />

P12<br />

P13<br />

P14<br />

R11<br />

R12<br />

R13<br />

R14<br />

T17<br />

T18<br />

U12<br />

U13<br />

U14<br />

U15<br />

U16<br />

U17<br />

U18<br />

V17<br />

V18<br />

V20<br />

V21<br />

V23<br />

AA9<br />

AA11<br />

AC18<br />

AD1<br />

AD18<br />

AD24<br />

NVCC_EPDC1 M10<br />

NVCC_EPDC2 N10<br />

P10<br />

NVCC_EPDC3<br />

NVCC_EPDC4 R10<br />

NVCC_EPDC5 U10<br />

AC9<br />

USB_OTG_VDDA25_1 AD9<br />

USB_H1_VDDA25_1<br />

GND<br />

3V_VGEN2<br />

NVCC_JTAG<br />

NVCC_JTAG<br />

R56<br />

DNP<br />

0<br />

1V8_SW4<br />

GND<br />

1V8_ANA_PLL<br />

NVCC_RESET<br />

C146<br />

0.1UF<br />

U9<br />

C138<br />

0.1UF SH26<br />

DNP<br />

V8<br />

NVCC_RESET<br />

SH28<br />

DNP<br />

Figure 6. i.MX50 Voltage Domains<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 15<br />

GND<br />

GND<br />

AD11<br />

USB_OTG_VDDA33 AC11<br />

USB_H1_VDDA33<br />

C129<br />

0.1UF<br />

C133<br />

0.1UF<br />

GND<br />

GND<br />

SH22<br />

DNP<br />

C134<br />

0.1UF<br />

GND<br />

NVCC_SRTC<br />

SH24<br />

NVCC_SRTC<br />

DNP<br />

C136<br />

0.1UF<br />

AA1<br />

C101 C102 C103 C104 C105 C106 C107 C108 C109 C110 C111 C112<br />

0.22UF 0.22UF 0.22UF 0.22UF 0.22UF 0.22UF 0.22UF 0.22UF 0.01UF 0.01UF 10UF 10UF<br />

NVCC_EIM<br />

C114 C115 C116 C118 C119 C120<br />

SH16<br />

DNP<br />

0.1UF 0.1UF 0.1UF 0.01UF 0.01UF 10UF<br />

GND<br />

NVCC_EPDC<br />

C121 C122 C123 C124 C125 C126<br />

SH18<br />

DNP<br />

0.1UF 0.1UF 0.1UF 0.1UF 0.01UF 10UF<br />

SH20<br />

DNP<br />

C130<br />

0.1UF<br />

GND<br />

3V3_USB<br />

2V5_VUSB2<br />

1V2_RTC<br />

1<br />

2<br />

3V_VGEN2<br />

DCDC_3V15<br />

1<br />

2<br />

1V_SW1<br />

JP4<br />

HDR 1X2<br />

DNP<br />

1V2_DDR<br />

1<br />

2<br />

SH13<br />

0<br />

3V_VGEN2<br />

C143 C144<br />

22UF 0.01UF<br />

GND<br />

ICAP Classification:<br />

Drawing Title:<br />

FCP: ___ FIUO: X<br />

i MX50 Reference Des

i.MX50 Power Management Design with MC13892<br />

PCB MOD:<br />

Cut Trace<br />

4,5<br />

Touch Screen<br />

Connector<br />

VCC_BP<br />

Sensitive analog lines.<br />

X1-X2 and Y1-Y2<br />

make differential pairs.<br />

Note: use 10uF for Coulomb Counting of a battery.<br />

DNP if not required.<br />

4,8 CSPI_SS0<br />

1,15 CSPI_SCLK<br />

1,15 CSPI_MOSI<br />

1,15 CSPI_MISO<br />

BATT_NTC<br />

4,9 PMIC_STBY_REQ<br />

SH83<br />

0<br />

DNP<br />

3V3_USB<br />

(PUS_9)<br />

SWBST<br />

5V_APL<br />

R3 DNP 10K<br />

5V_APL<br />

3 2<br />

1<br />

GND<br />

GND<br />

R19 0<br />

-<br />

+<br />

B1<br />

B2<br />

A2<br />

C1<br />

C2<br />

BT1<br />

2994TR<br />

R7<br />

47K<br />

DNP<br />

R17 0<br />

DNP<br />

1V2_RTC 1V8_SW4<br />

LI-ION_BATTERY<br />

GPO1<br />

BATTISNS<br />

U6<br />

NLSV1T34<br />

GND<br />

Q3<br />

FDZ193P<br />

A1<br />

GND GND<br />

TP5<br />

GND<br />

C39 0.1UF<br />

GND<br />

Coin cell.<br />

C42<br />

C43<br />

0.1UF<br />

0.1UF<br />

GND<br />

GND<br />

BATTFET<br />

(active high)<br />

R26 0<br />

BATTISNS<br />

B12<br />

BATTISNSCC<br />

K7<br />

C22<br />

CFP<br />

10UFK8<br />

CFM<br />

VCC_BP<br />

R1 0.02<br />

C1 C2<br />

10UF 2.2uF<br />

GND<br />

3V_VGEN2<br />

K2<br />

L2 SPIVCC<br />

R14 100K<br />

DNP<br />

M2<br />

J2<br />

H2<br />

H4<br />

CS<br />

CLK<br />

MOSI<br />

MISO<br />

GNDSPI<br />

SPI/I2C<br />

interface<br />

R15<br />

2.775V C25 2.2UF VCORE<br />

GND<br />

A9<br />

VCORE<br />

4.7K 1.5V C27 2.2UF VCOREDIG B9<br />

VCOREDIG Reference<br />

1.2V C28 0.1UF REFCORE D7<br />

B8<br />

Generation<br />

REFCORE<br />

GNDCORE<br />

GND<br />

GND<br />

GND<br />

1<br />

VCCA<br />

2<br />

A<br />

R18 DNP 0<br />

R21 0<br />

3<br />

GND<br />

6<br />

VCCB<br />

4<br />

B<br />

NC 5<br />

TP4<br />

C37 2.2UF<br />

R4 0.02<br />

GND<br />

VCOREDIG R23 DNP 0<br />

R24 0<br />

GND VCORE R28 DNP 0<br />

VCOREDIG R29 0<br />

R30 DNP 0<br />

GND<br />

CHRGISNS<br />

CHRGCTRL<br />

CHRGCTRL1<br />

TO-2.0A<br />

R20 10M<br />

Y1<br />

TP59<br />

GND 2<br />

1GND<br />

TP8<br />

R22<br />

GND<br />

C44<br />

C45<br />

32.768KHz<br />

0<br />

GPO1 1V2_RTC<br />

15pF<br />

15pF<br />

2<br />

D1<br />

B1<br />

B2<br />

A2<br />

LED_ORANGE<br />

PWRON2<br />

1<br />

A1 C1<br />

C2<br />

R27 4.7K<br />

R25 0<br />

Figure 7. MC13892 Schematic<br />

5V Selection<br />

ECKIL 4,9<br />

C46<br />

RESET_IN_B 4,9,15<br />

POR_B 4,9<br />

3V_VGEN2<br />

1uF 1V2_RTC<br />

U5<br />

GND<br />

5<br />

VCC<br />

1<br />

PMIC_ON_REQ 4,9<br />

WDOG_B 4,8<br />

PWR_INT(GP4_18) 4,8<br />

2<br />

PWRON3<br />

PWRON1<br />

4,15<br />

4<br />

4,9 Open-drain required<br />

3<br />

GND<br />

NC7SP125P5X<br />

GND<br />

1.2V LPDDR2<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

16 <strong>Freescale</strong> <strong>Semiconductor</strong><br />

Q1<br />

FDZ193P<br />

5V_APL<br />

GND<br />

C6<br />

0.1UF<br />

C2<br />

A1 C1<br />

A2<br />

B2<br />

B1<br />

R6 0<br />

DNP<br />

C7<br />

10UF<br />

C8 C9<br />

10UF 10UF<br />

GND<br />

U2 GND GND MC13892<br />

R8 10K R9<br />

10K<br />

Battery<br />

Interface &<br />

Protection<br />

J6<br />

GND<br />

GNDADC<br />

R320<br />

DNP<br />

4,5<br />

0<br />

TP3<br />

BATT_NTC<br />

K9<br />

GND K10<br />

M11<br />

ADIN5<br />

ADIN6<br />

ADIN7<br />

4,15 TOUCH_X0<br />

4,15 TOUCH_X1<br />

4,15 TOUCH_Y0<br />

4,15 TOUCH_Y1<br />

C20<br />

J9<br />

J12<br />

M12<br />

L12<br />

M13<br />

N12<br />

N13<br />

TSX1<br />

TSX2<br />

TSY1<br />

TSY2<br />

TSREF_1<br />

TSREF_2<br />

TSREF_3<br />

Touch<br />

Screen<br />

interface<br />

2.2UF<br />

E11<br />

ADTRIG<br />

A10<br />

BATT<br />

E6<br />

E1<br />

UID<br />

UVBUS<br />

F2<br />

VBUSEN<br />

G2<br />

VINUSB<br />

D1<br />

VUSB<br />

D9<br />

LICELL<br />

BATTISNS C13<br />

VUSB<br />

100mA<br />

GNDSUB1<br />

GNDSUB2<br />

GNDSUB3<br />

GNDSUB4<br />

GNDSUB5<br />

GNDSUB6<br />

GNDSUB7<br />

GNDSUB8<br />

GNDSUB9<br />

F6<br />

F7<br />

F8<br />

G6<br />

G7<br />

G8<br />

H6<br />

H7<br />

H8<br />

BATTFET D10<br />

B10<br />

BP<br />

BPSNS D12<br />

CHRGISNS C12<br />

A12<br />

CHRGCTRL2_1<br />

B11<br />

CHRGCTRL1<br />

CHRGRAW A11<br />

A13<br />

CHRGCTRL2_2 B13<br />

CHRGCTRL2_3<br />

N6<br />

XTAL1<br />

Charger<br />

Interface<br />

and Control<br />

CHRGLED E9<br />

CHRGSE1B D8<br />

GNDCHRG E8<br />

XTAL2<br />

GNDRTC<br />

GNDCTRL<br />

MODE<br />

PUMS1<br />

PWRON1<br />

PWRON2<br />

PWRON3<br />

STANDBY<br />

INT<br />

WDI<br />

RESETBMCU<br />

RESETB<br />

STANDBYSEC<br />

N5<br />

M5<br />

H9<br />

A8<br />

G9<br />

D13<br />

E10<br />

J8<br />

J5<br />

E12<br />

G10<br />

F11<br />

F12<br />

H12<br />

NC A7<br />

LEDMD D5<br />

LEDAD F5<br />

B6<br />

LEDKP<br />

GNDSWLED A6<br />

Backlight<br />

LED Drive<br />

CLK32K<br />

CLK32KMCU<br />

VSRTC<br />

K5<br />

J4<br />

M4<br />

LEDR B7<br />

LEDG E4<br />

B5<br />

LEDB<br />

GNDLED E5<br />

D6<br />

DVS1<br />

DVS2<br />

B3<br />

J7<br />

GNDREG1<br />

GNDREG2<br />

VGEN3_2<br />

B2<br />

F10 GPO1<br />

F9 GPO2<br />

G12<br />

GPO3<br />

GPO4<br />

H5<br />

G5<br />

GNDREG3<br />

DNP<br />

Q2<br />

FDZ193P<br />

SH30<br />

5V_APL<br />

APL_GPIO2 5<br />

CHGR_DET_B_TO_PMIC 8<br />

C10<br />

4.7uF<br />

C19 10UF<br />

3 2<br />

VCC_BP<br />

C11<br />

4.7uF<br />

5V_APL<br />

C12<br />

4.7uF<br />

4<br />

SH88 0<br />

1<br />

2<br />

5<br />

6<br />

R313 0<br />

DNP<br />

C13<br />

4.7uF<br />

4<br />

1<br />

2<br />

5<br />

6<br />

4<br />

5V_MAIN<br />

USB_5V<br />

1<br />

2<br />

5<br />

6<br />

4<br />

1<br />

2<br />

5<br />

6<br />

1V8_SW4<br />

GND GND GND<br />

GND<br />

Put 4.7UF capacitors at pins G13, H13, H1 and J1.<br />

K4<br />

PWGTDRV1<br />

Tri-Color<br />

LED Drive<br />

PWGTDRV2<br />

VCC_BP<br />

(PUS_4)<br />

+/- 1%<br />

1V_SW1<br />

SW1<br />

1050mA<br />

Buck<br />

VCC_BP<br />

1.5UH<br />

1L2 R10<br />

2<br />

0<br />

C17 10UF<br />

SW1<br />

GND<br />

(PUS_0)<br />

1V2_SW2<br />

SW2<br />

800mA<br />

Buck<br />

1L3 R11<br />

VCC_BP<br />

2.2UH 2<br />

0<br />

C18 10UF<br />

GND<br />

SW2<br />

(PUS_5)<br />

1V2_SW3<br />

SW3<br />

800mA<br />

Buck<br />

1L4 VCC_BP<br />

2.2UH 2<br />

GND<br />

SW3<br />

(PUS_1)<br />

1V8_SW4<br />

SW4<br />

800mA<br />

Buck<br />

1L5 2.2UH 2<br />

C21 10UF<br />

GND<br />

SW4<br />

VCC_BP L6 3.3uH<br />

VCC_BP SWBST<br />

1<br />

D2<br />

2.2uH 2 is for optional<br />

VCC_BP<br />

SWBST<br />

350mA<br />

2 1<br />

MBR120LSFT1G<br />

C23 10uF<br />

GND<br />

3 NSS12100XV6T1G<br />

2V775_VVIDEO<br />

Boost<br />

VVIDEO<br />

350mA<br />

VUSB2<br />

50mA<br />

VAUDIO<br />

150mA<br />

VVIOHI<br />

100mA<br />

VVIDEODRV<br />

VCC_BP C24 2.2UF<br />

GND<br />

C26 2.2UF<br />

VCC_BP<br />

GND<br />

3V_VAUDIO<br />

UNUSED<br />

VCC_BP C31 2.2UF<br />

2V775_VIOIH<br />

(PUS_2) UNUSED<br />

C32 2.2UF GND<br />

VCC_BP<br />

Q6<br />

(PUS_9) 2V5_VUSB2<br />

NOTE: (PUS_X) means the Power Up<br />

Sequence index number during turn on.<br />

VPLL<br />

50mA<br />

VDIG<br />

50mA<br />

VCAM<br />

250mA<br />

VCC_BP C33<br />

C34<br />

VCAMDRV<br />

C35<br />

1V8_ANA_PLL<br />

GND(PUS_6)<br />

VCC_BP<br />

2.2UF<br />

Q7<br />

1V2_DIG<br />

NSS12100XV6T1G<br />

(PUS_7)<br />

DNP<br />

2.2UF GND<br />

3 UNUSED<br />

VCC_BP<br />

3V_VCAM<br />

GND<br />

Q8<br />

2.2UF<br />

NSS12100XV6T1G<br />

GND<br />

3<br />

VCC_BP<br />

VSD<br />

250mA<br />

VGEN1<br />

200mA<br />

VSDDRV<br />

C36<br />

VGEN1DRV<br />

C38<br />

2.2UF<br />

2.2UF<br />

GND<br />

GND<br />

3V15_VSD<br />

3<br />

Q9<br />

NSS12100XV6T1G<br />

DNP VCC_BP<br />

UNUSED<br />

3V_VGEN1 Q10<br />

NSS12100XV6<br />

3<br />

VGEN2<br />

350mA<br />

VGEN3<br />

50mA<br />

VGEN2DRV<br />

C40<br />

VGEN3DRV<br />

2.2UF<br />

GND<br />

VCC_BP<br />

Q11<br />

NSS12100UW3<br />

(PUS_3)<br />

3V_VG<br />

C41<br />

DNP<br />

2.2UF 1 UNUSED<br />

1V8_VGEN3<br />

GND<br />

M7<br />

SW1IN G13<br />

F13<br />

SW1OUT<br />

SW1FB E13<br />

GNDSW1<br />

H10<br />

SW2IN H13<br />

J13<br />

SW2OUT J10<br />

SW2FB K13<br />

GNDSW2<br />

SW3IN H1<br />

SW3OUT G1<br />

F4<br />

SW3FB F1<br />

GNDSW3<br />

SW4IN J1<br />

K1<br />

SW4OUT<br />

SW4FB L1<br />

GNDSW4<br />

G4<br />

SWBSTIN A4<br />

B4<br />

SWBSTOUT<br />

SWBSTFB D4<br />

A5<br />

GNDSWBST<br />

VVIDEODRV<br />

VVIDEO<br />

K12<br />

L13<br />

VINUSB2<br />

VUSB2_1<br />

VAUDIO<br />

A3<br />

A1<br />

N8<br />

VINIOHI N10<br />

VIOHI N9<br />

VPLL<br />

VINDIG<br />

E2<br />

M9<br />

VDIG M8<br />

VCAMDRV M6<br />

VCAM K6<br />

VSDDRV C2<br />

VSD D2<br />

VGEN1DRV M10<br />

VGEN1 N11<br />

VGEN2DRV N4<br />

VGEN2 M3<br />

VINGEN3DRV N3<br />

VGEN3_1 M1<br />

VUSB2_2<br />

VUSB2_3<br />

A2<br />

B1<br />

VINPLL C1<br />

PUMS2<br />

E7<br />

VGEN3_3<br />

N1<br />

N2<br />

VINAUDIO N7<br />

4<br />

SH85<br />

0<br />

1<br />

2<br />

5<br />

6<br />

GND

VSOURCE<br />

SH1<br />

0<br />

C47 + C48 + C49 + C50<br />

100UF 100UF 100UF 4.7uF<br />

Note: Freq=1Mhz, Tsoftstart=3.2ms<br />

3V_VGEN2<br />

R33<br />

10.0K<br />

SH71<br />

DNP<br />

C51<br />

0.1UF<br />

VDDI<br />

GND<br />

U7<br />

18<br />

19<br />

20<br />

GND<br />

5<br />

VIN1<br />

NC1<br />

VIN2<br />

BOOT<br />

21<br />

DDR2/DDR3 Power<br />

0.7V<br />

GND<br />

VDDI<br />

24<br />

VDDI<br />

PG<br />

MC34713EP<br />

4<br />

8<br />

NC2<br />

7<br />

VREFIN<br />

VOUT<br />

11<br />

3<br />

ILIM<br />

2<br />

FREQ<br />

COMP<br />

6<br />

SD<br />

9<br />

INV 10<br />

R31<br />

9.31K<br />

PVIN1 PVIN2 PVIN3<br />

C53 0.1UF<br />

C54<br />

0.1UF<br />

R34 5.1K<br />

SW1<br />

SW2<br />

SW3<br />

15<br />

16<br />

17<br />

1 L7<br />

1.0UH<br />

2<br />

R37 0<br />

C55<br />

R38 15K<br />

R41 10K<br />

R42 DNP4.99K<br />

20PF C56 560PF<br />

PGND1 PGND2 PGND3GND1<br />

GND2<br />

C61<br />

12 13 14 1 25<br />

0.1UF<br />

1V8_SW4<br />

22<br />

23<br />

Figure 8. 3.15V Buck Regulator<br />

SH85<br />

0<br />

GND<br />

SH86<br />

C3<br />

10uF<br />

SH84 DNP<br />

3<br />

U1<br />

LTC3409EDD<br />

VIN1<br />

MODE<br />

5<br />

DNP 7<br />

RUN<br />

4<br />

VIN2<br />

2<br />

GND<br />

9<br />

E_PAD<br />

Vout = 0.613 * [ R(Vout-Vfb) / R(Vfb-Gnd) + 1 ]<br />

Vout = 1.2V for R(Vout-Vfb) = 127K & R(Vfb-Gnd)=133K<br />

Figure 9. 1.2V Buck Regulator<br />

VDDO2P5 LDO<br />

VSOURCE<br />

C16<br />

2.2uF<br />

GND<br />

VDD2P5 LDO<br />

3V_VGEN2<br />

GND<br />

C15<br />

100 PF<br />

Figure 10. 2.5V LDO Regulators<br />

i.MX50 Power Management Design with MC13892<br />

Vout = 0.7 * [ R(sw-inv) / R(inv-gnd) + 1 ]<br />

Vout = 3.14V for R39=17.4K, R44=4.99K<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 17<br />

GND<br />

SW 6<br />

1<br />

VFB<br />

SYNC 8<br />

Q4<br />

IRLML6401<br />

VSOURCE<br />

3 2<br />

R306<br />

100K<br />

GND<br />

1V2_SW2<br />

R13 10K 1<br />

10K<br />

R16<br />

C30<br />

100 PF<br />

1<br />

U3<br />

VIN<br />

5<br />

VOUT<br />

C14<br />

4<br />

BYP<br />

4.7uF<br />

3<br />

ON/OFF<br />

2<br />

GND<br />

LP2992<br />

GND<br />

1<br />

2 3<br />

Q5<br />

MMBT3904<br />

R307<br />

100K<br />

1<br />

U4<br />

VIN<br />

5<br />

VOUT<br />

C29<br />

4<br />

BYP<br />

22UF<br />

3<br />

ON/OFF<br />

2<br />

GND<br />

LP2992<br />

GND<br />

L1 2.2UH<br />

1 2<br />

SH87<br />

DNP<br />

R2<br />

127.0K<br />

R5<br />

133.0K<br />

VDDO2P5<br />

VDD2P5<br />

1V2_DDR<br />

C4<br />

20PF C5<br />

10uF<br />

R35<br />

4.12K<br />

C57<br />

470pF<br />

R39<br />

17.4K<br />

R44<br />

4.99K<br />

C58 +<br />

100UF<br />

SH2<br />

0<br />

C59 + C60 +<br />

100UF 100UF<br />

DCDC_3V15

i.MX50 Power Management Design with MC13892<br />

BOOT_MODE0<br />

BOOT_MODE1<br />

R73<br />

10K<br />

GND<br />

4,6 PMIC_STBY_REQ<br />

4,6 PMIC_ON_REQ<br />

C148<br />

18PF<br />

DNP<br />

4,6<br />

4,6 POR_B<br />

RESET_IN_B<br />

4,6,15<br />

QZ1<br />

1 2<br />

32.768KHZ<br />

DNP<br />

GND<br />

ECKIL<br />

C149<br />

18PF<br />

DNP<br />

AD2<br />

POR_B<br />

AB1<br />

AB2 BOOT_MODE0<br />

BOOT_MODE1<br />

RESET_IN_B<br />

AC1<br />

AC2<br />

TEST_MODE<br />

Y2<br />

ECKIL<br />

CKIL<br />

W2<br />

W1<br />

PMIC_STBY_REQ<br />

PMIC_ON_REQ<br />

Y1<br />

SH31<br />

SH0603<br />

DNP<br />

U12C<br />

PCIMX508DJV1A<br />

i.MX50 - CONTROL PINS<br />

Figure 11. i.MX50 Control Signals<br />

4.5 MC13892 PCB Layout Example<br />

NVCC_RESET<br />

NVCC_RTC<br />

NVCC_JTAG<br />

JTAG_TCK JTAG_TCK<br />

JTAG_TMS<br />

JTAG_TDI<br />

JTAG_TDO<br />

JTAG_TRST_B<br />

W4<br />

JTAG_TMS<br />

JTAG_TDI<br />

JTAG_TDO<br />

Y4<br />

AA4<br />

U7<br />

JTAG_TRSTB<br />

JTAG_MOD<br />

AA5<br />

V7<br />

CKIH AA6 SH33 DNP<br />

The following example shows the PMIC layout section for a reference design of the i.MX50 using the MC13892<br />

power management. It is design in 10 layers with 4 inner planes (GND and PWR) form layer 4 to layer 7. For<br />

simplicity, only top, bottom and Inner signal layers are shown in figures x to y.<br />

1<br />

TP<br />

SH<br />

R31910<br />

4<br />

C48<br />

TP4<br />

TP5<br />

C47 L4<br />

L5<br />

C49<br />

C21JP3<br />

SH13<br />

R93<br />

R92<br />

C37<br />

R316<br />

JP4<br />

1<br />

R66<br />

1<br />

S<br />

R315<br />

L6<br />

1<br />

D2<br />

1<br />

1<br />

1C40<br />

R20<br />

C411<br />

R76<br />

C44<br />

C45<br />

R67<br />

R62<br />

S<br />

U2<br />

S<br />

AC5<br />

EXTAL<br />

XTAL<br />

AD5<br />

Y1<br />

Figure 12. Top Fabrication Drawing<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

18 <strong>Freescale</strong> <strong>Semiconductor</strong><br />

C7<br />

1<br />

GND<br />

Y2<br />

4 GND 3<br />

1 2<br />

GND<br />

C152<br />

15PF<br />

1<br />

C<br />

R74 1.0M<br />

24MHZ<br />

C38<br />

C31<br />

R1<br />

TP8<br />

C22TP3<br />

C154<br />

1<br />

Y3<br />

TP15<br />

GND<br />

JTAG_MOD<br />

1V8_SW4<br />

GND<br />

R85<br />

10K<br />

DNP<br />

R86<br />

1K<br />

OSC.<br />

Y3<br />

VCC<br />

10K<br />

C153<br />

15PF 22.5792MHZ<br />

DNP<br />

4<br />

3<br />

OUT<br />

DGND 2<br />

EN/DIS<br />

1<br />

AL2<br />

1<br />

1<br />

R76<br />

1V8_ANA_PLL<br />

C154<br />

0.1UF<br />

GND<br />

R16<br />

1U6<br />

U4<br />

TP59<br />

TP17<br />

TP20<br />

SH31<br />

R21<br />

L3<br />

C2<br />

1<br />

C233<br />

TP18<br />

101<br />

C1<br />

SH79<br />

J20<br />

TP23<br />

TP21<br />

5<br />

C30<br />

4<br />

1<br />

L9<br />

2<br />

JP5<br />

+<br />

C<br />

1

C121<br />

C124<br />

C1<br />

SH1<br />

C130<br />

C129<br />

C133<br />

C134<br />

20<br />

4<br />

C10<br />

C1<br />

SH6<br />

C116<br />

C114<br />

JP4<br />

C119<br />

C118<br />

C89<br />

C138<br />

10<br />

C84<br />

C148<br />

JP3<br />

SH2<br />

C19<br />

R18<br />

R19<br />

R15<br />

C75<br />

SH20<br />

R63<br />

SH26<br />

SH7<br />

Q8<br />

Q11<br />

Q10<br />

SH8<br />

40<br />

R17<br />

1<br />

1<br />

C12<br />

Q7<br />

SH4<br />

R7<br />

C35<br />

C34<br />

R320<br />

Figure 13. Bottom Fabrication Drawing<br />

Figure 14. Top Layer<br />

i.MX50 Power Management Design with MC13892<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 19<br />

C32<br />

Q6<br />

30<br />

C39<br />

R11<br />

R10<br />

Q9<br />

TP15<br />

C6<br />

C20<br />

20<br />

10<br />

R30<br />

SH83<br />

R27<br />

R25<br />

R26<br />

C43<br />

C42<br />

C29<br />

U5<br />

10<br />

2<br />

J20<br />

1<br />

2<br />

1<br />

C46<br />

BT1<br />

1<br />

1<br />

5<br />

2<br />

1<br />

R29<br />

R28<br />

C18<br />

C17<br />

1<br />

R22<br />

1<br />

5<br />

1<br />

15<br />

JP5<br />

17<br />

1<br />

1<br />

1<br />

1<br />

1<br />

2<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

C<br />

A<br />

1<br />

1<br />

1<br />

1<br />

101<br />

5<br />

4<br />

1<br />

2<br />

+<br />

1

i.MX50 Power Management Design with MC13892<br />

Figure 15. Inner Layer 2 (Signal)<br />

Figure 16. Inner Layer 3 (Signal)<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

20 <strong>Freescale</strong> <strong>Semiconductor</strong>

Figure 17. Inner Layer 8 (Signal)<br />

Figure 18. Inner Layer 9 (Signal)<br />

i.MX50 Power Management Design with MC13892<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 21

i.MX50 Power Management Design with MC13892<br />

40<br />

2<br />

20<br />

10<br />

1<br />

1<br />

1<br />

1<br />

1<br />

Figure 19. Bottom Layer<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

22 <strong>Freescale</strong> <strong>Semiconductor</strong><br />

30<br />

20<br />

10<br />

1 2<br />

1<br />

1<br />

1<br />

5<br />

2<br />

1<br />

1<br />

1<br />

15<br />

17<br />

1

i.MX50 Power Management Design with the MC34709<br />

5 i.MX50 Power Management Design with the MC34709<br />

The MC34709 is a power management IC that includes the necessary sources to supply the i.MX50. Its main<br />

features are:<br />

• Ten-bit ADC for monitoring.<br />

• Four-wire resistive touchscreen interface<br />

• Five buck converters for direct supply of the processor core and memory<br />

• One boost converter for USB OTG support<br />

• Eight LDO Regulators with internal and external pass devices for thermal budget optimization<br />

• Power control logic with processor interface and event detection<br />

• Real time clock and crystal oscillator circuitry with coin cell backup<br />

• Support for external secure real time clock on a companion system processor IC<br />

• Single SPI/I2C bus for control & register access<br />

• Four general purpose low voltage I/Os with interrupt capability<br />

• Two PWM outputs<br />

5.1 MC34709 Voltage supplies<br />

Supply Typical Application<br />

Table 6. MC34709 Voltage Supplies Summary<br />

Output Voltage<br />

(in V)<br />

Load Capability<br />

(in mA)<br />

SW1 Buck regulator for processor VDDGP domain 0.650 - 1.4375 2000<br />

SW2 Buck regulator for processor VCC domain 0.650 - 1.4375 1000<br />

SW3 Buck regulator for processor VDD domain and peripherals 0.650 - 1.425 500<br />

SW4A Buck regulator for DDR memory and peripherals 1.200 – 1.975: 2.5/3.15/3.3 500<br />

SW4B Buck regulator for DDR memory and peripherals 1.200 – 1.975: 2.5/3.15/3.3 500<br />

SW5 Buck regulator for I/O domain 1.200 – 1.975 1000<br />

SWBST Boost regulator for USB OTG 5.00/5.05/5.10/5.15 380<br />

VSRTC Secure Real Time Clock supply 1.2 0.05<br />

VPLL Quiet Analog supply 1.2/1.25/1.5/1.8 50<br />

VREFDDR DDR Ref supply 0.6-0.9V 10<br />

VDAC TV DAC supply, external PNP 2.5/2.6/2.7/2.775 250<br />

VUSB2 VUSB/peripherals supply, internal PMOS 2.5/2.6/2.75/3.0 65<br />

VUSB/peripherals external PNP 2.5/2.6/2.75/3.0 350<br />

VGEN1 General peripherals supply #1 1.2/1.25/1.3/1.35/<br />

1.4/1.45/1.5/1.55<br />

VGEN2 General peripherals supply #2, internal PMOS 2.5/2.7/2.8/2.9/3.0/<br />

3.1/3.15/3.3<br />

General peripherals supply #2, external PNP 2.5/2.7/2.8/2.9/3.0/<br />

3.1/3.15/3.3<br />

VUSB USB Transceiver supply 3.3 100<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 23<br />

250<br />

50<br />

250

i.MX50 Power Management Design with the MC34709<br />

5.2 MC34709 Power-up Sequence<br />

The MC34709 has 5 PUMS signals that enable to program the power up sequence as well as the default output<br />

voltage for specific rails, making the part suitable to supply DDR2, DDR3, LPDDR2, LVDDR3 memories with the<br />

correct power up sequence for many processors of the i.MX family. The following table shows the power up<br />

sequence and all possible voltage combinations to supply the i.MX50 in all possible modes.<br />

Table 7. Power-up Defaults<br />

i.MX50 mDDR LPDDR2 LPDDR2 mDDR LPDDR2 mDDR<br />

PUMS[4:1] 1010 1011 1100 1101 1110 1111<br />

PUMS5=0<br />

VUSB2/VGEN2<br />

PUMS5=1<br />

VUSB2/VGEN2<br />

SW1A<br />

(VDDGP)<br />

SW1B<br />

(VDDGP)<br />

SW2 (8)<br />

(VCC)<br />

SW3 (8)<br />

(VDDA)<br />

SW4A (8)<br />

(DDR/SYS)<br />

SW4B (8)<br />

(DDR/SYS)<br />

SW5 (8)<br />

(I/O)<br />

VUSB (9)<br />

Ext PNP Ext PNP Ext PNP Ext PNP Ext PNP Ext PNP<br />

Internal<br />

PMOS<br />

Internal<br />

PMOS<br />

Internal<br />

PMOS<br />

Internal<br />

PMOS<br />

Internal<br />

PMOS<br />

Internal<br />

PMOS<br />

1.1 1.1 1.1 1.1 1.1 1.1<br />

1.1 1.1 1.1 1.1 1.1 1.1<br />

1.2 1.2 1.2 1.2 1.2 1.2<br />

1.2 1.2 1.2 1.2 1.2 1.2<br />

1.8 1.2 3.15 3.15 3.15 3.15<br />

1.8 1.2 1.2 1.8 1.2 1.8<br />

1.8 1.8 1.8 1.8 1.8 1.8<br />

3.3 3.3 3.3 3.3 3.3 3.3<br />

VUSB2 2.5 2.5 2.5 2.5 2.5 2.5<br />

VSRTC 1.2 1.2 1.2 1.2 1.2 1.2<br />

VPLL 1.8 1.8 1.8 1.8 1.8 1.8<br />

VREFDDR On On On On On On<br />

VDAC 2.5 2.5 2.5 2.5 2.5 2.5<br />

VGEN1 1.2 1.2 1.2 1.2 1.2 1.2<br />

VGEN2 3.1 3.1 3.1 3.1 2.5 2.5<br />

Not used on System<br />

SWBST Off Off Off Off Off Off<br />

Notes<br />

8. The SWx node are activated in APS mode when enabled by the start-up sequencer.<br />

9. VUSB is supplied by SWBST.<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

24 <strong>Freescale</strong> <strong>Semiconductor</strong>

i.MX50 Power Management Design with the MC34709<br />

VCOREDIG, VSRTC, and VCORE, are brought up in the pre-sequencer start-up. See Figure 2<br />

System Core Active<br />

Turn On Verification<br />

Power Up Sequencer<br />

UV Masking<br />

RESETB<br />

WDI<br />

Turn On Event<br />

INT<br />

1 - Off<br />

Tap x<br />

2.0 ms<br />

Table 8. Power-up Sequence i.MX50<br />

PUMS [4:1] = [0100, 1011, 1100, 1101, 1110, 1111]<br />

0 SW2<br />

1 SW3<br />

2 SW1A/B<br />

3 VDAC<br />

4 SW4A/B, VREFDDR<br />

5 SW5<br />

6 VGEN2, VUSB2<br />

7 VPLL<br />

8 VGEN1<br />

9 VUSB<br />

Sequencer time slots<br />

8 ms 8 ms<br />

20 ms 12 ms<br />

2 - Cold Start<br />

Figure 20. Complete MC34709 Power-up Sequence<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 25<br />

128 ms<br />

WDI Pulled Low<br />

3 - Watchdog 4 - On 3- Watchdog 1 - Off<br />

Power up of the system upon a Turn On Event followed by a transition to the On state if WDI is pulled high ... or transition to Off state if WDI remains low<br />

Turn on Event is based on PWRON being pulled low<br />

= Indeterminate State<br />

ow

i.MX50 Power Management Design with the MC34709<br />

SW2<br />

SW3<br />

SW1A/B<br />

VDAC<br />

SW4A/B<br />

VREFDDR<br />

SW5<br />

VGEN2<br />

VUSB2<br />

VPLL<br />

VGEN1<br />

VUSB<br />

Power on event<br />

2ms 2ms 2ms 2ms 2ms 2ms 2ms<br />

2ms 2ms<br />

Figure 21. MC3709 Power up Sequence for i.MX50 processors.<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

26 <strong>Freescale</strong> <strong>Semiconductor</strong>

5.3 Interfacing the i.MX50 with the MC34709<br />

i.MX50 Power Management Design with the MC34709<br />

Table 9, shows all the i.MX voltage rails, their power requirements and their associated MC34709 regulator. Most of<br />

the supply domains have flexible voltage and could be adjusted or supplied with a different regulator depending on<br />

each application needs<br />

Power Rail of<br />

i.MX50<br />

NVCCSRTC 32 kHz osc. power<br />

(when chip off)<br />

VCC LP Transistor<br />

power<br />

VDDA Peripheral<br />

Memory + L2<br />

Cache power<br />

Table 9. i.MX50 voltage domain supplies with the MC34709<br />

I.MX50 MC34709<br />

Power Domain MIN TYP MAX<br />

Associated<br />

Regulator<br />

PUM[4:0]<br />

=1110<br />

Curren<br />

t (mA) PUS<br />

1.2 VSRTC 1.2 -<br />

1.2 SW2 1.2 1000 0<br />

1.2 SW3 1.2 500 1<br />

VDDAL1 L1 Cache power 1.2 SW3 1.2 500 1<br />

VDDGP Core and G<br />

Transistor power<br />

VDDO2P5 Predriver for EMI<br />

pads<br />

1 SW1A/B 1 1600 2<br />

2.5 VDAC 2.5 50 3<br />

NVCC_EMI_DRAM Power to EMI pins 1.2 SW4B 1.2 500 4<br />

VREF DRAM Reference 0.9<br />

ALL 3.3V IO NVCC 3.0 V I/Os -<br />

VDD3P0 VDD2P5 LDO<br />

input + power to<br />

Bandgap,<br />

DCDC predriver,<br />

tempsensor, 480<br />

MHz PLL<br />

USB_OTG_VDDA33 Power to USB<br />

Host<br />

USB_H1_VDDA33 Power to USB<br />

OTG<br />

All 1.8 IO NVCC 1.8 V I/Os -<br />

NVCC_RESET (LVIO) Power to<br />

POR_B,RESET_I<br />

N_B,<br />

TESTMODE, &<br />

BOOTMODE[0:1]<br />

3 SW4A 3.15 500 4<br />

3.3 VUSB 3.3 100 9<br />

3.3 VUSB 3.3 100 9<br />

1.875 or<br />

2.775<br />

SW5 1.8 1000 5<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 27

i.MX50 Power Management Design with the MC34709<br />

Power Rail of<br />

i.MX50<br />

VDD2P5 Power to 24 MHz<br />

osc, efuse, xtalok,<br />

32 kHz osc. power<br />

mux<br />

USB_OTG_VDDA25 Power to USB<br />

Host<br />

USB_H1VDDA25 Power to USB<br />

OTG<br />

2.5 VGEN2 2.5 250 6<br />

2.5 VGEN2 2.5 250 6<br />

2.5 VGEN2 2.5 250 6<br />

VDD1P8 Power to all PLLs 1.8 VPLL 1.8 50 7<br />

VDD1P2 Power to all PLL<br />

digital, 32 kHz osc.<br />

(when chip on),<br />

much of analog,<br />

digital<br />

Table 9. i.MX50 voltage domain supplies with the MC34709<br />

I.MX50 MC34709<br />

Power Domain MIN TYP MAX<br />

Associated<br />

Regulator<br />

PUM[4:0]<br />

=1110<br />

Curren<br />

t (mA) PUS<br />

1.2 VGEN1 1.2 250 8<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

28 <strong>Freescale</strong> <strong>Semiconductor</strong>

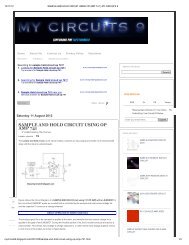

5.3.1 Interfacing Block Diagram<br />

i.MX50 Power Management Design with the MC34709<br />

The following block diagrams show all the power connections needed for the interface, as well as how the<br />

communication signals must be connected between the i.MX50 and MC34709.<br />

5.0V<br />

4.2V<br />

regulator<br />

VIN<br />

MC34709<br />

External<br />

DC/DC<br />

regulator<br />

SW1A/B<br />

SW2<br />

SW4<br />

VUSB<br />

SW5<br />

VPLL<br />

VGEN2<br />

VSW3<br />

VUSB2<br />

VDAC<br />

VSW4A<br />

VGEN1<br />

3.15 V<br />

VDDGP<br />

VCC<br />

USB_VDDA33<br />

VDD2P5<br />

VDDO25<br />

Figure 22. i.MX50 Power Interface with MC34709 Block Diagram<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 29<br />

i.MX50<br />

NVCC_EIM_DRAM<br />

POP_LPDDR2_18V<br />

NVCC_RESET<br />

NVCC_JTAG<br />

VDD1P8<br />

NVCC_KEYPAD<br />

(OPT)<br />

VDDA<br />

VDDAL1<br />

VDD3P0<br />

NVCC_MISC<br />

NVCC_SPI<br />

NVCC_SD1<br />

NVCC_SD2<br />

POP_NAND_VCC<br />

NVCC_NANDF<br />

NVCC_KEYPAD<br />

NVCC_SSI<br />

NVCC_UART<br />

NVCC_LCD<br />

NVCC_EPDC<br />

VDD1P2<br />

Peripherals<br />

CODEC<br />

HDMI<br />

ETHERNET<br />

3G PCIe<br />

RS-232

i.MX50 Power Management Design with the MC34709<br />

MC34709<br />

RESETBMCU<br />

RESETB<br />

STANDBY<br />

POWERON1<br />

WDI<br />

INT<br />

UID<br />

CKL<br />

MISO/SDA<br />

Figure 23. i.MX50 Control Interface with MC34709 Block Diagram<br />

5.3.1.1 3.15 V DC-DC power supply<br />

SWx<br />

POR_B<br />

WDOG<br />

CLK32MCU CLK<br />

PUMS1<br />

PUMS2<br />

PUMS3<br />

PUMS4<br />

PUMS5<br />

SWx<br />

SWx<br />

GPIOX_X<br />

i.MX50<br />

RESET_IN_B<br />

PMIC_STBY_REQ<br />

PMIC_ON_REQ<br />

USB_OTG_ID<br />

CSPI_SCLK<br />

CSPI_MISO/MOSI<br />

For system stability, it is recommended that you use an extra 3.15 V DCDC power supply to support large current<br />

requirements (for example a 3G module or Wi-fi card). The MC34709 has limited 3.15 V output ability to supply al<br />

peripherals, however, in cases where Ethernet, 3G, or Wi-fi are not required, this buck converter may be eliminated<br />

from the power three.<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

30 <strong>Freescale</strong> <strong>Semiconductor</strong><br />

VDC

5.3.2 Interface Power-up Sequence<br />

The resulting power-up sequence of the interface is shown in the following figure<br />

Peripherals<br />

CODEC<br />

HDMI<br />

ETHERNET<br />

3G PCIe<br />

RS-232<br />

VDDA<br />

VDDA1<br />

Figure 24. Power up Sequence Flow Chart<br />

i.MX50 Power Management Design with the MC34709<br />

VCC SW2<br />

VDDGP<br />

VDDO2P5<br />

VDD3P0<br />

NVCC_MISC<br />

NVCC_SPI<br />

NVCC_SD1<br />

NVCC_SD2<br />

POP_NAND_VCC<br />

NVCC_NANDP<br />

NVCC_KEYPAD<br />

NVCC_SSI<br />

NVCC_UART<br />

NVCC_LCD<br />

NVCC_EPDC<br />

POP_LPDDR2_18V<br />

NVCC_RESET<br />

NVCC_JTAG<br />

VDD2P5<br />

USB_VDDA25<br />

VDD1P8<br />

VDD1P2<br />

HDMI (perpheral)<br />

USB_VDDA33<br />

Power Management Design Guidelines for the i.MX50x Family of Microprocessors, Rev. 1.0<br />

<strong>Freescale</strong> <strong>Semiconductor</strong> 31<br />

3.15V<br />

DC-DC<br />

regulator<br />

SW3<br />

SW1A/B<br />

VDAC<br />

SW4A<br />

SW4B<br />

VREFDDR<br />

SW5<br />

VGEN2<br />

VUSB2<br />

VPLL<br />

VGEN1<br />

VUSB

i.MX50 Power Management Design with the MC34709<br />

5.4 Application Example with the MC34709<br />

The following schematic is simplified application example for interfacing the MC34709 with an i.MX50 processor.<br />

note that this schematic only includes the block related to the power section as well as power management<br />

controlling signals.<br />

5_VGEN2<br />

DCDC_3V15<br />

3V15_SW4A_CPU<br />

VUSB2_2V5 2V5_VGEN2<br />

0<br />

R92<br />

R479 0 DNP<br />

1V8_VPLL<br />

0<br />

1V2_VGEN1<br />

0<br />

C95<br />

68uFDNP<br />

2V5_VGEN2 3V15_SW4A_CPU<br />

DNP 0<br />

C96<br />

DNP<br />

0.1UF<br />

GND<br />

3V15_SW4A_CPU<br />

3V15_SW4A_CPU<br />

3V15_SW4A_CPU<br />

3V15_SW4A<br />

3V15_SW4A_CPU<br />

R368 0.001<br />

0<br />

DNP 0<br />

R95<br />

R466 0 DNP<br />

3V15_SW4A_CPU<br />

SH12<br />

DNP<br />

3V15_SW4A_CPU<br />

3V15_SW4A_CPU<br />

3V15_SW4A_CPU<br />

R412<br />

C63<br />

R462<br />

0.1UF<br />

R499<br />

GND<br />

C68<br />

0.1UF<br />

VDD3P0 U5<br />

VDD3P0<br />

VDD2P5 V5<br />

VDD2P5<br />

R93<br />

C84<br />

GND<br />

C69<br />

VDD1P8 V6<br />

VDD1P8<br />

0.1UF 22UF<br />

GND<br />

C90<br />

VDD1P2 U6<br />

C91<br />

VDD1P2<br />

22UF 0.1UF<br />

GND<br />

1V8_SW5<br />

0 R463<br />

C76<br />

Not used (tied off to 1.8V)<br />

0.1UF<br />

VDD_DCDCI R7<br />

VDD_DCDCI<br />

R465 0<br />

GND<br />

GND<br />

C97<br />

0.1UF<br />

C110<br />

0.1UF<br />

C114<br />

0.1UF<br />

GND<br />

U6E<br />

GND<br />

DNP L10<br />

2<br />

2.2UH<br />

1 VDD_DCDCO T6<br />

VDD_DCDCO<br />

R6<br />

GND_DCDC<br />

H5<br />

NVCC_KEYPAD<br />

J5<br />

NVCC_MISC<br />

L5<br />

NVCC_UART<br />

i.MX50 - POWER<br />

GND<br />

C124<br />

0.1UF<br />

GND<br />

C118<br />

0.1UF<br />

C119<br />

0.1UF<br />

C120<br />

0.1UF<br />

C121<br />

0.1UF<br />

NVCC_EPDC<br />

C122 C123<br />

0.01UF 10UF<br />

3V15_SW4A_CPU<br />

3V15_SW4A_CPU<br />

GND<br />

GND<br />

3V3_USB 3V15_SW4A_CPU C125<br />

C127<br />

C126<br />

0.1UF<br />

USB_H1_VDDA33<br />

USB_3V3 R98 0<br />

22UF<br />

0.01UF<br />

GND<br />

C128<br />

0.1UF<br />

C129<br />

0.1UF<br />

GND<br />

PLace close to MX50<br />

C130 C131<br />

GND<br />

VUSB2_2V5<br />

0.1UF 0.1UF<br />

USB_2V5<br />

R100 0<br />

GND<br />

C133<br />

0.1UF<br />

C134<br />

GND<br />

1V2_RTC<br />

0.1UF<br />

NVCC_SRTC<br />

SH14<br />

DNP<br />

GND<br />

C136<br />

0.1UF<br />

GND<br />

3V15_SW4A_CPU<br />

NVCC_JTAG<br />

GND<br />

C137<br />

1V8_SW5<br />

0.1UF<br />

R459 0<br />

C138<br />

0.1UF<br />

GND<br />

1V8_SW5 3V15_SW4A_CPU<br />

NVCC_RESET<br />

GND<br />

C139<br />

0.1UF<br />

R461 0 DNP<br />

W11<br />

F9<br />

NVCC_EPDC1 F10<br />

NVCC_EPDC2<br />

F11<br />

NVCC_EPDC3<br />

F12<br />

NVCC_EPDC4<br />

P10<br />

NVCC_LCD<br />

P12<br />

NVCC_NANDF1<br />

USB_H1_VDDA25_1<br />

P5<br />

NVCC_SD2<br />

N5<br />

NVCC_SD1<br />

M5<br />

NVCC_SPI<br />

Y9<br />

USB_OTG_VDDA25_1 W9<br />

USB_OTG_VDDA33 Y11<br />

P11<br />

NVCC_NANDF2<br />

NVCC_SRTC R5<br />

K5<br />

NVCC_SSI<br />

NVCC_JTAG P9<br />

NVCC_RESET P6<br />

SH10<br />

DNP<br />

R99 0 DNP<br />

C132<br />

0.1UF<br />

C135<br />

0.1UF<br />

R101 0 DNP<br />

R460 0<br />

MCIMX508<br />

T7<br />

GND_KEL<br />

VSS1<br />

VSS2<br />

VSS3<br />

VSS4<br />

VSS5<br />

VSS6<br />

VSS7<br />

VSS8<br />

VSS9<br />

VSS10<br />

VSS11<br />

VSS12<br />

VSS13<br />

VSS14<br />

VSS15<br />

VSS16<br />

VSS17<br />

VSS18<br />

VSS19<br />

VSS20<br />

VSS21<br />

VSS22<br />

VSS23<br />

VSS24<br />