Audio Codec '97 Revision 2.1

Audio Codec '97 Revision 2.1

Audio Codec '97 Revision 2.1

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

AC ‘97 Component Specification <strong>Revision</strong> <strong>2.1</strong><br />

D.4 AC ’97 <strong>2.1</strong> Power Management<br />

D.4.1 Power Management “D State” Mappings for <strong>Audio</strong> <strong>Codec</strong>s<br />

The ACPI and PCI Bus Power Management Interface specifications define a standard set of device power<br />

management states (D0 – D3). An audio device driver written to comprehend these power management<br />

specifications must map each supported system-side D state to an audio <strong>Codec</strong>-specific power savings mode using<br />

the PR bits.<br />

A high-level set of expectations for the mapping of D States to audio feature availability, power consumption,<br />

resume latency, etc., is available in the <strong>Audio</strong> Device Class Power Management Reference Specification located at:<br />

http://www.microsoft.com/hwdev/download/audpmspc.rtf<br />

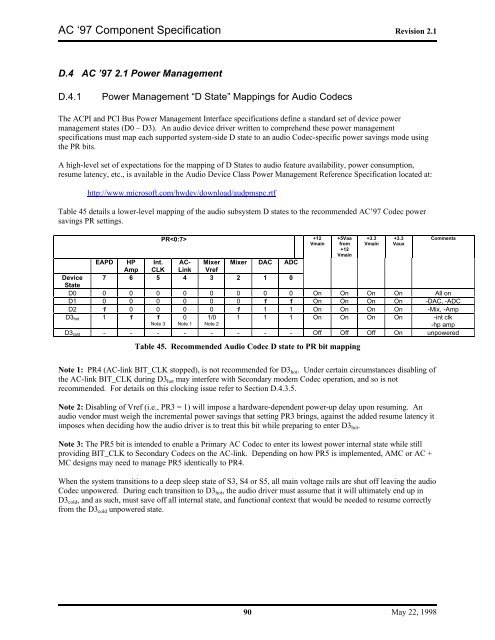

Table 45 details a lower-level mapping of the audio subsystem D states to the recommended AC’97 <strong>Codec</strong> power<br />

savings PR settings.<br />

PR<br />

90<br />

+12<br />

Vmain<br />

+5Vaa<br />

from<br />

+12<br />

Vmain<br />

+3.3<br />

Vmain<br />

+3.3<br />

Vaux<br />

May 22, 1998<br />

Comments<br />

EAPD HP Int. AC- Mixer Mixer DAC ADC<br />

Amp CLK Link Vref<br />

Device<br />

State<br />

7 6 5 4 3 2 1 0<br />

D0 0 0 0 0 0 0 0 0 On On On On All on<br />

D1 0 0 0 0 0 0 1 1 On On On On -DAC, -ADC<br />

D2 1 0 0 0 0 1 1 1 On On On On -Mix, -Amp<br />

D3hot 1 1 1 0 1/0 1 1 1 On On On On -int clk<br />

Note 3 Note 1 Note 2<br />

-hp amp<br />

D3cold - - - - - - - - Off Off Off On unpowered<br />

Table 45. Recommended <strong>Audio</strong> <strong>Codec</strong> D state to PR bit mapping<br />

Note 1: PR4 (AC-link BIT_CLK stopped), is not recommended for D3hot. Under certain circumstances disabling of<br />

the AC-link BIT_CLK during D3hot may interfere with Secondary modem <strong>Codec</strong> operation, and so is not<br />

recommended. For details on this clocking issue refer to Section D.4.3.5.<br />

Note 2: Disabling of Vref (i.e., PR3 = 1) will impose a hardware-dependent power-up delay upon resuming. An<br />

audio vendor must weigh the incremental power savings that setting PR3 brings, against the added resume latency it<br />

imposes when deciding how the audio driver is to treat this bit while preparing to enter D3hot.<br />

Note 3: The PR5 bit is intended to enable a Primary AC <strong>Codec</strong> to enter its lowest power internal state while still<br />

providing BIT_CLK to Secondary <strong>Codec</strong>s on the AC-link. Depending on how PR5 is implemented, AMC or AC +<br />

MC designs may need to manage PR5 identically to PR4.<br />

When the system transitions to a deep sleep state of S3, S4 or S5, all main voltage rails are shut off leaving the audio<br />

<strong>Codec</strong> unpowered. During each transition to D3hot, the audio driver must assume that it will ultimately end up in<br />

D3cold, and as such, must save off all internal state, and functional context that would be needed to resume correctly<br />

from the D3cold unpowered state.