Jennifer Zhao - EEWeb

Jennifer Zhao - EEWeb

Jennifer Zhao - EEWeb

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

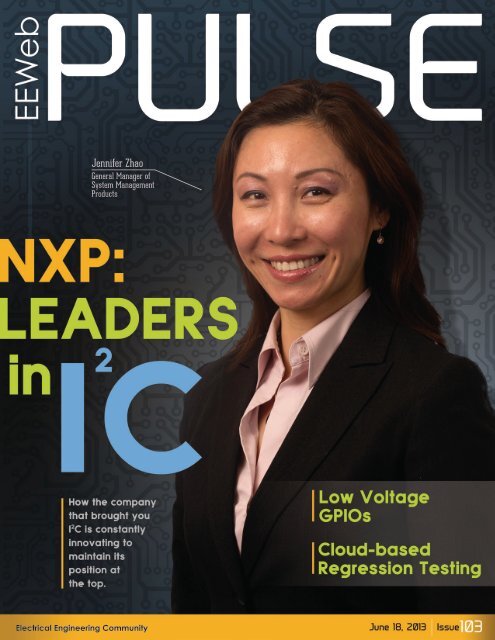

<strong>Jennifer</strong> <strong>Zhao</strong><br />

General Manager of<br />

System Management<br />

Products<br />

Electrical Engineering Community

Bringing your<br />

concepts to reality<br />

is as easy as...<br />

1.<br />

Create schematics, technical diagrams,<br />

and flowcharts using your browser.<br />

• 600+ Symbol Library<br />

• Share Schematics Online<br />

• Export High Quality Images<br />

digikey.com/schemeit<br />

2.<br />

Free and easy-to-use circuit simulator<br />

that runs in your browser.<br />

• SPICE Simulator<br />

• AC/DC/Transient Sims<br />

• Waveform Viewer<br />

partsim.com<br />

3.<br />

Full featured online CAD application<br />

for designing and manufacturing<br />

electronics hardware.<br />

• Schematic Capture<br />

• PCB Layout<br />

• BOM Integration<br />

pcbweb.com<br />

<br />

Visit: digikey.com/schemeit • partsim.com • pcbweb.com<br />

Copyright ©2013 Aspen Labs LLC.<br />

28<br />

18<br />

PULSE<br />

4<br />

8<br />

<strong>Jennifer</strong> <strong>Zhao</strong><br />

GENERAL MANAGER OF SYSTEM<br />

MANAGEMENT PRODUCTS AT NXP<br />

A conversation about how the inventors of I 2 C are<br />

constantly innovating to remain industry leaders.<br />

NXP’s I 2 C GPIO Family<br />

This new family of devices features Agile I/O,<br />

which helps integrate common system functions<br />

within the semiconductor.<br />

Featured Products<br />

This week’s latest products from <strong>EEWeb</strong>.<br />

Cloud-based Regression<br />

Testing for Chip Design<br />

This test allows designers to spot last minute<br />

tweaks or design flaws in a module.<br />

Sudoku: A Logical Test<br />

How to build a Sudoku program in the Java<br />

coding language.<br />

Challenges for<br />

ESD-Robust Design<br />

An overview of design challenges in state-ofthe-art<br />

analog technologies.<br />

CONTENTS<br />

4<br />

8<br />

Visit: eeweb.com<br />

12<br />

18<br />

24<br />

28<br />

RTZ<br />

35<br />

Return to Zero Comic<br />

3

PULSE<br />

NXP Semiconductors provides high performance mixed signal and standard product<br />

solutions. The company was formerly known as Philips Semiconductors, which is credited<br />

for inventing the I 2 C interface over 30 years ago. To this date, the company maintains its<br />

position as the number one supplier of I 2 C solutions and is determined to keep it<br />

that way.<br />

<strong>Jennifer</strong> <strong>Zhao</strong> started working at Philips Semiconductors as a Regional Marketing<br />

Manager for microcontrollers and then moved to logic and interface products. Her role<br />

within the company changed throughout the years, moving into higher level sales<br />

and marketing positions to better her understanding of customer’s needs. In 2009, she<br />

became General Manager for the System Management Product Line at NXP, which<br />

is her current position at the company. We spoke with <strong>Jennifer</strong> <strong>Zhao</strong> about the key<br />

initiatives of the interface business line, about their broad I 2 C portfolio, and how the<br />

company is constantly innovating to maintain its position at the top.<br />

4 Visit: eeweb.com<br />

INTERVIEW<br />

Visit: eeweb.com<br />

5

PULSE What are the key initiatives in the<br />

interface business line?<br />

The key initiatives in my current role are<br />

maintaining NXP’s number one position in I 2 C<br />

products in the market. I’m also responsible for<br />

delivering financial targets that the company<br />

set for the product line. This includes top line<br />

revenue, gross margin, and EBITs, which<br />

stands for earnings before interest and taxes.<br />

I have also put a lot of focus on innovation<br />

and expanding our group to address some<br />

key growing markets, like the mobile sector.<br />

It’s a rapidly growing and competitive<br />

market, so you have to be fast-to-market.<br />

Of course, in order to achieve all of these<br />

goals, it’s important to have a strong team, so<br />

managing the team and the people involved<br />

is an important part of my role. At NXP, we put<br />

a lot of focus on employee engagement—we<br />

use Gallup employee engagement surveys,<br />

and we have a lot of activities around people<br />

management and engagement. With an<br />

engaged team, our chances of being a great<br />

company are greatly improved.<br />

Could you give us an overview of NXP’s<br />

system management products?<br />

The system management product line<br />

consists of a broad portfolio of I 2 C products.<br />

I believe we have the broadest portfolio of<br />

I 2 C in the market. This portfolio includes I 2 C I/O<br />

expanders, muxes and switches, bus buffers,<br />

level shifters, and bus controllers. In addition,<br />

we also have local and remote temperature<br />

sensors, constant current and voltage source<br />

LED controllers, and LED flash drivers. You can<br />

see that some of these families are really<br />

targeting mobile and computing. It’s a pretty<br />

expansive portfolio.<br />

Philips Semiconductor (now NXP)<br />

invented the I 2 C-bus in 1982. Since<br />

its creation, I 2 C has been adopted<br />

by several competitors to bring<br />

I 2 C products to the market—all of<br />

which are compatible with NXP’s<br />

original system.<br />

My experience in the embedded space has<br />

really helped me in working with this portfolio.<br />

With the interface products, we developed<br />

them around the core. The ways in which<br />

we work with the SoC microprocessors and<br />

microcontrollers is really important, so we<br />

focus primarily on the interface. It’s important<br />

to understand the trends on the core, so<br />

processors are really important for us. We<br />

also work with our microcontrollers group really<br />

closely. In some of the microcontrollers like the<br />

Cortex M0, we worked to have it support the<br />

I 2 C I/O, which is the first microcontroller of its<br />

kind to be able to support it.<br />

Do you find that you have<br />

customers that are using your<br />

interface products even if they<br />

aren’t using your processor?<br />

Yes, we do. For example, a lot of our products<br />

work well with SoC, which NXP supports. We<br />

work closely with some of the SoC vendors like<br />

Qualcomm and we also have a really strong<br />

relationship with Intel.<br />

Do a lot of your products in the<br />

interface area have development<br />

boards available?<br />

Absolutely. For all of our products, we provide<br />

demo boards. The newest one that we have<br />

is called Fast-mode Plus development kit.<br />

Basically, we have the main board connect<br />

to our microcontroller and then have multiple<br />

daughter cards so you can plug in and<br />

evaluate the parts. Pretty much, for every<br />

product, we supply a demo board, which<br />

makes it much easier for the designers to<br />

evaluate the parts.<br />

How are NXP’s system management<br />

products positioned in the market?<br />

NXP is the leading I 2 C product provider in the<br />

market. The I 2 C bus was created by Philips<br />

Semiconductor in the early 1980s, which was<br />

first used in TVs and really expanded from<br />

there. The I 2 C allows easy communication<br />

between components that reside on the<br />

same circuit board. It’s not just to be used<br />

on single boards, but to connect components<br />

which are linked through a cable. It’s able to<br />

be adapted widely because it’s simple and<br />

flexible, which are key characteristics that<br />

engineers are looking for. That’s why this bus<br />

is really attractive for a lot of applications.<br />

<strong>Jennifer</strong> <strong>Zhao</strong> (Center) with system management team.<br />

Philips Semiconductor migrated to NXP back<br />

in 2006, so we took over the portfolio and IP,<br />

which included the I2 C-buses.<br />

What trends in technology do NXP’s<br />

products support?<br />

As I mentioned earlier, we work very closely<br />

with the core chip, because we provide<br />

interface solutions. One trend we are seeing<br />

is that the SoC is going towards lower voltage<br />

applications. A few years ago, the SoC was<br />

operating at 3.3V, but later on, it went down to<br />

1.8V. Now, the lowest has gone down to 0.9V.<br />

Many peripherals are still operating at 3.3V,<br />

so there is a strong need for level translation.<br />

Our level shifter family addresses this trend in<br />

the market. We have products that translate<br />

voltages from 1.8V to 3.3V and vice versa.<br />

The other trend we see is higher speeds. The<br />

original I 2 C ran at 100Kb per second, then we<br />

developed a Fast-mode I 2 C specification,<br />

which runs at 400Kb per second. Now, we’re<br />

seeing customers adopting 1Mb per second,<br />

which we call Fast-mode Plus I 2 C-bus. We<br />

have all these different speed families to<br />

support the higher speed trends in the system.<br />

What is the company culture<br />

like at NXP?<br />

I would describe NXP as a high performance<br />

culture. We also have a lot of focus on values.<br />

We implement the highest company values,<br />

which we try to carry out with all of our<br />

employees. We stress raising the bar, engaging<br />

curiosity, taking initiative, developing the<br />

core competency, and working together.<br />

Our motto is “Customer Focused Passion to<br />

Win.” It’s been a great pleasure working with<br />

a really professional team and we all want our<br />

company to be a great company. ■<br />

INTERVIEW<br />

“At NXP, we put a lot of focus on<br />

employee engagement...With<br />

an engaged team, our chances<br />

of being a great company are<br />

greatly improved.”<br />

6 Visit: eeweb.com Visit: eeweb.com 7

PULSE<br />

With added complexity in embedded<br />

systems comes the need for more<br />

pins especially general purpose inputs<br />

and outputs that are more versatile. In<br />

late 2012, NXP Semiconductors—the<br />

inventors of the I 2 C-bus—launched a<br />

GPIO family of devices to remedy these<br />

limitations. The new family of peripheral<br />

expanders includes an innovative<br />

feature set called Agile I/O that helps<br />

integrate common system functions<br />

within the semiconductor. This new<br />

family allows the user to expand their<br />

interface without taking up much<br />

additional board space.<br />

8 Visit: eeweb.com<br />

Device Family Overview<br />

“These peripheral expanders are an expansion of our<br />

current GPIO family, which is the broadest portfolio<br />

in the market,” says <strong>Jennifer</strong> <strong>Zhao</strong>, General Manager<br />

of NXP’s System Management product line. NXP’s<br />

new line is able to expand the two wires of the I2C bus into 8-bit and 16-bit, inputs and outputs. These<br />

general-purpose I/O pins have consolidated interfacing<br />

functions that eliminate the amount of external<br />

components needed on the PCB, which saves space<br />

and simplifies the design.<br />

Addressing Industry Trends<br />

The Agile I/O expanders also have a reduced package<br />

size, which is another trend in the industry. “We have<br />

what we call HLA BGA, which is a really small 0.4 mm<br />

pitch package to address the trend of saving board<br />

space,” says <strong>Jennifer</strong> <strong>Zhao</strong>. Although the new packages<br />

are significantly smaller, there is no cost premium.<br />

Addressing the industry trend of lower voltages, the<br />

new GPIO family has very low voltage operation, from<br />

1.65 to 5.5 volts. In addition, it has a very low standby<br />

current with a maximum of 3mA. With an expansive<br />

FEATURED ARTICLE<br />

voltage range to choose from, NXP has allowed<br />

customers the option of selecting the optimal device<br />

for their applications. Some devices have two supply<br />

pins to allow separate voltage selections for the I2C-bus interface and the I/O interface.<br />

Visit: eeweb.com<br />

9

PULSE<br />

PCAL Family<br />

One of the unique features of the Agile I/O<br />

expanders is what NXP calls the PCAL family.<br />

“The L stands for latch,” <strong>Zhao</strong> told us, “which<br />

allows the input to lock in changes on input pins<br />

and to the input port register.” This allows for more<br />

flexibility for the design, which is one of the key<br />

characteristics of the Agile I/O family. Latching<br />

inputs are important in applications like alarm<br />

system monitoring, where one alarm in a series<br />

is going in and out intermittently. “If your inputs<br />

don’t latch,” says Chris Anderson of <strong>EEWeb</strong> Tech<br />

Lab, “then by the time you’re microcontroller gets<br />

around to servicing that interrupt, and you may<br />

have missed which input has changed.” This would<br />

prevent receiving any information about which<br />

alarm is going off. The Agile I/O devices also has<br />

a programmable pull-up and pull-down resisters,<br />

open drain output, programmable output drive<br />

strength and an interrupt mask—options that<br />

NXPs customers have expressed interest in.<br />

10 Visit: eeweb.com<br />

Fm+ Development Kit<br />

NXP has an I2C development kit called the OM13320,<br />

which includes a number of target devices for<br />

exploring the I2C-bus. The kit is centered on the<br />

OM13260 development board, as well as GPIO<br />

target boards, bridge board and buffer board with<br />

additional separately purchased DIP EVM board, DIP<br />

adapter boards and daughter cards. The Fm+ Dev<br />

system includes a Graphic User Interface (GUI) that<br />

allows point and click operation from your PC to<br />

control all the registers of the 16-bit Agile I/O GPIO<br />

PCAL6416A and several other devices when they<br />

are electrically connected. There is also an Expert<br />

Mode which allows the more advanced users to<br />

write code specifically for the device to operate in a<br />

specific manner.<br />

World’s lowest power capacitive<br />

sensors with auto-calibration<br />

NXP is a leader in low power capacitance touch sensors, which work based<br />

on the fact that the human body can serve as one of the capacitive plates in<br />

parallel to the second plate, connected to the input of the NXP capacitive<br />

sensor device.<br />

Thanks to a patented auto-calibration technology, the capacitive sensors<br />

can detect changes in capacitance and continually adjust to the environment.<br />

Things such as dirt, humidity, freezing temperatures, or damage to the<br />

electrode do not affect the device function.<br />

The rise of touch sensors in modern electronics has become a worldwide<br />

phenomenon, and with NXP’s low power capacitive sensors it’s never been<br />

easier to create the future.<br />

Learn more at: touch.interfacechips.com

PULSE<br />

12 Visit: eeweb.com<br />

Accurate Automatic RTC<br />

IGBT Driver Intelligent Power Device<br />

The PCA2129T is a CMOS Real Time Clock (RTC) and calendar with an integrated<br />

Temperature Compensated Crystal (Xtal) Oscillator (TCXO) and a 32.768 kHz quartz<br />

crystal optimized for very high accuracy and very low power consumption. The<br />

PCA2129 has a selectable I²C-bus or SPI-bus, a backup battery switch-over circuit, a<br />

programmable watchdog function, a timestamp function, and many other features.<br />

The device is also AEC-Q100 compliant for automotive applications and has a TCXO<br />

with integrated capacitors...Read More<br />

Renesas Electronics Corporation announced their development of an intelligent<br />

power device of isolated IGBT driver , the R2A25110KSP . This device is developed for<br />

use in electric and hybrid vehicle power inverters. Incorporating newly developed<br />

Micro-Isolator isolation technology exclusive to Renesas Electronics, the R2A25110KSP<br />

makes it possible to build more highly reliable and compact systems for today’s demanding<br />

automotive applications...Read More<br />

4A Synchronous Buck Converter<br />

UMTS Band 4 Duplexer with RX Port<br />

The Avago ACMD-4104 is a highly miniaturized duplexer designed for use in the UMTS<br />

Band 4 (1710-1755 MHz UL, 2110-2155 MHz DL) handsets and mobile data terminals.<br />

Low insertion loss in the Tx channel minimizes current drain from the power amplifier,<br />

while low Rx channel insertion loss improves receiver sensitivity. The Rx port is balanced<br />

(100 ohms) to preserve Common-Mode Rejection Ration (CMRR) and simplify<br />

the interface to baseband chipsets...Read More<br />

The TPS56428 is an adaptive on-time D-CAP2 mode synchronous buck converter.<br />

The TPS56428 enables system designers to complete the suite of various end-equipment<br />

power bus regulators with a cost effective, low component count, low standby<br />

current solution. The main control loop for the TPS56428 uses the D-CAP2 mode<br />

control that provides a fast transient response with no external compensation components.<br />

Advanced Eco-mode allows the TPS56428 to maintain high efficiency<br />

during lighter load conditions...Read More<br />

High ESD-Protected Transceiver<br />

The MAX14770E is a half-duplex, ±35kV high ESD-protected transceiver for PROFIBUS-<br />

DP and RS-485 applications. In addition, it can be used for RS-422/V.11 communications.<br />

The MAX14770E is designed to meet IEC 61158-2, TIA/EIA-422-B, TIA/EIA-485-A,<br />

V.11, and X.27 standards. The MAX14770E operates from a +5V supply and has true<br />

fail-safe circuitry that guarantees a logic-high receiver output when the receiver<br />

inputs are open or shorted...Read More<br />

Power Management ICs Reduce Carbon Footprint<br />

Fujitsu Semiconductor America introduced its new FM4 family of 32-bit RISC microcontrollers<br />

based on the ARM® Cortex-M4 processor core. The MCUs are designed<br />

for applications that require advanced, high-speed computing performance, such<br />

as general-purpose inverters, servomotors, PLCs and other industrial equipment,<br />

as well as energy-efficient, inverter-based home appliances. The new FM4 family<br />

includes 84 MCUs in its MB9B560R/460R/360R/160R series...Read More<br />

High-Voltage Sense Signal IC<br />

FEATURED PRODUCTS<br />

8-Channel Video Decoders & Audio Codecs<br />

The TW2968 is a low power NTSC/PAL video decoder chip that is designed for video<br />

surveillance applications. It consumes very low power in a typical composite input<br />

application. The available power down mode further reduces the power consumption.<br />

It uses the 1.0V for digital supply voltage and 3.3V for I/O and analog power.<br />

A single 27MHz crystal is all that needed to decode all analog video standards. The<br />

video decoder decodes the base-band analog CVBS into digital 8-bit 4:2:2 YCbCr<br />

for output...Read More<br />

The device is available in 2 (SEN012) and 3 (SEN013) channel versions according to<br />

the application’s requirements. The internal gate drive and protection circuitry provides<br />

gate drive signals to the internal 650 V MOSFETs in response to the voltage applied<br />

to the VCC pin. This simple configuration provides easy integration into existing<br />

systems by using the system VCC rail as an input to the SENZero. The SENZero family<br />

uses a low cost compact SO-8 package to reduce PCB area while the pin configuration<br />

is designed to meet pin-pin fault conditions...Read More<br />

83mm Phase Control Thyristors<br />

IXYS Corporation announced that its wholly owned UK subsidiary,<br />

IXYS UK Westcode Ltd., launched a new addition to its 83mm die<br />

phase control thyristors product group. The thyristors, rated at 2200<br />

volt, are the latest introduction to this new product group that uses<br />

an integrated die construction and improved package design for<br />

better electromechanical and thermal performances. The 2.2kV<br />

thyristor has an average current rating (Case temperature 55C)<br />

of 4340 amperes, with a junction to heat sink thermal resistance of<br />

0.008 kelvins per watt. The new thyristor is constructed using an all<br />

diffused silicon wafer slice fused to a metal header and encapsulated<br />

in a fully hermetic package. This construction enhances the<br />

performance and provides excellent transient thermal and surge<br />

current ratings...Read More<br />

Visit: eeweb.com<br />

13

PULSE<br />

Unique ID Family of EEPROMs<br />

14 Visit: eeweb.com<br />

Low Common Mode 16-Bit Quad DAC<br />

Microchip Technology Inc., a leading provider of microcontroller, mixed-signal,<br />

analog and Flash-IP solutions, today introduced a family of serial EEPROM devices<br />

that feature a unique, pre-programmed 32-bit serial number for customers requiring<br />

unique IDs in their applications. For applications needing longer than 32-bit IDs,<br />

the unique ID can be extended to 48-bit, 64-bit, 96-bit, 128-bit and other lengths by<br />

increasing the number of bytes read from memory. Because the 32-bit ID is unique<br />

within these devices, any longer bit sequence is also unique...Read More<br />

The DAC1653Q is a high-speed, high-performance 16-bit quad channel digitalto-analog<br />

converter (DAC). The device provides sample rates up to 1.5 Gsps with<br />

selectable 2x, 4x and 8x interpolation filters optimized for multi carrier and broadband<br />

wireless transmitters. The DAC1653Q integrates a JEDEC JESD204B-compliant<br />

high-speed serial input data interface running up to 10 Gbps allowing dual channel<br />

input sampling at up to 750 Msps over four differential lanes. It offers numerous<br />

advantages over traditional parallel digital interfaces...Read More<br />

200 Lumen-Per-Watt MK-R LEDs<br />

TVS Diode Array Reduces Clamping Voltages<br />

Littelfuse, Inc. has introduced the SP3051-04HTG Transient Voltage Suppression (TVS)<br />

Diode Array the latest addition to the lightning surge devices in the company’s TVS<br />

Diode Array line. It integrates low capacitance rail-to-rail diodes with an additional<br />

zener diode to protect I/O pins against ESD and lightning-induced surge events. This<br />

robust device can safely absorb 20A of current (tP=8/20μs) without performance<br />

degradation and a minimum of ±30kV ESD protection. Furthermore, the low loading<br />

capacitance makes it ideal for protecting high-speed signal pins such as 1Gb<br />

Ethernet data lines...Read More<br />

Mouser Electronics, Inc. announced it is stocking the new XLamp® MK-R LEDs from<br />

Cree, which leverage the SC³ Technology next-generation LED platform to deliver<br />

up to 200 lumens-per-watt. Cree XLamp® MK-R LEDs are built on Cree’s revolutionary<br />

SC³ Technology platform, delivering up to 200 lumens-per-watt (at 1W, 25ºC)<br />

enabling lighting manufacturers to create the next generation of high-lumen indoor<br />

and outdoor LED lighting systems...Read More<br />

Automotive Qualified Angle Sensor<br />

AK740X product family comprises the 12bit angle sensor AK7401 with serial / PWM<br />

interface as well as the high speed 12bit angle sensor AK7405 with serial / ABZ interface.<br />

The AK7401 is an automotive qualified 12bits angle sensor which detects the<br />

angular position of a magnetic field parallel to the IC surface. The contactless angle<br />

sensor can be made by the simple construction containing small magnet and this<br />

sensor. AK7401 is suitable for the rotational position sensing application, for example<br />

steering angle measurement, valve position sensing and so on...Read More<br />

Compatible LIN Transceivers<br />

The MLX80020BA is a physical layer device for<br />

a single wire data link capable of operating in<br />

applications using baud rates of 19.2kBd. The<br />

MLX80020BA is compatible to LIN2.x specifications<br />

used by European OEMs. Because of the very low<br />

power consumption of the MLX80020 in the sleep<br />

mode it’s suitable for ECU applications with hard<br />

standby current requirements. The implemented<br />

high resistive termination in sleep mode as well as<br />

the driving capability of the INH pin allows a comfortable<br />

handling of LIN short circuits to GND. In<br />

order to reduce the power consumption in case<br />

of failure modes, the integrated sleep timer takes<br />

care for switching the ECU into the most power<br />

saving sleep mode after power on or wake up<br />

events that are not followed by a mode change<br />

response of the microcontroller...Read More<br />

High Performance SiC Schottky Diodes<br />

The SCS1xxAGC series of high-performance silicon carbide (SiC) Schottky<br />

barrier diodes offers industry-leading low forward voltage and fast recovery<br />

time, leading to improved power conversion efficiency in applications.<br />

Low forward voltage is maintained over a wide operating temperature<br />

range, resulting in ultra-low switching loss. In addition, the diodes feature a<br />

breakdown voltage of 600V – impossible to achieve in silicon-based SBDs.<br />

The device has applications in PFC/power supplies, solar panel inverters,<br />

uninterruptible power supplies, air conditioners...Read More<br />

FEATURED PRODUCTS<br />

Highly Programmable Hall-Effect Switch<br />

Allegro announces a new field-programmable, unipolar Hall-effect switch<br />

designed for use in high-temperature applications. The A1128 device uses<br />

a chopper-stabilization technique to eliminate offset inherent in singleelement<br />

devices. Allegro’s new device has an advanced programming<br />

algorithm to simplify the customer’s end-of-line process. It also has a higher<br />

programming resolution for tighter magnetic switch points. It is targeted at<br />

the automotive and industrial markets. The devices are externally programmable.<br />

A wide range of programmability is available on the magnetic<br />

operate point, BOP, while the hysteresis remains fixed...Read More

Portability & Power All In One...<br />

Debug digital designs on an iPad, iPhone, iPod.<br />

Can a logic analyzer be sexy? Watch the video and weigh in...<br />

Logiscope transforms an iPhone, iPad or iPod into a 100MHz, 16 channel logic analyzer.<br />

Not only is it the most intuitive logic analyzer available, the triggering is so powerful<br />

you’ll be able to count the hair on your bug.<br />

See why our innovation keeps getting recognized.<br />

Technology You Can Trust<br />

Avago Technologies Optocouplers<br />

Safety Certifi ed Protection...<br />

Worldwide!<br />

IEC 60747-5-5 Certifi ed<br />

Optocouplers are the only isolation devices that meet or exceed the IEC 60747-5-5<br />

International Safety Standard for insulation and isolation. Stringent evaluation tests show Avago’s<br />

optocouplers deliver outstanding performance on essential safety and deliver exceptional High Voltage protection<br />

for your equipment. Alternative isolation technologies such as ADI’s magnetic or TI’s capacitive isolators do not deliver<br />

anywhere near the high voltage insulation protection or noise isolation capabilities that optocouplers deliver.<br />

For more details on this subject, read our white paper at: www.avagoresponsecenter.com/672

PULSE<br />

Cloud-Based<br />

Regression Testing<br />

for Chip Designs<br />

18 Visit: eeweb.com<br />

HarnHua Ng<br />

Founder, Plunify<br />

TECH ARTICLE<br />

Background<br />

Many compilation cycles are needed throughout the course of developing an<br />

FPGA design. As an IP vendor, it is imperative that changes to an IP core will not<br />

break the entire circuit. As a circuit designer, you would like to try different “what<br />

if” scenarios--for example, if you constrain the circuit in a certain way, or if you<br />

add a particular IP core, or if the cache size of your embedded microcontroller is<br />

changed to a particular value. Whether your design in a particular configuration<br />

will fit into different target devices might be an unknown in the first place.<br />

Visit: eeweb.com<br />

19

PULSE<br />

20 Visit: eeweb.com<br />

Regression testing and benchmarking have other equally<br />

important objectives, for example, in cases where customers<br />

or the marketing team would like to compare your IP cores<br />

against a competitor’s. Whether a design has been modified, or the<br />

logic around a specific module which is part of a bigger system has<br />

been changed, or if there is a last-minute netlist tweak, regression<br />

testing involves running a series of tests and then analyzing the<br />

results to see if all is well.<br />

CHALLENGES<br />

How long it takes to run the tests and how fast<br />

one can analyze the results are key factors<br />

in an effective regression, benchmarking or<br />

design exploration effort. Many times, FPGA<br />

designers have to forgo trying really interesting<br />

“what-if” scenarios for a variety of reasons,<br />

including the ones below:<br />

• Schedules are tight and the design changes<br />

required for the testcase in mind were too<br />

complicated or numerous to be done in a<br />

reasonable amount of time.<br />

• Designers did not want the resulting builds<br />

to consume too many server resources and<br />

slow down colleagues’ builds.<br />

• It was too tedious to send a large number of<br />

builds out to the local compute server farm<br />

to be scheduled and executed.<br />

SOLUTION<br />

In a cloud-computing environment, running<br />

and analyzing builds at scale becomes much<br />

easier. Making use of a cloud-based FPGA<br />

design platform, this case study shows how<br />

regression testing can be done for an FPGAbased<br />

embedded system that uses the LEON3<br />

processor IP core.<br />

In this example, the impact on utilization<br />

and timing performance of different RAM<br />

configurations for the LEON3 processor is<br />

evaluated by varying the data width and<br />

depth of the processor’s external memory<br />

modules.<br />

REGRESSION TEST DETAILS<br />

• Target device: Altera Stratix III device with<br />

142K Logic Elements<br />

• FPGA tool version: Quartus II 12.0<br />

• RAM module configurations:<br />

• Number of words, W: 16, 32, 64, 128, 256,<br />

512, 1024<br />

• Word widths (bits), D: 64, 128, 256, 512, 1024,<br />

2048, 4095, 8192<br />

Total number of configurations: 56<br />

• Build server specification: 2 virtual CPU cores,<br />

17GB RAM, high IO speed<br />

Total number of servers used: 56<br />

Each configuration is made into an individual<br />

Quartus II project and stored in a folder named<br />

after it, like the following:<br />

…<br />

leon3mp/W16_D64/<br />

leon3mp/W16_D128/<br />

leon3mp/W16_D256/<br />

…<br />

RUNNING BUILDS IN PARALLEL<br />

The designer issues builds using a Tcl API<br />

known as FPGAAccel that the cloud platform<br />

provides. Executing Tcl commands at the<br />

top-level “leon3mp” folder, each project’s<br />

build is submitted to compile simultaneously.<br />

Figure 1: Timing and area results<br />

TECH ARTICLE<br />

Figure 2: Time taken for synthesis and implemtation across all builds<br />

Visit: eeweb.com<br />

21

Excerpts from a typical build script:<br />

…<br />

cd W16_D64<br />

quartus_sh –t ~/fpgaaccel/tcl/quartus/<br />

cloudcompile.tcl –project leon3mp –op<br />

compile –src<br />

cd ..<br />

cd W16_D128<br />

quartus_sh –t ~/fpgaaccel/tcl/quartus/<br />

cloudcompile.tcl –project leon3mp –op<br />

compile –src<br />

cd ..<br />

…<br />

RESULTS<br />

PULSE<br />

Not all builds are expected to be completed<br />

successfully, because some of the RAM<br />

configurations are theoretically too resourceheavy<br />

to either fit into the target device or pass<br />

timing. To prevent any build from running for<br />

too long, the designer specified a maximum<br />

runtime of 24 hours. The platform has a feature<br />

where any build taking more than a specified<br />

duration would be automatically terminated.<br />

When all the builds were done, nine out of the<br />

56 configurations failed, as shown in Figure<br />

1. Upon examination, eight of the builds<br />

exceeded the maximum runtime, indicating<br />

that any RAM configuration with 1024 words<br />

could not be implemented in a reasonable<br />

amount of time. One of the builds crashed<br />

during the Fitter stage, due to insufficient<br />

memory even though 17GB was allocated<br />

to it.<br />

Failed configurations<br />

22 Visit: eeweb.com<br />

ANALYSIS<br />

After compilation, analysis and comparison of the results is another<br />

potential time-sink. Over time, most engineers will build up a collection<br />

of custom scripts to automate compilation builds and parse results.<br />

However, changes in tool versions, design report formats and server<br />

environment require extra engineering hours in maintaining those<br />

scripts. Having analysis capabilities already in the tools can save<br />

much effort and time.<br />

Figures 1 and 2 show basic timing and area statistics, comparing the<br />

successful builds to see which ones performed better. Looking at the<br />

former, the configuration with 64 memory words and a word width<br />

of 128 bits had the best maximum frequency whereas its 2048-bitwidth<br />

counterpart had the worst. From a qualitative point of view,<br />

this design’s timing seemed more ‘sensitive’ when the number of<br />

memory words was 64.<br />

Some of the RAM module configurations like W64_D2048, despite<br />

being smaller, had worse timing performance than larger ones such as<br />

W256_D2048. Within configurations with the same number of memory<br />

words, it was clear that certain bit-widths were better suited for this<br />

design in terms of the timing results.<br />

The total time needed to run all the builds was about 33 hours and<br />

average build time was 42.1 minutes. Because of the ability to spawn<br />

a virtual server for each build, all the builds were done in slightly more<br />

than an hour’s time.<br />

In general, larger RAM configurations need more compilation time,<br />

which is not surprising. Again, comparing configurations of the same<br />

number of memory words and smaller data bit-widths sometimes takes<br />

longer to synthesize and implement.<br />

SUMMARY<br />

Due to limitations on compute resources, a cloud-based design platform<br />

for FPGA designs enables design teams to carry out benchmarking,<br />

regression testing and design optimization efforts that often cannot be<br />

done locally, or does not have the priority for immediate execution.<br />

For competitive analysis or technical support reasons, product lines<br />

need to be constantly re-evaluated or re-compiled on new or legacy<br />

tool versions. These tasks require engineers and IT teams to maintain<br />

legacy tool versions and server environments. This case study shows<br />

how a cloud platform can save time and effort for design teams<br />

due to its scalability and flexibility in having on-demand compute<br />

resources available. ■<br />

» CLICK HERE<br />

to comment on the article.<br />

Power Factor Correction Controllers<br />

ISL6730A, ISL6730B, ISL6730C, ISL6730D<br />

Features<br />

The ISL6730A, ISL6730B, ISL6730C, ISL6730D are active<br />

power factor correction (PFC) controller ICs that use a boost<br />

topology. (ISL6730B, ISL6730C, ISL6730D are Coming Soon.)<br />

The controllers are suitable for AC/DC power systems, up to<br />

2kW and over the universal line input.<br />

The ISL6730A, ISL6730B, ISL6730C, ISL6730D are operated<br />

in continuous current mode. Accurate input current shaping is<br />

achieved with a current error amplifier. A patent pending<br />

breakthrough negative capacitance technology minimizes zero<br />

crossing distortion and reduces the magnetic components<br />

size. The small external components result in a low cost design<br />

without sacrificing performance.<br />

The internally clamped 12.5V gate driver delivers 1.5A peak<br />

current to the external power MOSFET. The ISL6730A,<br />

ISL6730B, ISL6730C, ISL6730D provide a highly reliable<br />

system that is fully protected. Protection features include<br />

cycle-by-cycle overcurrent, over power limit, over-temperature,<br />

input brownout, output overvoltage and undervoltage<br />

protection.<br />

The ISL6730A, ISL6730B provide excellent power efficiency<br />

and transitions into a power saving skip mode during light load<br />

conditions, thus improving efficiency automatically. The<br />

ISL6730A, ISL6730B, ISL6730C, ISL6730D can be shut down<br />

by pulling the FB pin below 0.5V or grounding the BO pin. The<br />

ISL6730C, ISL6730D have no skip mode.<br />

Two switching frequency options are provided. The ISL6730B,<br />

ISL6730D switch at 62kHz, and the ISL6730A, ISL6730C<br />

switch at 124kHz.<br />

VI<br />

VLINE<br />

+<br />

VOUT<br />

February 26, 2013<br />

FN8258.0<br />

ISEN<br />

ICOMP<br />

VIN<br />

VCC<br />

ISL6730<br />

GATE<br />

GND<br />

BO VREG<br />

FB<br />

COMP<br />

• Reduce component size requirements<br />

- Enables smaller, thinner AC/DC adapters<br />

- Choke and cap size can be reduced by 66%<br />

- Lower cost of materials<br />

• Excellent power factor over line and load regulation<br />

- Internal current compensation<br />

- CCM Mode with Patent pending IP for smaller EMI filter<br />

• Better light load efficiency<br />

- Automatic pulse skipping<br />

- Programmable or automatic shutdown<br />

• High reliable design<br />

- Cycle-by-cycle current limit<br />

- Input average power limit<br />

- OVP and OTP protection<br />

- Input brownout protection<br />

• Small 10 Ld MSOP package<br />

Applications<br />

• Desktop computer AC/DC adaptor<br />

• Laptop computer AC/DC adaptor<br />

• TV AC/DC power supply<br />

• AC/DC brick converters<br />

EFFICIENCY (%)<br />

ISL6730A, SKIP<br />

ISL6730C<br />

60<br />

0 20 40 60 80 100<br />

FIGURE 1. TYPICAL APPLICATION<br />

OUTPUT POWER (W)<br />

FIGURE 2. PFC EFFICIENCY<br />

TABLE 1. KEY DIFFERENCES IN FAMILY OF ISL6730<br />

VERSION ISL6730A ISL6730B ISL6730C ISL6730D<br />

Switching Frequency 124kHz 62kHz 124kHz 62kHz<br />

Skip Mode Yes-Fixed Yes-Fixed No No<br />

100<br />

95<br />

90<br />

85<br />

80<br />

75<br />

70<br />

65<br />

Get the Datasheet and Order Samples<br />

http://www.intersil.com<br />

Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2013<br />

All Rights Reserved. All other trademarks mentioned are the property of their respective owners.

PULSE<br />

26 24 Visit: eeweb.com<br />

eeweb.com<br />

TECH ARTICLE<br />

S u d o k u<br />

a Logical Test<br />

Rob Riemen<br />

Electrical Engineering Student<br />

Sudoku is a perfect logical test with some fun<br />

involved. For those who have never played<br />

Sudoku, it is a game starting with a grid containing<br />

36 elements. The elements are arranged in rows<br />

and columns in a 9 by 9 grid style. The board<br />

generally comes with squares filled in based on<br />

difficulty. The number of elements shown does not<br />

directly correlate with the difficulty which is an<br />

important distinction. The order of the elements<br />

makes the difference. Shown below is an example<br />

of a Sudoku board.<br />

Figure 1. Example Sudoku Board<br />

This appears to be around a medium difficulty<br />

Sudoku puzzle. The goal is to fill in this board so<br />

every cell has just one number. The numbers you<br />

choose are required to be chosen out of the range<br />

of 1 through 9. Notice how 3x3 boxes have been<br />

bolded as to distinguish a constraint. There should<br />

be no duplicates in the following fashion:<br />

• Each row should have the numbers 1–9<br />

• Each column should have the numbers 1–9<br />

• Each 3x3 box should have the numbers 1–9<br />

The order they are to be filled in should match with<br />

every other row, column and 3x3 box. With this in<br />

mind, there are a slew of possibilities the numbers<br />

can be hidden to create different difficulties for the<br />

user. With a certain amount of logical reasoning,<br />

most puzzles can be solved without guessing.<br />

This got me thinking. I am studying computer<br />

engineering and from my experience this has<br />

been a degree with elements of both electrical and<br />

software engineering. Logic is present throughout<br />

all aspects of these engineering topics. With this<br />

in mind, building a Sudoku program in the Java<br />

coding language is a great test in improving both<br />

logical and engineering skills.<br />

This is not an article about building a Sudoku<br />

program from scratch and the possibilities that<br />

are available to do so. Like with any computer<br />

program, there are multitudes of different ways to<br />

structure and code a Sudoku program.<br />

Originally, it seemed the simplest way to structure<br />

the programming for this project is to use FOR<br />

loops and IF statements. With some tinkering and<br />

multiple attempts later, a Sudoku program was<br />

materializing. This was possible because you could<br />

randomly generate a number. Then recursively<br />

through FOR loops you could eliminate from which<br />

constraints to eliminate numbers. For example, if a<br />

3 was generated, you could save the three in an<br />

array, and you could then only generate 1–2 and<br />

4–9. Doing this created a random board<br />

without duplicates.<br />

Following the generation of the board came hiding<br />

the numbers. As I have mentioned before, just<br />

hiding more numbers does not determine difficulty.<br />

Some easy Sudoku puzzles have more hidden<br />

numbers than harder difficulty puzzles. So, how do<br />

you hide numbers in a way that changes difficulty?<br />

Essentially, when answering this question you have<br />

to ask yourself, “How do you want users answering<br />

your puzzle?” It then boils down to figuring out<br />

a similar version of a Sudoku solver. The key to<br />

discovering a solution lies in understanding how<br />

the game works scientifically. In order to create<br />

challenging puzzles in Sudoku, algorithms based<br />

on Knuth’s Algorithm X to solve the Exact Cover<br />

problem need to be developed. This solution is<br />

termed as the Dancing Links technique, which is<br />

fairly useful in software engineering.<br />

Here begins the problem.<br />

Exact Cover, Knuth’s Algorithm, and the<br />

Dancing Links Technique.<br />

We have what is technically called the “Exact<br />

Cover” problem. On Wikipedia’s terms, the exact<br />

cover problem is as such; “given a collection<br />

S of subsets of a set X, an exact cover is a<br />

subcollection S* of S such that each element in X<br />

is contained in exactly one subset in S*. One says<br />

that each element in X is covered by exactly one<br />

subset in S*. An exact cover is a kind of cover”<br />

(Wikipedia 2013). In relation to Sudoku, the exact<br />

cover problem is associated with the restrictions<br />

that make Sudoku the game it is. Each element<br />

represents the individual cells. The S* references<br />

the constraints of the game Sudoku. The collection<br />

of these subset S* is what is coined as S. S is then<br />

of the set X which is the game of Sudoku itself.<br />

To simplify this concept, we take a look at the<br />

following matrix:<br />

Figure 2. Exact Cover Matrix Example<br />

The problem is to select a certain number of<br />

rows so that each column contains a 1. Knuth’s<br />

Algorithm provides a way to select rows in which<br />

all columns contain a 1. The solution to this<br />

example picks Rows A, D, and F. These satisfy<br />

the constraints. With an algorithm, the user has<br />

to develop a solution that will cycle through each<br />

column and row. In software engineering, circular<br />

doubly linked lists of the 1s in the matrix are used<br />

to check the progress of finding the correct rows.<br />

Each 1 in the matrix can check every square it is<br />

touching with a “link.” In the end the algorithm<br />

efficiently can find a solution choosing the<br />

correct rows.<br />

This technique using the circular doubly linked lists<br />

is referred to as the Dancing Links Technique. As<br />

the code moves around the matrix the linked lists<br />

cause the links to “dance” with partner links. This is<br />

done until the program finds the correct rows that<br />

solve the problem. This is exactly what would help<br />

in finding correct solutions for Sudoku.<br />

Recently, we have been referring to a matrix<br />

that contains just 1’s and 0’s. When referring to<br />

Sudoku, the Dancing Links Technique works in the<br />

same way as with 1’s and 0’s. The program has<br />

to determine which number it is analyzing and the<br />

numbers it touches. Then through Dancing Links<br />

it can “dance” around the 9x9 matrix until it has<br />

a record of what numbers exist. From this array<br />

of numbers, the program would then be able to<br />

determine which number fills an empty cell.<br />

By figuring out a way to solve a Sudoku puzzle<br />

through Dancing Links, we can choose how to<br />

hide numbers. From analyzing how the algorithm<br />

works, we see that when the program can easily<br />

eliminate numbers in rows, it can execute faster.<br />

In reality, our minds are working similarly to the<br />

algorithm. We scan each row, column, and box to<br />

see what numbers are available to us. The more<br />

significant numbers that are shown, the easier<br />

the puzzle becomes. Say, for example, there are<br />

five to seven 6’s shown on the board. From this<br />

information, we know that there are only several<br />

more possibilities available for 6’s. Hypothetically,<br />

this is compared to the two 1’s that are shown. As<br />

the program is dancing through the program and<br />

more of a certain number is shown, execution time<br />

decreases. The program will have a much easier<br />

time completing the range of 6’s than the range<br />

of 1’s.<br />

Using this information, the algorithm will be<br />

implemented to dance through and randomly<br />

choose more of similarities above to un-hide as to<br />

change difficulty. For example, several rows and<br />

columns may show more numbers, as well as more<br />

2’s, 3’s, 5’s and 8’s are un-hidden as to give an<br />

easy difficulty. Then the next board generated will<br />

increase the number of hidden numbers in this<br />

fashion. Or, in context with my statement earlier,<br />

keep the same number of squares hidden, but<br />

switch the numbers that are hidden and what order<br />

they are shown.<br />

Conclusion<br />

Obviously, Sudoku puzzles can be graded<br />

on difficulty based on the number of numbers<br />

revealed. It will be easier to solve a puzzle with<br />

plenty of numbers shown, and will be harder to<br />

complete when more are hidden. But, this is not<br />

the most efficient way to randomly create playable<br />

Sudoku boards. When coding and analyzing<br />

the exact cover problem in Sudoku, Knuth’s<br />

Algorithm helps solve the problem. The Dancing<br />

Links Technique is implementing Knuth’s Algorithm<br />

into the software which helps essentially solve an<br />

unsolved Sudoku board. Using this knowledge<br />

of how this algorithm and technique works, we<br />

can develop an efficient way to generate random<br />

Sudoku boards that actually match their<br />

true difficulty.<br />

Bibliography<br />

“Exact Cover.” Wikipedia. Wikimedia Foundation, 03 June 2013.<br />

Web. 17 Mar. 2013.<br />

Visit: eeweb.com<br />

27 25

PULSE<br />

28 Visit: eeweb.com<br />

TECH ARTICLE<br />

Gianluca Boselli<br />

Texas Instruments, Analog ESD Team<br />

A<br />

s the popularity of portable electronics, “smart<br />

devices”, and automotive electronics keeps<br />

increasing, so does the need for analog functions to be<br />

embedded in ICs. This drives the demand for specific analog<br />

technologies, which are becoming a bigger and bigger<br />

portion of the overall semiconductor market.<br />

Visit: eeweb.com<br />

29

PULSE<br />

◉<br />

ELECTROSTATIC<br />

DISCHARGE<br />

(ESD)<br />

An electrostatic<br />

charge transfer<br />

from a body to<br />

an object, which<br />

results in high<br />

currents (several<br />

amperes) during<br />

a short period of<br />

time (hundreds of<br />

nanoseconds.<br />

30 Visit: eeweb.com<br />

With some simplification, analog technologies<br />

can be binned into three main categories:<br />

1. High-Power BiCMOS: Main targets are the<br />

power devices’ RDSON and breakdown<br />

voltage. A very wide array of components’<br />

type is usually featured (Bipolar, CMOS,<br />

LDMOS, and DEMOS devices), to cover<br />

applications from Low-Voltage (LV, few<br />

Volts) up to very High-Voltage (HV, hundreds<br />

of Volts).<br />

2. High-Speed BiCMOS: Main target is the<br />

speed of the bipolar devices, to support<br />

high-speed applications, up to several<br />

hundreds of GHz.<br />

3. Analog-CMOS: Main feature is a high-density<br />

CMOS logic, along with low-parasitic, lownoise<br />

and high-quality passives. They tend<br />

to be “derivatives” of CMOS technologies.<br />

Electrostatic discharge (ESD) events can<br />

be caused by IC’s human handling/testing<br />

during manufacturing process and can lead<br />

to catastrophic damage. To guarantee ESD<br />

robustness against handling/testing, each IC<br />

is qualified against standard ESD tests, usually<br />

human-body model (HBM) and chargeddevice<br />

model (CDM).<br />

Figure 1: Typical ESD protection network implementation: a valid ESD<br />

discharge path must exist between each pad-to-pad combination.<br />

To achieve the required level of ESD robustness,<br />

dedicated on-chip circuitry (typically referred<br />

to as “ESD Protection” or “ESD Clamp”) is<br />

added to each pad to absorb ESD energy<br />

to a safe level for the protected circuitry.<br />

In a typical ESD protection implementation,<br />

each pad-to-pad combination must have<br />

a valid ESD discharge path through an ESD<br />

protection (Fig. 1). There are many challenges<br />

that analog technologies pose in terms of<br />

ESD-robust design.<br />

ESD TECHNOLOGY CHALLENGES<br />

One fundamental difference between<br />

CMOS and Analog technologies lies in the<br />

fact that the latter are often built modular.<br />

This allows the IC designer to select only a<br />

portion of available process masks, to exactly<br />

tailor design needs (not all the components<br />

available in a given process may be used<br />

for a design).<br />

From an ESD design standpoint this implies<br />

that ESD designers have to support identical<br />

ESD applications with a different mask set. This<br />

could be very challenging in that the actual<br />

behaviour of the ESD protection strongly<br />

depends on the mask set. In other words,<br />

several version of the same ESD protection<br />

may need to be built, depending on the mask<br />

set available.<br />

Another challenging aspect of analog<br />

technologies lies in the utilization model. While<br />

state-of-the-art CMOS technologies have a<br />

few years life span, analog technologies may<br />

be used for 10-15, and even 20 years. The<br />

resulting applications’ portfolio during this<br />

life span is quite a challenge for ESD design.<br />

ESD DESIGN CHALLENGES<br />

Drain-Extended MOS<br />

A drain-extended MOS (DEMOS) is a device<br />

where a same-type low-doped region is<br />

added to a high-doped drain region, or<br />

drain extension (Fig. 2). This impacts both<br />

voltage rating (i.e. breakdown increases)<br />

and drain-gate voltage drop (relevant for<br />

gate oxide reliability). On the other hand,<br />

this type of design degrades driving current<br />

characteristics, as the channel is in general not<br />

optimized for this junction. A more sophisticated version, the laterally<br />

diffused MOS (LDMOS), has better current driving characteristics.<br />

From an ESD standpoint, DEMOS transistors feature very low ESD<br />

robustness, i.e. the ability to withstand high current densities under<br />

ESD conditions. The DEMOS’ ESD weakness is a major challenge<br />

for efficient ESD Design, in that it requires special ESD protection<br />

circuitry that does not exercise DEMOS transistors during ESD events<br />

(which has an impact in terms of area). This specific issue has<br />

been addressed by multiple studies in the last 15 years, thanks also<br />

to the utilization of these components in state-of-the-art CMOS<br />

technologies.<br />

In a recent work [1] it has been shown that the blocking of the<br />

silicidation process over the high-doped/low-doped drain region<br />

(“SBLK” region in Figure 3) can significantly increase DEMOS<br />

transistors’ ESD robustness.<br />

This construction basically increases the resistance on the drain<br />

side. While its detailed impact is rather complex, it can be viewed<br />

as a way to prevent non-uniform current conduction through the<br />

ESD current distribution over the entire width of the device.<br />

3-dimensional TCAD electro-thermal simulation clearly depicts the<br />

uniform ESD current distribution along the entire width of the device<br />

with the blocking of the silicidation in the drain region (Fig. 4). This<br />

will allow some of the ESD energy to be dissipated by the DEMOS<br />

with such construction, thereby reducing constraints on the ESD<br />

protection design.<br />

High-Voltage Active FETs<br />

“Active FETs” are very popular ESD protection devices, typically for<br />

low-voltage applications. The name refers to the fact that the ESD<br />

current is shunted through MOS devices in active operation mode.<br />

This mode is enabled during ESD-conditions only, through an ESD<br />

event detector. The circuit is timed to remain in on-condition for<br />

the entire duration of the ESD events (1-2 microseconds).<br />

In CMOS technologies, where the oxide and the drain junction<br />

share the same voltage rating, the on-condition is achieved through<br />

transiently coupling the drain with the gate. A basic implementation<br />

of this concept is shown in Figure 5.<br />

For HV devices (like the aforementioned DEMOS and LDMOS), the<br />

drain rating can be much higher than the gate rating (for instance,<br />

drain could be rated 20V, while the gate only 3.3V). Therefore, a<br />

circuit like the one depicted would not work, as drain and gate<br />

would basically have the same voltage, leading to gate reliability<br />

issues (Fig. 5).<br />

A way to divide the pad voltage down to achieve an appropriate<br />

gate voltage is needed. This can be achieved with a source-follower<br />

stage (Fig. 6). This scheme allows typical HV devices to work within<br />

◉<br />

TECH ARTICLE<br />

Figure 2: Cross-section of a generic lateral<br />

DEMOS transistor.<br />

Figure 3: TOP: Typical DEMOS Transistor<br />

BOTTOM: DEMOS with blocking of the<br />

silicidation process.<br />

Figure 4: TCAD simulation of DEMOS<br />

Visit: eeweb.com<br />

31

PULSE<br />

Figure 5: (Left) Typical low-voltage transiently triggered active-FET Circuit<br />

Figure 6: (Right) Basic transiently triggered active-FET circuit utilizing<br />

source-follower buffer<br />

Figure 7: Generic HV SCR construction in a DEMOS (similar concept<br />

applies to LDMOS)<br />

the normal drain and gate operating ratings. Additionally, it also<br />

provides two significant benefits over the circuit (Fig. 5):<br />

1. The capacitance is much smaller as it drives a much smaller transistor.<br />

2. The turn-on/turn-off time constants are separated out and can be<br />

individually optimized.<br />

High-Voltage Silicon Controlled Rectifiers (SCR)<br />

Silicon-controlled rectifiers (SCR) are pnpn structures. By virtue of the<br />

mutual coupling of the vertical pnp transistor and the lateral npn<br />

transistor embedded in this pnpn structure, SCRs are the most efficient<br />

devices in terms of ESD power dissipation. Once one of the two bipolars<br />

turns on, it will turn on the other one, and so on.<br />

32 Visit: eeweb.com<br />

With reference to Figure 2, the integration of<br />

an SCR into any DeMOS (or LDMOS) is pretty<br />

straightforward, through the addition of a<br />

high-doped P-type diffusion within the drain<br />

well extension. As one can see from Figure 6, a<br />

pnpn structure with the mutually coupled npn<br />

and pnp, is formed. In addition, the presence<br />

of the gate can be used to further tune the<br />

HV-SCR ESD characteristics.<br />

The fundamental issue with type of SCRs<br />

is their ability to maintain power-scaling<br />

characteristics [2], as the pulse width of the<br />

applied ESD stress increases. More specifically,<br />

based on the maximum power dissipated by<br />

the SCR under 100ns ESD pulse, one would<br />

expect [2] a certain power dissipated under<br />

200ns and 500ns ESD pulses.<br />

However, the actual maximum power<br />

dissipated under 200ns and 500ns ESD pulses<br />

is much lower that the expectation (Fig. 8). This<br />

is a significant issue, especially in the case of<br />

ESD pulses deriving from system-level events,<br />

where the stress duration can largely exceed<br />

that of standard HBM events.<br />

High-Voltage Bipolars<br />

HV bipolar devices are not immune to poor<br />

scaling power scaling characteristics, as<br />

highlighted for HV SCRs. This is highlighted in<br />

Figure 9 where the actual maximum power<br />

dissipated does not follow power-scaling law<br />

from 100ns on.<br />

Besides power-scaling issues associated to HV<br />

bipolar devices designed as ESD protection<br />

circuits, there is another aspect related to<br />

HV bipolars that needs to be considered:<br />

parasitic bipolars formed by N-diffusions tied<br />

to adjacent bondpads.<br />

With reference to Figure 10, bondpads (PAD1<br />

and PAD2) usually have an ESD protection<br />

referenced to a common ground (GND). In<br />

the case of an ESD event from PAD1 to PAD2,<br />

the ESD current (red solid line in Figure 10)<br />

will flow from ESD Protection 1, through the<br />

common GND and ESD Protection 2, to reach<br />

PAD2. With the N-diffusions tied to PAD1 and<br />

PAD2, a parasitic npn bipolar is now formed<br />

(the common p-substrate acts as base of the<br />

bipolar), which can conduct current during<br />

ESD events and, eventually, fail.<br />

The main issue with this configuration is due<br />

to the fact that the base of the parasitic<br />

bipolar (common ground) has an elevated<br />

potential, due to ESD current flowing in ESD<br />

Protection 2. This makes the parasitic bipolar<br />

very susceptible to triggering and, hence,<br />

prone to failure.<br />

Unlike CMOS technologies, in Analog technologies<br />

it is pretty common to have multiple<br />

N-type diffusions to support many different<br />

voltage ratings and isolation techniques.<br />

Therefore, any permutation of N-type diffusions<br />

will create a parasitic in a scenario similar<br />

to that depicted in Figure 10. Considering<br />

the number of emitter, collector, base types<br />

and geometric effects, it is quite possible to<br />

generate hundreds of parasitic bipolar in a<br />

given technology. This is rather challenging<br />

for ESD design, in that the ESD protection<br />

network must be able to adequately protect<br />

the aforementioned parasitics.<br />

ESD QUALIFICATION CHALLENGES<br />

“On-Chip” System-Level Requirements<br />

To guarantee robustness to ESD events during<br />

IC’s manufacturing process, HBM and CDM<br />

tests are performed. In the last few years,<br />

a new trend to require system-level ESD<br />

protection at IC level is emerging. Normally<br />

system-level ESD protection is addressed at<br />

system-level, by placing on the board (in<br />

proximity to ESD stress sources) dedicated<br />

transient voltage suppressors (TVS) circuits.<br />

The rationale behind the trend is that TVS can<br />

be eliminated (thereby reducing cost and<br />

system design complexity), if the individual<br />

IC’s are ESD system-level robust.<br />

Without digressing into why this rationale is<br />

flawed, the impact of these requirements for<br />

IC-level ESD design is dramatic, not only in<br />

terms of ESD area but also in terms of design<br />

complexity and learning cycles needed.<br />

Custom ESD Level Requirements<br />

Typical ESD level requirements for IC-level<br />

ESD robustness are 2000V HBM and 500V<br />

CDM. Although it has been unambiguously<br />

demonstrated that 1000V HBM and 250V<br />

CDM provide very reliable ESD design<br />

in today’s manufacturing environment,<br />

certain customers may require >8KV HBM<br />

performance on selected pins to deal with<br />

unspecified system-level events. The impact<br />

of these requirements is, again, very significant<br />

in terms of area and development time.<br />

TECH ARTICLE<br />

Figure 8: Power-to-failure for HV SCR. It can be seen that power-scaling<br />

law does not hold.<br />

◉ ◉<br />

Figure 9: Similar non-scaling power characteristics, as in the case of HV<br />

SCRs, are observed with 20V CER NPN.<br />

Visit: eeweb.com<br />

33

ESD STRATEGY<br />

PULSE<br />

Figure 10: Parasitic NPN between two pad-connected N-type diffusions.<br />

The common p-substrate acts as base on the NPN.<br />

The breadth of analog technologies components portfolio and the<br />

subsequent large number of applications to protect, does not lend<br />

itself to a “single ESD strategy” that would fit all the requirements.<br />

Therefore, ESD engineers in analog technologies are looking at all<br />

ESD protection strategies, carefully weighting pros and cons to find<br />

the most suitable solution.<br />

1. Active FETs: They are very effective and popular for low-voltage<br />

applications. However, for high-voltage applications, the<br />

combination of low FETs’ drive current and large area makes them<br />

less appealing.<br />

2. Breakdown-based devices: They rely on parasitic bipolar npn or<br />

pnp. Npn-based are very popular thanks to excellent area/ESD<br />

performance trade-off. The main drawback is the difficulty to control<br />

performance over process variations.<br />

3. SCRs: These solutions are the most efficient in terms of area/ESD<br />

performance and they are pretty easy to design. However, inherent<br />

latch-up risks and difficult implementation from DRC-LVS standpoint,<br />

somewhat limit their usage.<br />

4. Self-protection: This solution is very effective in the case of large<br />

output drivers, which can be designed to withstand ESD events as<br />

well. The drawback is the need for a co-design effort between the<br />

IP and ESD.<br />

As the relevance of Analog technologies has been rapidly increasing<br />

over recent years, in this work we have reviewed the ESD challenges<br />

associated to technology, design and qualification requirements.<br />

34 Visit: eeweb.com<br />

REFERENCES<br />

[1] A. Salman et al, Proceedings of International<br />

Reliability Physics Symposium, 2012<br />

[2] D.C. Wunsch and R.R. Bell, in IEEE Trans.<br />

Nucl. Sci., 1968<br />

[3] IEC61000-4-2: Electromagnetic compatibility<br />

(EMC) – Part 4-2<br />

About the Author<br />

Gianluca Boselli joined Texas Instruments (TI) in<br />

2001 where he focused on ESD and Latch-up<br />

development for advanced CMOS technologies,<br />

with particular emphasis on process and<br />

modeling aspects. In 2007, his responsibilities<br />

extended into ESD development of TI’s Analog<br />

technologies portfolio, where he is now the<br />

manager of the Analog ESD Team. He completed<br />

his Master’s in EE at the University of<br />

Parma, Italy, in 1996. In 2001 he completed<br />

his Ph.D. at the University of Twente, The Netherlands,<br />

where he worked on high current<br />

phenomena in CMOS technologies. Dr. Boselli<br />

is currently a member of the Board of Directors<br />

of the ESD Association, where he is the Symposium<br />

Business Unit Manager, and serves on<br />

the Editorial Board of the IEEE Transactions on<br />

Device and Materials Reliability (T-DMR). He is<br />

an IEEE senior member and holds seventeen<br />

patents with several pending. ■<br />

» CLICK HERE<br />

to comment on the article.<br />

Car Trouble<br />

Asleep on the Job<br />

Tech Support Guru<br />

Join Today<br />

eeweb.com/register