The ALICE TRD Trigger System - IRTG Heidelberg

The ALICE TRD Trigger System - IRTG Heidelberg

The ALICE TRD Trigger System - IRTG Heidelberg

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

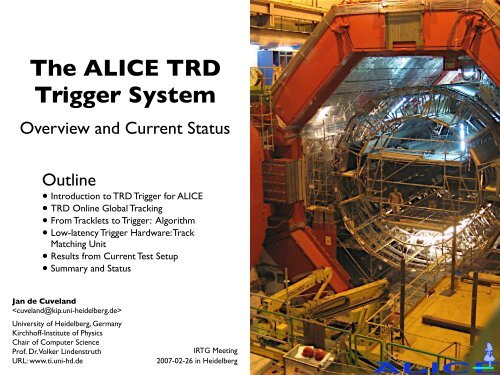

<strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong><br />

<strong>Trigger</strong> <strong>System</strong><br />

Overview and Current Status<br />

Outline<br />

• Introduction to <strong>TRD</strong> <strong>Trigger</strong> for <strong>ALICE</strong><br />

• <strong>TRD</strong> Online Global Tracking<br />

• From Tracklets to <strong>Trigger</strong>: Algorithm<br />

• Low-latency <strong>Trigger</strong> Hardware: Track<br />

Matching Unit<br />

• Results from Current Test Setup<br />

• Summary and Status<br />

Jan de Cuveland<br />

<br />

University of <strong>Heidelberg</strong>, Germany<br />

Kirchhoff-Institute of Physics<br />

Chair of Computer Science<br />

Prof. Dr. Volker Lindenstruth<br />

URL: www.ti.uni-hd.de<br />

<strong>IRTG</strong> Meeting<br />

2007-02-26 in <strong>Heidelberg</strong>

<strong>ALICE</strong> Experiment Overview<br />

lead nucleon<br />

~ speed of light<br />

<strong>TRD</strong><br />

interaction point<br />

lead nucleon<br />

~ speed of light<br />

<strong>ALICE</strong><br />

• 1150 TeV Pb-Pb<br />

interactions<br />

• 8000 collisions per<br />

second<br />

• Detectors for<br />

• <strong>Trigger</strong> (diff.<br />

levels): ITS, <strong>TRD</strong><br />

• High resolution<br />

tracking: TPC<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26 2<br />

• ...<br />

Goal is to create the Quark-Gluon<br />

Plasma, a state of matter existing<br />

during the first few microseconds<br />

after the big bang

Transition Radiation Detector – <strong>TRD</strong><br />

• 1.2 million channels<br />

• 1.4 million ADCs<br />

• 65664 MCMs<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26 3<br />

MCMs perform<br />

amplification,<br />

digitization, linear<br />

fit and read-out

<strong>TRD</strong> <strong>Trigger</strong> Tasks<br />

• Complex trigger<br />

system<br />

• Objective:<br />

• Find high pt electron<br />

pairs<br />

• Tasks:<br />

• Reconstruct tracks<br />

• Analyze tracks<br />

• <strong>Trigger</strong> decision<br />

required after 6 µs<br />

• Primary design<br />

objective: minimize<br />

latency<br />

High pt<br />

Track<br />

<strong>ALICE</strong><br />

Event Display<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26 4<br />

<strong>TRD</strong>

<strong>TRD</strong> <strong>Trigger</strong> Timing<br />

Charge Cluster to Tracklet<br />

• Local tracking units on detector perform<br />

linear fits and reject uninteresting data<br />

deflection<br />

origin<br />

time bins<br />

“Tracklet”<br />

(32-Bit word):<br />

• y position<br />

(origin)<br />

• slope<br />

(deflection)<br />

• z position<br />

(pad-row<br />

number)<br />

• charge<br />

• <strong>Trigger</strong> decision after 6 µs<br />

• Charge drift and data pre-processing uses most<br />

of the time<br />

Global Tracking<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

• Inside GTU (Global Tracking Unit)<br />

• Objective: find high momentum tracks<br />

• Search for tracklets belonging together<br />

• Combine tracklets from all six layers<br />

• Reconstruct pt, compare to threshold<br />

and generate trigger<br />

• Constraint:<br />

only approx. 1.5 µs processing time<br />

5

<strong>ALICE</strong> <strong>Trigger</strong> Hierarchy<br />

• To account for different detector latencies, there are several levels in<br />

the <strong>ALICE</strong> trigger:<br />

<strong>Trigger</strong> Pre-<strong>Trigger</strong> Level-0 Level-1 Level-2 High-Level<br />

Time after<br />

Interaction<br />

0.2 µs 1.2 µs 6.5 µs ~ 88 µs > 1 ms<br />

Average Rate<br />

(Pb-Pb)<br />

~ 5000 Hz ~ 5000 Hz ~ 400 Hz ~ 200 Hz ~ 100 Hz<br />

Description/Use<br />

<strong>TRD</strong><br />

Contribution<br />

<strong>TRD</strong> Specific<br />

Wake-Up<br />

generated<br />

for <strong>TRD</strong><br />

Strobe to<br />

Sampling<br />

Electronics<br />

<strong>TRD</strong><br />

contributes<br />

to L0 via<br />

Pre-<strong>Trigger</strong><br />

Major Rate<br />

Reduction<br />

<strong>TRD</strong><br />

contributes<br />

to L1 via<br />

GTU<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

TPC Past-<br />

Future<br />

Protection<br />

Software<br />

<strong>Trigger</strong>, Data<br />

Compression<br />

– –<br />

6

<strong>TRD</strong> <strong>Trigger</strong> Timing<br />

Collision<br />

Pre-<br />

<strong>Trigger</strong><br />

Drift Time<br />

Level-0<br />

<strong>Trigger</strong><br />

Fit Calculation Tracklet Building<br />

Tracklet Shipping<br />

Global Tracking<br />

0 1 2 3 4 5 6 7 8<br />

Time after Collision [µs]<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

Level-1<br />

<strong>Trigger</strong><br />

Raw Data Shipping...<br />

Level-1 Contribution<br />

Shipping<br />

7

<strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> Overview<br />

Other <strong>ALICE</strong> <strong>System</strong>s <strong>TRD</strong> <strong>System</strong>s<br />

CTP<br />

(Central<br />

<strong>Trigger</strong><br />

Processor)<br />

Other Detectors<br />

T0<br />

V0<br />

TOF<br />

ACORDE<br />

L1 contrib., BUSY<br />

TTC (incl. L0, L1, L2,<br />

Bunch Count)<br />

L0 contrib., BUSY<br />

GTU<br />

(Global Tracking<br />

Unit)<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

End-of-Tx<br />

Pre-<strong>Trigger</strong><br />

Control Boxes<br />

(anti-)<br />

coincidence<br />

Online<br />

Tracking<br />

Outside Magnet<br />

Inside Magnet<br />

L0, L1<br />

+ Pre-<strong>Trigger</strong><br />

Tracklet Data<br />

<strong>TRD</strong><br />

(18 Super-Modules)<br />

8<br />

@ 2 TBit/s

Track Matching Unit (TMU):<br />

From Tracklets to <strong>Trigger</strong><br />

6 Modules<br />

<strong>TRD</strong> Stack<br />

12 Links from<br />

1 Detector Stack<br />

left<br />

right<br />

left<br />

right<br />

left<br />

right<br />

left<br />

right<br />

left<br />

right<br />

left<br />

right<br />

Implemented as FPGA<br />

Design using VHDL<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26 9<br />

Tracklets<br />

Raw Data<br />

Track Re-assembly<br />

Reconstruction of the<br />

Transverse Momentum<br />

Tracks pt rec<br />

Event Buffer<br />

Comparison to Threshold<br />

TMU<br />

<strong>Trigger</strong><br />

Unit<br />

Concentrator<br />

Unit

Track Re-assembly<br />

Module Profile<br />

Projected<br />

Tracklets<br />

Track<br />

Virtual<br />

Plane<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26 10<br />

•<br />

•<br />

•<br />

•<br />

Search for tracklets<br />

belonging together<br />

(3-dimensional<br />

matching task)<br />

Projection of<br />

tracklets to virtual<br />

plane<br />

Sliding window<br />

algorithm<br />

A track is found, if ≥<br />

4 tracklets from<br />

different layers inside<br />

same multidimensional<br />

window

Reconstruction of the Transverse<br />

Momentum<br />

• Calculate linear fit of (unprojected) y positions of tracklets<br />

• Estimate transverse momentum from line parameter a<br />

• Uses look-up tables, additions and multiplications<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26 11

Simulation Results<br />

• Simulation with AliRoot data, electrons with pt > 3 GeV/c<br />

Detection Efficiency<br />

Results depend on multiplicity<br />

density dNch/dη and number of<br />

tracklets delivered by detector<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

Reconstruction Precision<br />

pt reconstruction<br />

precision: 2.1 %<br />

12

TMU Board – Buffering Design<br />

Structure<br />

12x<br />

link<br />

data<br />

1<br />

end<br />

marker<br />

=<br />

+<br />

6<br />

16<br />

Alignment<br />

control<br />

DP BRAM<br />

wa<br />

FIFO<br />

we<br />

125 MHz<br />

clock domain<br />

ra<br />

re<br />

5<br />

empty<br />

128<br />

end_marker<br />

Link<br />

scheduler<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

2<br />

link_index<br />

data_valid<br />

200 MHz<br />

clock domain<br />

...<br />

4<br />

Event<br />

end rec.<br />

128<br />

128<br />

128<br />

12<br />

block<br />

bases<br />

DP BRAM<br />

wa<br />

...<br />

ra<br />

1<br />

0<br />

18<br />

18<br />

offset<br />

RAM allocator<br />

Event drop control<br />

+<br />

+<br />

14<br />

128<br />

18<br />

data<br />

address<br />

we<br />

SRAM Controller<br />

DDL SIU<br />

interface

TMU Board – Buffering / SIU Interface<br />

link_index<br />

end marker<br />

reached<br />

data_valid<br />

12<br />

4<br />

wa<br />

buffer_full<br />

DP BRAM<br />

ra<br />

offset<br />

1<br />

0<br />

RAM allocator<br />

Event drop control<br />

buffer full<br />

logic<br />

+<br />

...<br />

ra<br />

Event read-out<br />

control<br />

Header<br />

gen.<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> DP <strong>Trigger</strong> BRAM <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

wa<br />

=<br />

18<br />

1<br />

SRAM Controller<br />

+<br />

128<br />

re<br />

full<br />

32<br />

200 MHz<br />

clock domain<br />

empty<br />

SIU<br />

Interface<br />

DDL<br />

SIU<br />

link_full<br />

60 MHz<br />

clock domain<br />

15

Multi-Event Buffering inside the GTU<br />

• Multi-Event buffering significantly reduces detector dead time:<br />

average dead time<br />

average dead time<br />

100 %<br />

80 %<br />

60 %<br />

40 %<br />

20 %<br />

0 %<br />

0 Hz 50 Hz 100 Hz 150 Hz 200 Hz 250 Hz<br />

average tape rate<br />

average tape rate<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

buffer size n = 1<br />

n = 2<br />

n = 3<br />

n = 4<br />

n = 5<br />

(Results from Monte-Carlo Simulation of <strong>Trigger</strong> Timing)<br />

16

GTU Architecture<br />

Parallel processing:<br />

90 independent "Track<br />

Matching Units" (TMUs)<br />

From Detector<br />

1080 x 2.5 GBit/s Serial<br />

Optical Links (2 per Module)<br />

• <strong>Trigger</strong> Data (max. 20<br />

Tracklets per Link)<br />

• Raw ADC Data<br />

1 (large) FPGA chip<br />

per TMU<br />

Each TMU receives<br />

data from 1 detector<br />

stack (via 12 links)<br />

TMU<br />

TMU<br />

TMU<br />

TMU<br />

TMU Board<br />

Board<br />

Board<br />

Board<br />

Board<br />

Global Tracking Unit (GTU)<br />

TMU<br />

TMU<br />

TMU<br />

TMU<br />

TMU Board<br />

Board<br />

Board<br />

Board<br />

Board<br />

...<br />

5 x 8 Bit<br />

LVDS<br />

(18 x)<br />

SMU<br />

Concentrator<br />

Board<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

SMU<br />

Concentrator<br />

Board<br />

Raw Data<br />

to DAQ<br />

18 x 4 Bit<br />

LVDS<br />

<strong>Trigger</strong><br />

Unit<br />

Board<br />

17<br />

<strong>Trigger</strong><br />

to CTP

Track Matching Unit (TMU) Board<br />

12 Fiber Optical<br />

Serial Links<br />

(2.5 GBit/s)<br />

From 1<br />

Detector<br />

Stack<br />

850 nm<br />

SFP-Transceiver<br />

DDR2 SDRAM<br />

64 MB<br />

FPGA<br />

Config<br />

PROM<br />

(6U Height, Single Width)<br />

DDR2 SRAM<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26 18<br />

4 MB<br />

Xilinx<br />

XC4VFX60<br />

FF1152<br />

Custom LVDS I/O<br />

72 Pairs<br />

JTAG<br />

CompactPCI Bus<br />

3 Parallel Links<br />

(120 MHz DDR,<br />

8 Bit LVDS)<br />

To Right TMU<br />

From Left TMU<br />

To SMU Board<br />

DDR2 SRAM:<br />

High Bandwidth (28.8<br />

GBit/s) Data Buffer<br />

Virtex-4 FPGA:<br />

59k LCs, 448 I/Os,<br />

12 Internal Multi-<br />

Gigabit Serializer/<br />

Deserializer-Units,<br />

2 PowerPC Cores

SMU Concentrator Board<br />

<strong>ALICE</strong> Timing,<br />

<strong>Trigger</strong> & Control<br />

Input (TTC)<br />

Ethernet: <strong>System</strong><br />

Configuration<br />

and Control<br />

<strong>ALICE</strong> Detector<br />

Data Link (DDL)<br />

TTC<br />

RJ45<br />

850 nm<br />

SFP-Transceiver<br />

850 nm<br />

SFP-Transceiver<br />

Detector Control<br />

<strong>System</strong> (DCS)<br />

Board<br />

DDR2 SDRAM<br />

128 MB<br />

FPGA<br />

(Xilinx<br />

XC4VFX40<br />

FF1152)<br />

Config<br />

PROM<br />

DDL - Source<br />

Interface Unit (SIU)<br />

(6U Height, Double Width)<br />

DDR2 SRAM<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

4 MB<br />

CompactPCI Custom LVDS I/O<br />

JTAG<br />

<strong>Trigger</strong> Out<br />

From TMU 0<br />

From TMU 1<br />

From TMU 2<br />

From TMU 3<br />

From TMU 4<br />

5 Parallel Links<br />

(120 MHz DDR,<br />

8 Bit LVDS)<br />

19

Combined TMU/SMU Board<br />

Front Side Back Side<br />

(6U Height, Double Width)<br />

• Alternative assembly for stand-alone operation without LVDS backplane<br />

• Used for testing with the first <strong>TRD</strong> super-module<br />

• Modifications needed for ethernet socket, SIU mounting<br />

• Not used in the final <strong>ALICE</strong> <strong>TRD</strong> setup<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

Detector Control<br />

<strong>System</strong> (DCS)<br />

Board<br />

20

Current Intermediate GTU Setup<br />

• 5 combined TMU/SMU boards<br />

Diagnostics<br />

and Debugging<br />

via Embedded<br />

PowerPC<br />

60 Fiber<br />

Optical Links<br />

5 DDL SIUs<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

FPGA/PROM<br />

Programming and<br />

Control via DCS<br />

Boards (Ethernet)<br />

JTAG Interfaces<br />

for Additional<br />

Debugging<br />

21

Latest Test Results<br />

Current Test Setup<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

• Continuous parallel read-out of full<br />

<strong>TRD</strong> super-module via 60 links<br />

• Successful transmission of detector<br />

raw data via DDL to DAQ PC<br />

• Event shaper VHDL design still has<br />

timing problems (complex design<br />

running at 200 MHz) – sometimes,<br />

wrong data is transmitted<br />

• Critical hardware components<br />

(FPGA, SFPs, MGTs, SRAM, PCI, SIU<br />

Interface, TTCrx interface on DCS<br />

board) successfully tested<br />

• LVDS bus not yet tested<br />

• Optical link diagnostic features via<br />

PowerPC supported detector<br />

integration<br />

• No TMU/SMU hardware problems<br />

encountered<br />

22

Status and Outlook<br />

Prototype Test Setup, March 2006<br />

Test Setup, October 2006<br />

• TMU/SMU Hardware<br />

• PCB version with minor changes is in<br />

production, 130 PCBs to be delivered<br />

• FPGA Design<br />

• Reconstruction and trigger algorithm<br />

implemented (in VHDL) and verified<br />

• Data-shipping design implemented, but<br />

needs further tuning to meet timing<br />

requirements<br />

• Control components are currently being<br />

implemented (TTC interfacing, backplane<br />

LVDS communication, ...)<br />

• Next steps<br />

• Further testing and optimization of VHDL<br />

design, implement remaining components<br />

• Build final setup of 90 TMUs + 18 SMUs<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

23

Thank You for Your Attention<br />

Questions?<br />

Jan de Cuveland – Uni <strong>Heidelberg</strong>, KIP – <strong>The</strong> <strong>ALICE</strong> <strong>TRD</strong> <strong>Trigger</strong> <strong>System</strong> – <strong>IRTG</strong> Meeting, <strong>Heidelberg</strong> – 2007-02-26<br />

E-Mail:<br />

cuveland@kip.uni-heidelberg.de