Vergleich von Fpga-Architekturen für partitionierte Wavelet ...

Vergleich von Fpga-Architekturen für partitionierte Wavelet ...

Vergleich von Fpga-Architekturen für partitionierte Wavelet ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

© £<br />

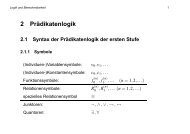

<br />

.<br />

A i+1<br />

B i+1<br />

A i<br />

B i<br />

C i<br />

CARRY LOGIC<br />

Figure 2: Conceptual Diagram of a Typical Addition (2 Bits/CLB)<br />

If only one adder bit is to be implemented per CLB, the<br />

selected carry<br />

may be forced to skip the first stage of carry<br />

logic. To do this, a configuration bit is set to one and<br />

selected to replace the output of the compar<br />

ator. If the bit is<br />

selected and set to zero,<br />

an initial v alue is f orced into the<br />

carry<br />

chain.<br />

This initial v T <br />

alue has three sources, determined by the SUMcon<br />

figuration<br />

bits. The first source is the configuration bit used<br />

to gate out the B operand.<br />

When this bit is a one, a 2-operand<br />

function is performed,<br />

and a one at the carry input pro-<br />

vides add-with-carry<br />

or subtr<br />

<br />

act-without-borrow A (borrow T is<br />

active<br />

Low). When the N-1, BN-1<br />

BYP<br />

bit is a zero, a 1-operand function is<br />

performed,<br />

and the carry chain is initialized A<br />

N-2, BN-2<br />

with a zero.<br />

The second source is F3.<br />

If F3 is not selected as the add/<br />

subtract<br />

control, it is a free input to the carr y chain. If it is<br />

used to control addition and subtraction, it A provides a zero T<br />

N-3, BN-3<br />

BYP<br />

or one such that the initial carry<br />

/borrow is un-asser ted in<br />

both cases.<br />

AN-4, BN-4 The final source is F1. When initialization is selected, this is<br />

a free input to the carry<br />

chain.<br />

The second stage of the carry<br />

logic may also be skipped, in<br />

the same way<br />

as the first stage. However, there is no initialization<br />

function in the second stage.<br />

A3, B3 G FNGEN<br />

F FNGEN<br />

<br />

B 1<br />

A 1,<br />

B 0<br />

A 0,<br />

CARRY IN (OPTIONAL)<br />

T INCY<br />

T BYP<br />

Figure 3: Carry Propagation Paths<br />

C i+2<br />

S i+1<br />

S i<br />

X1998A<br />

CLB CLB CLB CLB<br />

CARRY OUT (OPTIONAL)<br />

<br />

<br />

OVERFLOW (OPTIONAL)<br />

SN-1 CLB<br />

S <br />

N-2<br />

CLB<br />

T<br />

CLB<br />

CLB<br />

CLB<br />

CLB<br />

CLB<br />

CLB<br />

<br />

<br />

<br />

SUM<br />

SN-3<br />

AN-2,<br />

BN-2<br />

CLB<br />

SN-4<br />

CLB CLB AN-3, BN-3CLB S3 S1 S0 N-4 CLBs <br />

2<br />

X1805<br />

B N-1<br />

A N-1,<br />

<br />

A2,<br />

B2<br />

TBYP S2<br />

A1,<br />

B1<br />

T<br />

XAPP 013 July 4, 1996 (Version 2.0) OPCY<br />

TOPCY A0, B0 3<br />

B 2<br />

A 2,<br />

CARRY IN (OPTIONAL)<br />

¡ <br />

<br />

X1999A<br />

Figure 2: Alternative Adder Organization<br />

<br />

T SUM<br />

T INCY<br />

T BYP<br />

T BYP<br />

TBYP CARRY OUT <br />

(OPTIONAL)<br />

OVERFLOW <br />

(OPTIONAL)<br />

SN-1 S<br />

N-2<br />

<br />

SN-3 S2 S1 S0 TSUM N-2<br />

2 CLBs<br />

<br />

X1806