Vergleich von Fpga-Architekturen für partitionierte Wavelet ...

Vergleich von Fpga-Architekturen für partitionierte Wavelet ...

Vergleich von Fpga-Architekturen für partitionierte Wavelet ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

© £<br />

C 1 • • • C 4<br />

G 1 • • • G 4<br />

F 1 • • • F 4<br />

K<br />

(CLOCK)<br />

4<br />

WE D 1 /A 4 D 0<br />

4<br />

EC<br />

4<br />

EC<br />

LATCH<br />

ENABLE<br />

4 4<br />

LATCH<br />

ENABLE<br />

WRITE<br />

DECODER<br />

1 of 16<br />

WRITE<br />

DECODER<br />

1 of 16<br />

D IN<br />

16-LATCH<br />

ARRAY<br />

WRITE PULSE<br />

D IN<br />

16-LATCH<br />

ARRAY<br />

WRITE PULSE<br />

READ<br />

ADDRESS<br />

READ<br />

ADDRESS<br />

Figure 6: 32x1 Edge-Triggered Single-Port RAM (F and G addresses are identical)<br />

<br />

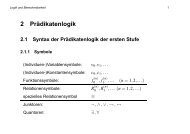

¡ ¤ § <br />

<br />

<br />

<br />

¡<br />

<br />

<br />

<br />

<br />

¤ §<br />

<br />

©<br />

<br />

<br />

<br />

<br />

<br />

¢ <br />

¤ ¡ <br />

<br />

<br />

<br />

<br />

<br />

¢<br />

¤ <br />

© <br />

<br />

© <br />

<br />

<br />

<br />

¤<br />

<br />

<br />

© <br />

<br />

<br />

<br />

<br />

§¡<br />

<br />

<br />

<br />

§ ¦¨¦¨<br />

<br />

© ¨ <br />

<br />

<br />

MUX<br />

MUX<br />

G'<br />

F'<br />

X6754<br />

¤ § <br />

<br />

<br />

<br />

<br />

¨<br />

<br />

<br />

<br />

H'