Vergleich von Fpga-Architekturen für partitionierte Wavelet ...

Vergleich von Fpga-Architekturen für partitionierte Wavelet ...

Vergleich von Fpga-Architekturen für partitionierte Wavelet ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

©£ <br />

XC4000E and XC4000X Series Field Programmable Gate Arrays <br />

CLB<br />

<br />

Double-Length Lines<br />

PSM PSM<br />

PSM<br />

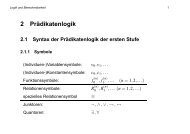

The double-length lines consist of a grid of metal segments,<br />

each twice as long as<br />

<br />

the single-length lines: they<br />

run past<br />

two<br />

CLBs bef ore enter ing a s witch matr ix. Double-length<br />

lines are grouped<br />

<br />

in pairs with the switch matrices staggered,<br />

¤ <br />

<br />

so that each line goes<br />

<br />

through a switch<br />

matr ix at<br />

every<br />

other row or column of CLBs (see Figure 29).<br />

<br />

There are four vertical and four horizontal double-length<br />

lines associated with each CLB. These lines provide faster<br />

signal routing over<br />

intermediate distances, while retaining<br />

routing flexibility. Double-length lines are connected by way<br />

of the programmable<br />

switch matrices. Routing connectivity<br />

is shown in Figure 28.<br />

Quad Lines (XC4000X only)<br />

CLB CLB<br />

CLB CLB CLB<br />

<br />

XC4000X devices<br />

also include tw elve vertical and tw elve<br />

¤ <br />

<br />

horizontal quad lines <br />

per CLB row and column. Quad lines<br />

are four<br />

times as long as the single-length lines . They are<br />

interconnected via <br />

buffered switch matrices (shown as diamonds<br />

in Figure <br />

28 on page 4-31). Quad lines run<br />

past four<br />

CLBs before<br />

<br />

enter ing a b uffered switch matr ix. The y are<br />

grouped<br />

in f ours, with the b uffered switch<br />

<br />

matr ices staggered,<br />

so that each line goes<br />

<br />

¤ <br />

through a buffered<br />

s <br />

witch<br />

matrix at every fourth CLB location in that row or column.<br />

(See Figure 30.)<br />

<br />

<br />

The buffered<br />

switch matrixes have four pins, one on<br />

<br />

each<br />

edge.<br />

All of the pins are bidirectional. Any pin can drive any<br />

or all of the other pins.<br />

Each buffered switch matrix contains one buffer and six<br />

pass transistors.<br />

It resemb les the prog rammable s witch<br />

matrix shown in Figure 27, with the addition of a prog rammable<br />

buffer. There can be up to two independent inputs<br />

and up to two<br />

independent<br />

pendent inputs can be b<br />

<br />

§ <br />

uffe<br />

¨¡¡<br />

<br />

¤ <br />

<br />

<br />

The place and route softw<br />

<br />

a<br />

requirements of the design<br />

quad line signal should <br />

be b<br />

is typically buffered, while<br />

<br />

a<br />

scenario<br />

is to alter nate<br />

<br />

bu<br />

allows<br />

both vertical and hor<br />

at alternating<br />

buffered switc<br />

Due to the buffered switch<br />

<br />

fast.<br />

They provide the f ast<br />

heavily loaded signals for lo<br />

Longlines<br />

<br />

<br />

§ <br />

<br />

¨ <br />

<br />

§ <br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

.<br />

<br />

<br />

<br />

©<br />

PSM<br />

CLB CLB CLB<br />

Doubles<br />

Singles<br />

Doubles<br />

Figure 29: Single- and Double-Length Lines, with<br />

Programmable Switch Matrices<br />

<br />

(PSMs) <br />

¥¤ ¡ § <br />

X6601<br />

<br />

<br />

CLB<br />

<br />

CLB<br />

<br />

CLB<br />

Figure 30: Quad Lines<br />

<br />

£¥¨¥©<br />

¨<br />

§ ¥©¥<br />

§ ¥ <br />

<br />

¨ <br />

££¥<br />

§¥¥§<br />

¥¨¨§¥<br />

§ ¨¡ ¨ <br />

<br />

£¥<br />

<br />

¡ ¡<br />

<br />

<br />

<br />

C<br />

<br />

C<br />

<br />

C<br />

Longlines form a grid of me<br />

run the entire length or <br />

wi<br />

intended for high fan-out, t<br />

that<br />

<br />

are distributed<br />

o <br />

ver<br />

devices,<br />

quad lines are pre<br />

<br />

the buffered<br />

switch matrice<br />

out nets<br />

<br />

Two<br />

horizontal longlines pe<br />

or open-drain<br />

drivers (TBU<br />

ment unidirectional or bidir<br />

ers,<br />

or wired-AND functions<br />

page 4-27 for more details.<br />

Each horizontal longline dr<br />

(XC4000E) or eight (XC40<br />

vate these resistors, attach<br />

line net. The software autom<br />

ate number<br />

of pull-ups . Th<br />

each end of these two<br />

horiz