Technical Product Specification for Canoe Pass - Preminary - Intel

Technical Product Specification for Canoe Pass - Preminary - Intel

Technical Product Specification for Canoe Pass - Preminary - Intel

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Intel</strong> ® Server Board S2600CP and Server System P4000CP TPS <strong>Intel</strong> ® Server System P4000CP Power System Options<br />

0V<br />

1.0 2.0 3.46V<br />

V V<br />

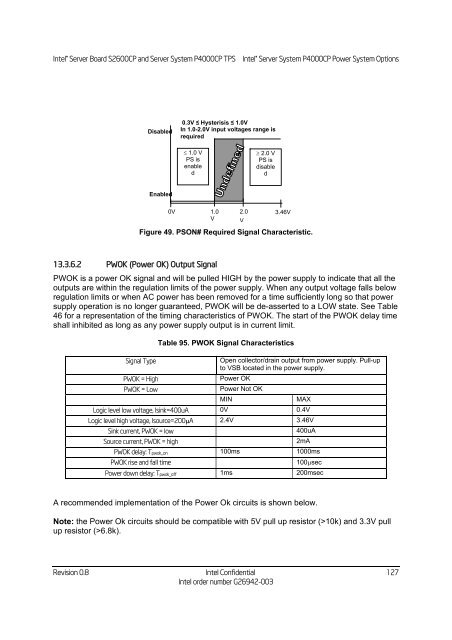

Figure 49. PSON# Required Signal Characteristic.<br />

13.3.6.2 PWOK (Power OK) Output Signal<br />

PWOK is a power OK signal and will be pulled HIGH by the power supply to indicate that all the<br />

outputs are within the regulation limits of the power supply. When any output voltage falls below<br />

regulation limits or when AC power has been removed <strong>for</strong> a time sufficiently long so that power<br />

supply operation is no longer guaranteed, PWOK will be de-asserted to a LOW state. See Table<br />

46 <strong>for</strong> a representation of the timing characteristics of PWOK. The start of the PWOK delay time<br />

shall inhibited as long as any power supply output is in current limit.<br />

Signal Type<br />

PWOK = High<br />

PWOK = Low<br />

Disabled<br />

Enabled<br />

0.3V ≤ Hysterisis ≤ 1.0V<br />

In 1.0-2.0V input voltages range is<br />

required<br />

1.0 V<br />

PS is<br />

enable<br />

d<br />

Table 95. PWOK Signal Characteristics<br />

Revision 0.8 <strong>Intel</strong> Confidential<br />

<strong>Intel</strong> order number G26942-003<br />

Open collector/drain output from power supply. Pull-up<br />

to VSB located in the power supply.<br />

Power OK<br />

Power Not OK<br />

2.0 V<br />

PS is<br />

disable<br />

d<br />

MIN MAX<br />

Logic level low voltage, Isink=400uA 0V 0.4V<br />

Logic level high voltage, Isource=200A 2.4V 3.46V<br />

Sink current, PWOK = low 400uA<br />

Source current, PWOK = high 2mA<br />

PWOK delay: Tpwok_on 100ms 1000ms<br />

PWOK rise and fall time 100sec<br />

Power down delay: Tpwok_off 1ms 200msec<br />

A recommended implementation of the Power Ok circuits is shown below.<br />

Note: the Power Ok circuits should be compatible with 5V pull up resistor (>10k) and 3.3V pull<br />

up resistor (>6.8k).<br />

127