Enhanced Polymer Passivation Layer for Wafer Level Chip Scale ...

Enhanced Polymer Passivation Layer for Wafer Level Chip Scale ...

Enhanced Polymer Passivation Layer for Wafer Level Chip Scale ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

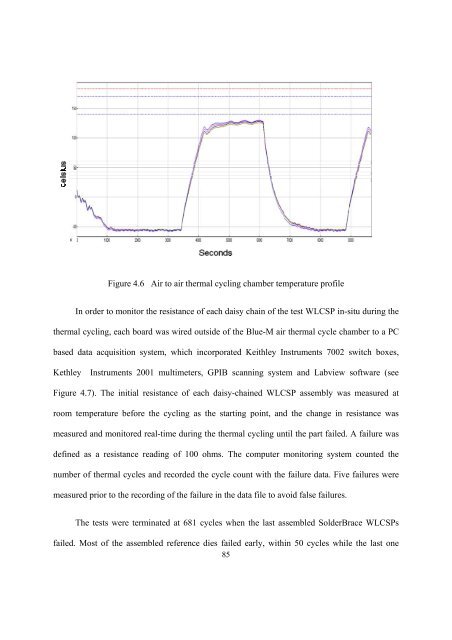

Figure 4.6 Air to air thermal cycling chamber temperature profile<br />

In order to monitor the resistance of each daisy chain of the test WLCSP in-situ during the<br />

thermal cycling, each board was wired outside of the Blue-M air thermal cycle chamber to a PC<br />

based data acquisition system, which incorporated Keithley Instruments 7002 switch boxes,<br />

Kethley Instruments 2001 multimeters, GPIB scanning system and Labview software (see<br />

Figure 4.7). The initial resistance of each daisy-chained WLCSP assembly was measured at<br />

room temperature be<strong>for</strong>e the cycling as the starting point, and the change in resistance was<br />

measured and monitored real-time during the thermal cycling until the part failed. A failure was<br />

defined as a resistance reading of 100 ohms. The computer monitoring system counted the<br />

number of thermal cycles and recorded the cycle count with the failure data. Five failures were<br />

measured prior to the recording of the failure in the data file to avoid false failures.<br />

The tests were terminated at 681 cycles when the last assembled SolderBrace WLCSPs<br />

failed. Most of the assembled reference dies failed early, within 50 cycles while the last one<br />

85