pdf file

pdf file

pdf file

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

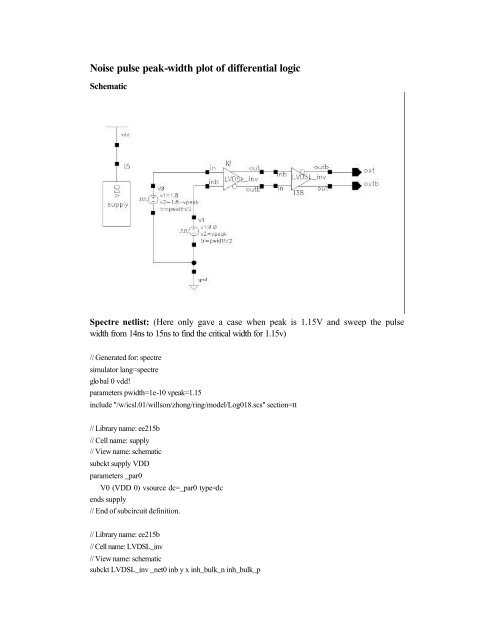

Noise pulse peak-width plot of differential logic<br />

Schematic<br />

Spectre netlist: (Here only gave a case when peak is 1.15V and sweep the pulse<br />

width from 14ns to 15ns to find the critical width for 1.15v)<br />

// Generated for: spectre<br />

simulator lang=spectre<br />

global 0 vdd!<br />

parameters pwidth=1e-10 vpeak=1.15<br />

include "/w/icsl.01/willson/zhong/ring/model/Log018.scs" section=tt<br />

// Library name: ee215b<br />

// Cell name: supply<br />

// View name: schematic<br />

subckt supply VDD<br />

parameters _par0<br />

V0 (VDD 0) vsource dc=_par0 type=dc<br />

ends supply<br />

// End of subcircuit definition.<br />

// Library name: ee215b<br />

// Cell name: LVDSL_inv<br />

// View name: schematic<br />

subckt LVDSL_inv _net0 inb y x inh_bulk_n inh_bulk_p

parameters num<br />

I1 (vdd! net22) isource dc=500u m=num type=dc<br />

M3 (y x vdd! inh_bulk_p) pch w=1.8u l=180.00n m=num<br />

M2 (x y vdd! inh_bulk_p) pch w=1.8u l=180.00n m=num<br />

M7 (net29 net22 0 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

M8 (net22 net22 0 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

M4 (y inb net29 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

M1 (x _net0 net29 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

ends LVDSL_inv<br />

// End of subcircuit definition.<br />

V1 (net012 0) vsource type=pulse val0=0.0 val1=vpeak period=20n delay=1n \<br />

rise=pwidth/2 fall=pwidth/2 width=0<br />

V0 (net011 0) vsource type=pulse val0=1.8 val1=1.8-vpeak period=20n \<br />

delay=1n rise=pwidth/2 fall=pwidth/2 width=0<br />

I5 (vdd!) supply _par0=1.8<br />

I38 (net10 net037 outb _net0 0 vdd!) LVDSL_inv num=1<br />

I0 (net011 net012 net037 net10 0 vdd!) LVDSL_inv num=1<br />

simulatorOptions options reltol=1e-3 vabstol=1e -6 iabstol=1e -12 temp=27 \<br />

tnom=27 scalem=1.0 scale=1.0 gmin=1e-12 rforce=1 maxnotes=5 maxwarns=5 \<br />

digits=5 cols=80 pivrel=1e-3 ckptclock=1800 \<br />

sens<strong>file</strong>="../psf/sens.output"<br />

tran tran stop=100n write=" spectre.ic" writefinal="spectre.fc" \<br />

annotate=status maxiters=5<br />

finalTimeOP info what=oppoint where=raw<strong>file</strong><br />

modelParameter info what=models where=raw<strong>file</strong><br />

element info what=inst where=raw<strong>file</strong><br />

outputParameter info what=output where=raw<strong>file</strong><br />

saveOptions options save=allpub<br />

Simulation Results:

Delay of differential logic with cross-coupling<br />

Schematic:<br />

Spectre Netlist: (with 5x drive for victim and L sweep from 500um to 1500um)<br />

// Generated for: spectre<br />

simulator lang=spectre

global 0 vdd!<br />

parameters L=1500<br />

include "/w/icsl.01/willson/zhong/ring/model/Log018.scs" section=tt<br />

// Library name: ee215b<br />

// Cell name: LVDSL_inv<br />

// View name: schematic<br />

subckt LVDSL_inv _net0 inb y x inh_bulk_n inh_bulk_p<br />

parameters num<br />

I1 (vdd! net22) isource dc=500u m=num type=dc<br />

M3 (y x vdd! inh_bulk_p) pch w=1.8u l=180.00n m=num<br />

M2 (x y vdd! inh_bulk_p) pch w=1.8u l=180.00n m=num<br />

M7 (net29 net22 0 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

M8 (net22 net22 0 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

M4 (y inb net29 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

M1 (x _net0 net29 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

ends LVDSL_inv<br />

// End of subcircuit definition.<br />

subckt supply VDD<br />

parameters _par0<br />

V0 (VDD 0) vsource dc=_par0 type=dc<br />

ends supply<br />

// End of subcircuit definition.<br />

// Library name: ee215b<br />

// Cell name: LVDSL_coupling_sav<br />

// View name: schematic<br />

V6 (net047 0) vsource type=pulse val0=0.0 val1=1.8 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V5 (net091 0) vsource type=pulse val0=1.8 val1=0 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V4 (net37 0) vsource type=pulse val0=1.8 val1=0 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V2 (net038 0) vsource type=pulse val0=0.0 val1=1.8 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V3 (net39 0) vsource type=pulse val0=1.8 val1=0.0 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V1 (net044 0) vsource type=pulse val0=0 val1=1.8 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

C18 (net62 net61) capacitor c=40e -18*L<br />

C17 (net58 net57) capacitor c=40e -18*L<br />

C16 (net57 0) capacitor c=20e-18*L<br />

C14 (net58 0) capacitor c=20e-18*L<br />

C13 (net58 0) capacitor c=20e-18*L<br />

C12 (net57 0) capacitor c=20e-18*L

C11 (net61 0) capacitor c=20e-18*L<br />

C10 (net62 0) capacitor c=20e-18*L<br />

C9 (net62 0) capacitor c=20e-18*L<br />

C8 (net61 net58) capacitor c=40e-18*L<br />

C7 (net61 0) capacitor c=20e-18*L<br />

C5 (net45 0) capacitor c=20e-18*L<br />

C4 (net46 0) capacitor c=20e-18*L<br />

C3 (net46 0) capacitor c=20e-18*L<br />

C2 (net45 net62) capacitor c=40e-18*L<br />

C1 (net45 0) capacitor c=20e-18*L<br />

I0 (net091 net047 net62 net61 0 vdd!) LVDSL_inv num=5<br />

I9 (net37 net038 net46 net45 0 vdd!) LVDSL_inv num=100<br />

I8 (net46 net45 out_l outb_l 0 vdd!) LVDSL_inv num=1<br />

I3 (net58 net57 out_r outb_r 0 vdd!) LVDSL_inv num=1<br />

I2 (net39 net044 net58 net57 0 vdd!) LVDSL_inv num=100<br />

I1 (net62 net61 out_v outb_v 0 vdd!) LVDSL_inv num=1<br />

I5 (vdd!) supply _par0=1.8<br />

simulatorOptions options reltol=1e-3 vabstol=1e -6 iabstol=1e -12 temp=27 \<br />

tnom=27 scalem=1.0 scale=1.0 gmin=1e-12 rforce=1 maxnotes=5 maxwarns=5 \<br />

digits=5 cols=80 pivrel=1e-3 ckptclock=1800 \<br />

sens<strong>file</strong>="../psf/sens.output"<br />

tran tran stop=100n write="spectre.ic" writefinal="spectre.fc" \<br />

annotate=status maxiters=5<br />

finalTimeOP info what=oppoint where=raw<strong>file</strong><br />

modelParameter info what=models where=raw<strong>file</strong><br />

element info what=inst where=raw<strong>file</strong><br />

outputParameter info what=output where=raw<strong>file</strong><br />

saveOptions options save=allpub<br />

Simulation Result: ( For out_v signal)

Delay of differential logic with swizzling<br />

Schematic:<br />

Spectre Netlist: (with 5x drive for victim and sweep L from 500um to 1500um)<br />

// Generated for: spectre<br />

simulator lang=spectre

global 0 vdd!<br />

parameters L=1000<br />

include "/w/icsl.01/willson/zhong/ring/model/Log018.scs" section=tt<br />

// Library name: ee215b<br />

// Cell name: LVDSL_inv<br />

// View name: schematic<br />

subckt LVDSL_inv _net0 inb y x inh_bulk_n inh_bulk_p<br />

parameters num<br />

I1 (vdd! net22) isource dc=500u m=num type=dc<br />

M3 (y x vdd! inh_bulk_p) pch w=1.8u l=180.00n m=num<br />

M2 (x y vdd! inh_bulk_p) pch w=1.8u l=180.00n m=num<br />

M7 (net29 net22 0 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

M8 (net22 net22 0 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

M4 (y inb net29 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

M1 (x _net0 net29 inh_bulk_n) nch w=1.6u l=180.00n m=num<br />

ends LVDSL_inv<br />

// End of subcircuit definition.<br />

// Library name: ee215b<br />

// Cell name: supply<br />

// View name: schematic<br />

subckt supply VDD<br />

parameters _par0<br />

V0 (VDD 0) vsource dc=_par0 type=dc<br />

ends supply<br />

// End of subcircuit definition.<br />

V6 (net047 0) vsource type=pulse val0=0.0 val1=1.8 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V5 (net091 0) vsource type=pulse val0=1.8 val1=0 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V4 (net37 0) vsource type=pulse val0=1.8 val1=0 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V2 (net038 0) vsource type=pulse val0=0.0 val1=1.8 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V3 (net39 0) vsource type=pulse val0=1.8 val1=0.0 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

V1 (net044 0) vsource type=pulse val0=0 val1=1.8 period=40n delay=1n \<br />

rise=10p fall=10p width=20n<br />

C56 (net62 net58) capacitor c=10e -18*L<br />

C55 (net62 net57) capacitor c=10e -18*L<br />

C31 (net46 net45) capacitor c=10e -18*L<br />

C44 (net58 net57) capacitor c=10e -18*L<br />

C45 (net58 net57) capacitor c=20e -18*L

C26 (net46 0) capacitor c=10e-18*L<br />

C32 (net46 net45) capacitor c=20e -18*L<br />

C34 (net61 0) capacitor c=20e-18*L<br />

C46 (net58 net57) capacitor c=10e -18*L<br />

C47 (net58 0) capacitor c=10e-18*L<br />

C35 (net62 0) capacitor c=20e-18*L<br />

C37 (net62 0) capacitor c=20e-18*L<br />

C40 (net45 net62) capacitor c=10e -18*L<br />

C38 (net62 net61) capacitor c=20e -18*L<br />

C27 (net46 0) capacitor c=10e-18*L<br />

C41 (net46 net62) capacitor c=10e -18*L<br />

C48 (net58 0) capacitor c=10e-18*L<br />

C49 (net57 0) capacitor c=10e-18*L<br />

C50 (net57 0) capacitor c=20e-18*L<br />

C25 (net45 0) capacitor c=10e-18*L<br />

C39 (net61 net62) capacitor c=20e -18*L<br />

C30 (net46 0) capacitor c=20e-18*L<br />

C36 (net61 0) capacitor c=20e-18*L<br />

C33 (net46 net45) capacitor c=10e -18*L<br />

C51 (net57 0) capacitor c=10e-18*L<br />

C54 (net61 net57) capacitor c=10e -18*L<br />

C52 (net58 0) capacitor c=20e-18*L<br />

C43 (net45 net61) capacitor c=10e -18*L<br />

C42 (net46 net61) capacitor c=10e -18*L<br />

C53 (net61 net58) capacitor c=10e -18*L<br />

I0 (net091 net047 net62 net61 0 vdd!) LVDSL_inv num=5<br />

I9 (net37 net038 net46 net45 0 vdd!) LVDSL_inv num=100<br />

I8 (net46 net45 out_l outb_l 0 vdd!) LVDSL_inv num=1<br />

I3 (net58 net57 out_r outb_r 0 vdd!) LVDSL_inv num=1<br />

I2 (net39 net044 net58 net57 0 vdd!) LVDSL_inv num=100<br />

I1 (net61 net62 out_v outb_v 0 vdd!) LVDSL_inv num=1<br />

I5 (vdd!) supply _par0=1.8<br />

simulatorOptions options reltol=1e-3 vabstol=1e -6 iabstol=1e -12 temp=27 \<br />

tnom=27 scalem=1.0 scale=1.0 gmin=1e-12 rforce=1 maxnotes=5 maxwarns=5 \<br />

digits=5 cols=80 pivrel=1e-3 ckptclock=1800 \<br />

sens<strong>file</strong>="../psf/sens.output"<br />

tran tran stop=100n write="spectre.ic" writefinal="spectre.fc" \<br />

annotate=status maxiters=5<br />

finalTimeOP info what=oppoint where=raw<strong>file</strong><br />

modelParameter info what=models where=raw<strong>file</strong><br />

element info what=inst where=raw<strong>file</strong><br />

outputParameter info what=output where=raw<strong>file</strong><br />

saveOptions options save=allpub

Simulation Result: (For out_v signal)