DB46 Xilinx Virtex-4 (XC4VSX35-10FFG668C) Daughter ... - Altium

DB46 Xilinx Virtex-4 (XC4VSX35-10FFG668C) Daughter ... - Altium

DB46 Xilinx Virtex-4 (XC4VSX35-10FFG668C) Daughter ... - Altium

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

1<br />

1<br />

2<br />

A A<br />

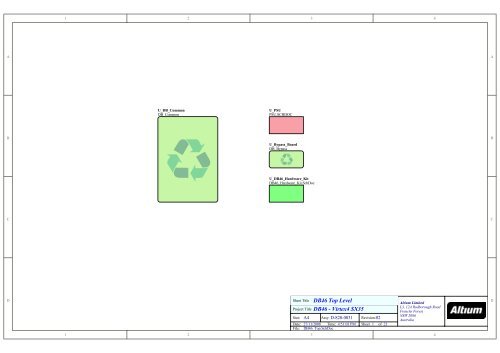

U_DB_Common<br />

DB_Common<br />

B B<br />

U_Bypass_Board<br />

DB_Bypass<br />

C C<br />

2<br />

U_PSU<br />

PSU.SCHDOC<br />

U_<strong>DB46</strong>_Hardware_Kit<br />

<strong>DB46</strong>_Hardware_Kit.SchDoc<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:03 PM Sheet 1 of 23<br />

File: <strong>DB46</strong>_Top.SchDoc<br />

3<br />

Sheet Title <strong>DB46</strong> Top Level<br />

3<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

TP0<br />

U_PSU_MAX1831_1V2_ALT<br />

PSU_MAX1831_1V2_ALT<br />

B<br />

GND<br />

GND<br />

1V2<br />

B<br />

3V3<br />

PWRNET<br />

PWRNET<br />

i<br />

i<br />

2V5<br />

5V0<br />

TP1<br />

3V3<br />

AGND GND<br />

TP2<br />

2V5<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:03 PM Sheet 2 of 23<br />

File: PSU.SCHDOC<br />

2<br />

5V0<br />

U_PSU_MAX8860_ADJ<br />

PSU_MAX8860_ADJ<br />

VIN<br />

nFAULT<br />

VSET<br />

VOUT<br />

2V5<br />

TP3<br />

PWRNET i<br />

1V2<br />

5V0<br />

R1T<br />

100K 1%<br />

C<br />

PWRNET i<br />

TP4<br />

1V2<br />

C<br />

PWRNET i<br />

1<br />

NT7<br />

2<br />

Analog power for the FPGA VCCAUX is set to<br />

a nominal 2.5V by the 100K feedback resistor.<br />

2V5<br />

2V5<br />

3<br />

Sheet Title Power Supply Top Level<br />

3<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

5V0<br />

1V2<br />

U1_PS<br />

MAX1831EEE<br />

L1_PS<br />

2u2, 15A, 4R2, SMD<br />

B<br />

R2_PS<br />

10R 1%<br />

Vfilt<br />

2<br />

4<br />

12<br />

IN<br />

IN<br />

VCC<br />

LX<br />

LX<br />

LX<br />

LX<br />

FB<br />

14<br />

16<br />

3<br />

1<br />

8<br />

LX<br />

FB<br />

R1_PS<br />

2K7 1%<br />

B<br />

C4_PS<br />

2.2uF 10V<br />

C2_PS<br />

470pF 50V<br />

COMP<br />

5<br />

6<br />

SHDN<br />

COMP<br />

PGND<br />

PGND<br />

13<br />

15<br />

R3_PS<br />

27K 1%<br />

GND<br />

R4_PS<br />

C5_PS<br />

10uF 10V<br />

C6_PS<br />

22uF 10V<br />

R5_PS TOFF<br />

100K 1%<br />

7<br />

TOFF<br />

AGND<br />

FBSEL<br />

9<br />

11<br />

2K7 1%<br />

C8_PS<br />

10uF 10V<br />

C1_PS<br />

22uF 10V<br />

C3_PS<br />

220uF 10V<br />

REF<br />

10 REF_1V2<br />

C7_PS<br />

1uF 25V<br />

GND GND AGND AGND AGND GND GND GND<br />

C C<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 3 of 23<br />

File: PSU_MAX1831_1V2_ALT.SchDoc<br />

2<br />

3<br />

Sheet Title Power Supply MAX1831 (1V2)<br />

3<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

B<br />

VIN<br />

2<br />

U11<br />

MAX8860EUA18+<br />

IN OUT<br />

1<br />

VOUT<br />

B<br />

7<br />

6<br />

nSHDN OUT<br />

CC nFAULT<br />

4<br />

8<br />

R1_LD<br />

100K 1%<br />

nFAULT<br />

Higher level has resistor (RA)<br />

between VSET and VOUT.<br />

GND<br />

C1_LD<br />

2.2uF 10V<br />

GND<br />

C2_LD<br />

0.033uF 10V<br />

3<br />

GND GND<br />

GND<br />

C C<br />

The voltage provided by the MAX8860 linear regulator is determined by the addition of a<br />

resistor between VOUT and VSET.<br />

D<br />

Note also that VIN must be a minimum of 0.18 Volts above VOUT.<br />

Sheet Title Power Supply MAX8860 (2V5) <strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 4 of 23<br />

File: PSU_MAX8860_ADJ.SchDoc<br />

2<br />

GND<br />

This additional resistor (RA) is located on the higher-level schematic.<br />

The voltage produced by the MAX8860 is calculated as follows:<br />

VOUT = 1.25 * (1 + RA / 100k)<br />

If RA = 20k, VOUT = 1.25 * (1 + 20k/100k) = 1.50 Volts<br />

If RA = 100k, VOUT = 1.25 * (1 + 100k/100k) = 2.50 Volts<br />

If RA = 164k, VOUT = 1.25 * (1 + 164k/100k) = 3.30 Volts<br />

Note that if VSET is grounded (on the higher-level schematic), VOUT=1.8 Volts<br />

SET<br />

5<br />

VSET<br />

R2_LD<br />

100K 1%<br />

3<br />

3<br />

C3_LD<br />

2.2uF 10V<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

B C1_MB C2_MB<br />

B<br />

220uF 10V 220uF 10V<br />

C C<br />

2<br />

3V3<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 5 of 23<br />

File: DB_Bypass.SchDoc<br />

GND<br />

These decoupling capacitors are intended to assist<br />

the voltage rails on the PCB - where the decoupling<br />

capacitors for the FPGA are not close.<br />

3<br />

Sheet Title Board Bypass Capacitors<br />

3<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

U_Memory_CommonBus_<strong>Daughter</strong>Board<br />

NB2_CommonMemory<br />

MEM<br />

CAN<br />

CAN<br />

B B<br />

U_CommonMemory_Termination<br />

DIP<br />

DIP<br />

NB2_CommonMemory_Termination<br />

MEM<br />

USER_LED<br />

USER_LED<br />

USERIO<br />

USERIO<br />

U_SRAM_K6R4016V1D-TC10T_256Kx16<br />

SRAM_256Kx16_TSOP44<br />

SRAM<br />

C<br />

U_SRAM_K6R4016V1D-TC10T_256Kx16<br />

CLOCKS<br />

CLOCKS<br />

C<br />

SRAM_256Kx16_TSOP44<br />

PROGRAM<br />

PROGRAM<br />

SRAM<br />

U_<strong>Daughter</strong>Board_LEDS<br />

DB_LEDS<br />

STATUS_LED<br />

STATUS_LED<br />

Top Level Schematic For <strong>Daughter</strong> Board Design<br />

Both FPGA-Only and FPGA + MCU<br />

This Device Sheet is the same for all designs.<br />

It relies on being instantiated in a project that contains a device-specific sheet named DEVICES.SchDoc .<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 6 of 23<br />

File: DB_Common.SchDoc<br />

2<br />

U_DEVICES<br />

DEVICES.SchDoc<br />

BUS<br />

SRAM1<br />

SRAM2<br />

STATUS_LED<br />

DAU_RESET_SW<br />

SLEEP_N<br />

SW<br />

BUZZER<br />

JTAG<br />

I2C<br />

KEYBOARD<br />

MOUSE<br />

RS232<br />

SPI<br />

TFT<br />

EXT_A<br />

EXT_B<br />

EXT_C<br />

ONE_WIRE_DB_PB<br />

ONE_WIRE_DBID<br />

ONE_WIRE_PIO1<br />

3<br />

Sheet Title <strong>Daughter</strong> Board Top Level<br />

3<br />

U_MotherBoardConnectors<br />

DB_MotherBoardConnectors<br />

DAU_RESET_SW<br />

SLEEP_N<br />

SW<br />

BUZZER<br />

JTAG<br />

I2C<br />

KEYBOARD<br />

MOUSE<br />

RS232<br />

SPI<br />

TFT<br />

EXT_A<br />

EXT_B<br />

EXT_C<br />

ONE_WIRE_DB_PB<br />

ONE_WIRE_DBID<br />

ONE_WIRE_PIO1<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

BUS<br />

SRAM1<br />

SRAM2<br />

C C<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 7 of 23<br />

File: DEVICES.SchDoc<br />

2<br />

U_FPGA<br />

FPGA.SCHDOC<br />

MEM_COMMON DAU_RESET_SW<br />

SRAM1<br />

SLEEP_N<br />

SRAM2<br />

SW<br />

BUZZER<br />

CAN<br />

I2C<br />

I2C<br />

B B<br />

STATUS_LED<br />

STATUS_LED<br />

KEYBOARD<br />

KEYBOARD<br />

MOUSE<br />

MOUSE<br />

ONE_WIRE_DB_PB<br />

ONE_WIRE_DBID<br />

ONE_WIRE_PIO1<br />

ONE_WIRE_DB_PB<br />

ONE_WIRE_DBID<br />

ONE_WIRE_PIO1<br />

DIP<br />

USER_LED<br />

USERIO<br />

RS232<br />

TFT<br />

EXT_A<br />

EXT_B<br />

EXT_C<br />

SPI<br />

CLOCKS<br />

PROGRAM<br />

JTAG<br />

Device Specific Section of <strong>Daughter</strong> Board Design<br />

3<br />

DAU_RESET_SW<br />

SLEEP_N<br />

SW<br />

BUZZER<br />

CAN<br />

DIP<br />

USER_LED<br />

Sheet Title FPGA, LEDs and SRAM Memory<br />

3<br />

USERIO<br />

RS232<br />

TFT<br />

EXT_A<br />

EXT_B<br />

EXT_C<br />

SPI<br />

CLOCKS<br />

PROGRAM<br />

JTAG<br />

This schematic sheet (plus any child sheets) will contain the device specific<br />

parts of any daughter board designs.<br />

This will include any FPGA or MCU devices as well as dedicated power<br />

supplies, connectors etc.<br />

4<br />

4

1<br />

1<br />

2<br />

2<br />

3<br />

3<br />

4<br />

4<br />

5<br />

5<br />

6<br />

6<br />

7<br />

7<br />

8<br />

8<br />

D D<br />

C C<br />

B B<br />

A A<br />

8<br />

02<br />

27/11/2008 4:51:04 PM<br />

FPGA.SCHDOC<br />

Project Title<br />

Size:<br />

Date:<br />

File:<br />

Revision:<br />

Sheet of<br />

Time:<br />

A2<br />

Sheet Title FPGA Connections<br />

Assy:<br />

23<br />

<strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

D-820-0031<br />

<strong>Altium</strong> Limited<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

NSW 2086<br />

Australia<br />

FPGA_TCK<br />

FPGA_TDI<br />

FPGA_TMS<br />

FPGA_TDO<br />

FPGA_PROGRAM<br />

FPGA_M0<br />

FPGA_M1<br />

FPGA_M2<br />

FPGA_CCLK<br />

FPGA_DONE<br />

3V3<br />

FPGA_PROGRAM<br />

FPGA_TDO<br />

FPGA_INIT<br />

FPGA_PROG_PWR_ON<br />

FPGA_DONE<br />

FPGA_ID3<br />

FPGA_ID0<br />

FPGA_ID1<br />

FPGA_ID2<br />

STATUS_LED<br />

FPGA_ID = 0x0 (<strong>Xilinx</strong>)<br />

TMS<br />

DONE<br />

M1<br />

CCLK<br />

M0<br />

M2<br />

TCK<br />

HSWAP_EN<br />

TDI<br />

PROG_B<br />

TDO<br />

DIN<br />

INIT<br />

U_FPGA_Power<br />

FPGA_NonIO.SchDoc<br />

U_Bypass_3V3<br />

Bypass_FPGA_3V3.SchDoc<br />

U_Bypass_2V5<br />

Bypass_FPGA_2V5.SCHDOC<br />

U_Bypass_1V2<br />

Bypass_FPGA_1V2.SCHDOC<br />

FPGA_DONE<br />

R1<br />

4K7 1%<br />

R2<br />

4K7 1%<br />

R3<br />

4K7 1%<br />

R4<br />

4K7 1%<br />

R7 100R 1%<br />

R8 100R 1%<br />

R9 100R 1%<br />

R10 100R 1%<br />

R12 100R 1%<br />

R14 100R 1%<br />

R18 100R 1%<br />

R23 100R 1%<br />

R24 100R 1%<br />

R22 100R 1%<br />

R20 100R 1%<br />

VRN_7<br />

VRP_7<br />

GND<br />

1 2<br />

NT2<br />

1 2<br />

NT3<br />

1 2<br />

NT4<br />

1 2<br />

NT5<br />

1 2<br />

NT6<br />

FPGA_CLK<br />

IO5<br />

FPGA_CLK1<br />

EXTEND_A3<br />

BUS_D29<br />

BUS_SDRAM_CKE<br />

BUS_SDRAM_NCAS<br />

BUS_SDRAM_NRAS<br />

EXTEND_B9<br />

EXTEND_B11<br />

EXTEND_A12<br />

EXTEND_A13<br />

BUS_SDRAM_NCS<br />

ONE_WIRE_DB_PB<br />

EXTEND_B1<br />

DAU_TFT_BLUE4<br />

DAU_TFT_BLUE3<br />

EXTEND_B35<br />

REF_CLK<br />

BUS_FLASH_NCS<br />

SCL<br />

DAU_TFT_IRQ<br />

DAU_TFT_POL<br />

DAU_TFT_MUX<br />

DAU_TFT_M<br />

DAU_TFT_DISP_ON<br />

DAU_TFT_BLIGHT<br />

SRAM1_D10<br />

SRAM1_D9<br />

SRAM1_D8<br />

SRAM1_A18<br />

SRAM1_A14<br />

SRAM1_A13<br />

SRAM1_D13<br />

SRAM1_D12<br />

EXTEND_B36<br />

EXTEND_B37<br />

IO28<br />

IO29<br />

SRAM2_D3<br />

SRAM1_D14<br />

EXTEND_B38<br />

EXTEND_B39<br />

DIP5<br />

LED1<br />

LED2<br />

LED4<br />

LED6<br />

LED7<br />

DIP1<br />

DIP4<br />

SRAM1_NBLE<br />

SRAM1_NOE<br />

SRAM1_A17<br />

SRAM1_A15<br />

SRAM2_NCS<br />

SRAM2_D1<br />

SRAM2_D2 EXTEND_B40<br />

EXTEND_B41<br />

LED0<br />

LED3<br />

LED5<br />

DIP0<br />

DIP2<br />

SRAM1_NBHE<br />

SRAM1_A16<br />

SRAM2_A4<br />

SRAM2_D0<br />

FPGA_INIT<br />

IO0<br />

IO2<br />

IO8<br />

SW4<br />

IO1<br />

IO3<br />

IO9<br />

IO10<br />

RS232_RTS<br />

EXTEND_B0<br />

EXTEND_C13<br />

EXTEND_C12<br />

EXTEND_A1<br />

EXTEND_A0<br />

EXTEND_B3<br />

EXTEND_B2<br />

BUS_A16<br />

BUS_A17<br />

EXTEND_A2<br />

EXTEND_B5<br />

EXTEND_B4<br />

BUS_A24<br />

BUS_A15<br />

EXTEND_A4<br />

EXTEND_B6<br />

BUS_D19<br />

BUS_D28<br />

BUS_D18<br />

BUS_D17<br />

BUS_D30<br />

BUS_A23<br />

EXTEND_A6<br />

EXTEND_A5<br />

EXTEND_B8<br />

EXTEND_B7<br />

BUS_A13<br />

BUS_A14<br />

EXTEND_A8<br />

EXTEND_A7<br />

EXTEND_B10<br />

BUS_A10<br />

BUS_NWE<br />

EXTEND_A10<br />

EXTEND_A9<br />

BUS_FLASH_NBUSY<br />

BUS_A8<br />

EXTEND_A11<br />

EXTEND_B12<br />

EXTEND_B13<br />

BUS_A11<br />

BUS_A5<br />

BUS_A4 EXTEND_B14<br />

BUS_A22<br />

EXTEND_A15<br />

EXTEND_A14<br />

EXTEND_B15<br />

EXTEND_A16<br />

EXTEND_B17<br />

EXTEND_B18<br />

EXTEND_A17<br />

EXTEND_B20<br />

EXTEND_B19<br />

DAU_TFT_GREEN2<br />

SRAM2_A9<br />

SRAM2_A10<br />

EXTEND_A18<br />

EXTEND_A19<br />

EXTEND_B22<br />

DAU_TFT_GREEN1<br />

SRAM2_A8<br />

SRAM2_A7<br />

SRAM2_A12<br />

SRAM2_A11<br />

EXTEND_A20<br />

EXTEND_B23<br />

EXTEND_B45<br />

DAU_TFT_GREEN0<br />

NEXUS_TCK<br />

SRAM2_A6<br />

NEXUS_TMS<br />

SRAM2_A13<br />

EXTEND_A22<br />

EXTEND_B29<br />

EXTEND_B25<br />

EXTEND_B24<br />

EXTEND_B46<br />

NEXUS_TDI<br />

SRAM2_A5<br />

SRAM2_NWE<br />

EXTEND_A23<br />

EXTEND_B30<br />

EXTEND_B26<br />

EXTEND_B47<br />

SRAM1_A10<br />

SRAM2_D7<br />

EXTEND_B31<br />

EXTEND_B32<br />

EXTEND_B27<br />

EXTEND_B28<br />

EXTEND_B48<br />

DAU_TFT_BLUE2<br />

SRAM1_A11<br />

SRAM2_D5<br />

SRAM2_D6<br />

EXTEND_B33<br />

EXTEND_B34<br />

EXTEND_B49<br />

DAU_TFT_RED0<br />

DAU_TFT_RED1<br />

DAU_TFT_RED2<br />

DAU_TFT_RED3<br />

SRAM1_A12<br />

SRAM1_D11<br />

SRAM2_D4<br />

BUS_D24<br />

EXTEND_C48<br />

EXTEND_C46<br />

EXTEND_C42<br />

CAN_RXD<br />

RS232_TX<br />

RS232_RX<br />

KBCLOCK<br />

MOUSECLOCK<br />

BUS_NOE<br />

BUS_D3<br />

BUS_D6<br />

BUS_D13<br />

BUS_D15<br />

SRAM2_D14<br />

EXTEND_A41<br />

EXTEND_A42<br />

EXTEND_A43<br />

IO26<br />

IO27<br />

IO31<br />

IO32<br />

IO34<br />

IO35<br />

SRAM2_NBLE<br />

SRAM2_D15<br />

SRAM2_NOE<br />

SRAM2_NBHE<br />

SRAM2_A15<br />

SRAM2_A16<br />

SRAM2_A17<br />

EXTEND_A45<br />

BUS_NBE1<br />

EXTEND_C49<br />

EXTEND_C44<br />

EXTEND_C40<br />

CAN_TXD<br />

BUS_SDRAM_FEEDBACK<br />

RS232_CTS<br />

KBDATA<br />

MOUSEDATA<br />

BUS_D1<br />

BUS_D4<br />

EXTEND_C15<br />

NEXUS_TDO<br />

EXTEND_A44<br />

BUS_D20<br />

BUS_D25<br />

BUS_D26<br />

BUS_D23<br />

BUS_D22<br />

BUS_D21<br />

BUS_D27<br />

BUS_SDRAM_CLK<br />

EXTEND_A46<br />

EXTEND_C11<br />

EXTEND_C9<br />

EXTEND_A47<br />

EXTEND_C10<br />

EXTEND_C8<br />

EXTEND_A48<br />

EXTEND_C3<br />

EXTEND_C7<br />

EXTEND_A49<br />

EXTEND_C2<br />

EXTEND_C6<br />

SRAM2_A3 EXTEND_B16<br />

EXTEND_B43<br />

EXTEND_C1<br />

EXTEND_C5<br />

SRAM2_A2<br />

SRAM2_A1<br />

EXTEND_C0<br />

EXTEND_C4<br />

SRAM2_A0<br />

EXTEND_B44<br />

SRAM1_A9<br />

EXTEND_B21<br />

SRAM1_A8<br />

SRAM1_A7<br />

EXTEND_A37<br />

SRAM1_A6<br />

SRAM2_A18<br />

SRAM2_A14<br />

EXTEND_A38<br />

SRAM1_A5<br />

SRAM2_D9<br />

SRAM2_D8<br />

EXTEND_A39<br />

IO33<br />

SRAM1_NWE<br />

SRAM2_D11<br />

SRAM2_D10<br />

EXTEND_A40<br />

SRAM1_A3<br />

SRAM1_A4<br />

SRAM1_NCS<br />

SRAM1_D0<br />

SRAM2_D13<br />

SRAM2_D12<br />

IO22<br />

IO21<br />

IO23<br />

IO12<br />

IO14<br />

IO17<br />

IO11<br />

IO13<br />

IO15<br />

IO16<br />

DIP3<br />

IO24<br />

IO25<br />

SRAM1_D1<br />

SRAM1_A2<br />

BUS_D16<br />

BUS_D31<br />

EXTEND_A36<br />

SDA<br />

IO4<br />

IO6<br />

IO7<br />

IO18<br />

IO19<br />

DIP6<br />

DAU_RESET_SW<br />

SRAM1_D15<br />

IO30<br />

IO20<br />

DIP7<br />

EXTEND_A21<br />

EXTEND_B42<br />

EXTEND_C14<br />

BUS_D8<br />

BUS_D9<br />

BUS_D10<br />

BUS_D11<br />

BUS_D14<br />

BUS_D12<br />

BUS_D7<br />

BUS_D5<br />

BUS_A20<br />

BUS_A12<br />

BUS_A9<br />

BUS_FLASH_NRESET<br />

EXTEND_C45<br />

EXTEND_C41<br />

EXTEND_C38<br />

EXTEND_C36<br />

EXTEND_C33<br />

EXTEND_C32<br />

EXTEND_C29<br />

EXTEND_C26<br />

EXTEND_C24<br />

EXTEND_C21<br />

EXTEND_C19<br />

EXTEND_C17<br />

EXTEND_C16<br />

EXTEND_C47<br />

EXTEND_C43<br />

EXTEND_C39<br />

EXTEND_C37<br />

EXTEND_C35<br />

EXTEND_C34<br />

EXTEND_C31<br />

EXTEND_C30<br />

EXTEND_C28<br />

EXTEND_C27<br />

EXTEND_C25<br />

EXTEND_C23<br />

EXTEND_C22<br />

EXTEND_C20<br />

EXTEND_C18<br />

EXTEND_A25<br />

EXTEND_A24<br />

EXTEND_A26<br />

EXTEND_A27<br />

DAU_TFT_CL1<br />

EXTEND_A28<br />

DAU_TFT_STH<br />

EXTEND_A29<br />

DAU_TFT_STV<br />

EXTEND_A30<br />

DAU_TFT_GREEN5<br />

EXTEND_A32<br />

DAU_TFT_GREEN4<br />

EXTEND_A31<br />

EXTEND_A33<br />

EXTEND_A34<br />

EXTEND_A35<br />

DAU_TFT_GREEN3<br />

DAU_TFT_CL2<br />

DAU_TFT_CL3<br />

SPI_DIN<br />

BUS_NBE2<br />

SPI_CLK<br />

UNUSED1<br />

BUS_NBE0<br />

SPI_SEL<br />

SPI_MODE<br />

BUS_NBE3<br />

BUS_A1<br />

BUS_D0<br />

BUS_A6<br />

BUS_D2<br />

BUS_SRAM_NCS<br />

SPI_DOUT<br />

BUS_A19<br />

BUS_A21<br />

BUS_A18<br />

BUS_A7<br />

BUS_A3<br />

BUS_A2<br />

SRAM1_D6<br />

SRAM1_D7<br />

SRAM1_D5<br />

SRAM1_D4<br />

SRAM1_D3<br />

SRAM1_D2<br />

SRAM1_A1<br />

SRAM1_A0<br />

UNUSED2<br />

SW0<br />

DAU_TFT_BLUE1<br />

BUZZER<br />

SW1<br />

SW2<br />

SW3<br />

DAU_TFT_RED4<br />

DAU_TFT_BLUE0<br />

UNUSED5<br />

UNUSED4<br />

UNUSED6<br />

UNUSED3<br />

FPGA_DIN<br />

SRAM1_NCS<br />

SRAM1_A[18..0]<br />

SRAM1_D[15..0]<br />

SRAM1_NBHE<br />

SRAM1_NWE<br />

SRAM1_NOE<br />

BUZZER<br />

BUZZER<br />

CAN_RXD<br />

CAN_TXD<br />

DIP[7..0]<br />

SCL<br />

SDA<br />

SPI_CLK<br />

SPI_DIN<br />

SPI_DOUT<br />

SPI_MODE<br />

SPI_SEL<br />

IO[35..0]<br />

FPGA_CLK<br />

REF_CLK<br />

FPGA_CCLK<br />

FPGA_DIN<br />

FPGA_DONE<br />

FPGA_ID[3..0]<br />

FPGA_INIT<br />

FPGA_M[2..0]<br />

FPGA_PROG_CLK<br />

FPGA_PROG_PWR_ON<br />

FPGA_PROGRAM<br />

FPGA_TCK<br />

FPGA_TDI<br />

FPGA_TDO<br />

FPGA_TMS<br />

FPGA_CLK1<br />

ONE_WIRE_DBID<br />

ONE_WIRE_DBID<br />

SW[4..0]<br />

ONE_WIRE_DB_PB<br />

ONE_WIRE_DB_PB<br />

SRAM2_NCS<br />

SRAM2_A[18..0]<br />

SRAM2_D[15..0]<br />

SRAM2_NBHE<br />

SRAM2_NWE<br />

SRAM2_NOE<br />

SRAM1_NBLE<br />

SRAM2_NBLE<br />

BUS_SDRAM_CLK<br />

BUS_SDRAM_FEEDBACK 1 2<br />

NT8<br />

ONE_WIRE_PIO1<br />

ONE_WIRE_PIO1<br />

ONE_WIRE<br />

U_1WB_DS2406_EPROM<br />

1WB_DS2406_EPROM<br />

ID<br />

PIO1<br />

PIO2<br />

ONE_WIRE<br />

A[18..0]<br />

D[15..0]<br />

NCS<br />

NWE<br />

NOE<br />

NBHE<br />

NBLE<br />

SRAM2<br />

A[18..0]<br />

D[15..0]<br />

NCS<br />

NWE<br />

NOE<br />

NBHE<br />

NBLE<br />

SRAM1<br />

BUS_A[24..1]<br />

BUS_D[31..0]<br />

BUS_NOE<br />

BUS_NWE<br />

BUS_NBE[3..0]<br />

BUS_SRAM_NCS<br />

BUS_FLASH_NCS<br />

BUS_SDRAM_NCS<br />

BUS_SDRAM_CKE<br />

BUS_SDRAM_CLK<br />

BUS_SDRAM_NCAS<br />

BUS_SDRAM_NRAS<br />

BUS_FLASH_NRESET<br />

BUS_FLASH_NBUSY<br />

BUS_A[24..1]<br />

BUS_D[31..0]<br />

BUS_NBE[3..0]<br />

BUS_NWE<br />

BUS_NOE<br />

BUS_FLASH_NCS<br />

BUS_FLASH_NRESET<br />

BUS_FLASH_NBUSY<br />

BUS_SDRAM_NCS<br />

BUS_SDRAM_CKE<br />

BUS_SDRAM_CLK<br />

BUS_SDRAM_NCAS<br />

BUS_SDRAM_NRAS<br />

BUS_SRAM_NCS<br />

HOST MEMORY RESOURCES<br />

MEM_COMMON<br />

DAUGHTER BOARD MEMORY RESOURCES<br />

REF_CLK<br />

FPGA_CLK<br />

FPGA_CLK1<br />

MODE<br />

SEL<br />

CLK<br />

DIN<br />

DOUT<br />

DIN<br />

DONE<br />

INSTALLED<br />

ID[3..0]<br />

CCLK<br />

PROGRAM<br />

M[2..0]<br />

INIT<br />

PROG_PWR_ON<br />

PROG_CLK<br />

TMS<br />

TDO<br />

TDI<br />

TCK<br />

TMS<br />

TDO<br />

TDI<br />

TCK<br />

HARD<br />

SOFT<br />

DAUGHTER BOARD I/O<br />

JTAG<br />

PROGRAM<br />

SPI BUS<br />

CLOCKS<br />

JTAG<br />

PROGRAM<br />

SPI<br />

CLOCKS<br />

NEXUS_TCK<br />

NEXUS_TDI<br />

NEXUS_TDO<br />

NEXUS_TMS<br />

DAU_RESET_SW<br />

HOST PERIPHERALS<br />

Host Reset<br />

Status LEDs<br />

L[7..0]<br />

USER_LED<br />

SW D[4..0]<br />

RED[4..0]<br />

GREEN[5..0]<br />

BLUE[4..0]<br />

M<br />

POL<br />

CL[3..1]<br />

STV<br />

STH<br />

DISP_ON<br />

BLIGHT<br />

IRQ<br />

MUX<br />

DAU_TFT_MUX<br />

DAU_TFT_RED[4..0]<br />

DAU_TFT_GREEN[5..0]<br />

DAU_TFT_BLUE[4..0]<br />

DAU_TFT_M<br />

DAU_TFT_POL<br />

DAU_TFT_CL[3..1]<br />

DAU_TFT_STV<br />

DAU_TFT_STH<br />

DAU_TFT_DISP_ON<br />

DAU_TFT_BLIGHT<br />

DAU_TFT_IRQ<br />

TFT<br />

TFT LCD DISPLAY INTERFACE<br />

DATA<br />

CLOCK<br />

KBCLOCK<br />

KBDATA<br />

MOUSECLOCK<br />

MOUSEDATA<br />

RS232_CTS<br />

RS232_RTS<br />

RS232_RX<br />

RS232_TX<br />

RS232<br />

KEYBOARD<br />

MOUSE<br />

RXD<br />

TXD<br />

RTS<br />

CTS<br />

DATA<br />

CLOCK<br />

LED[7..0]<br />

DAU_RESET_SW<br />

DIP<br />

USERIO IO[35..0]<br />

D[7..0]<br />

TXD<br />

RXD<br />

CAN<br />

SCL<br />

SDA<br />

I2C<br />

EXT_A<br />

EXT_B<br />

EXT_C<br />

EXTEND_C[49..0]<br />

EXTEND_B[49..0]<br />

EXTEND_A[49..0]<br />

D[49..0]<br />

D[49..0]<br />

D[49..0]<br />

ONE-WIRE CONNECTIONS<br />

SLEEP_N<br />

Shared Bypass Caps<br />

GND<br />

3V3<br />

C23_CM<br />

10uF 10V<br />

C24_CM<br />

10uF 10V<br />

BANK 1<br />

IO_L1P_D31_LC_1<br />

F14<br />

IO_L1N_D30_LC_1<br />

F13<br />

IO_L2P_D29_LC_1<br />

F12<br />

IO_L2N_D28_LC_1<br />

F11<br />

IO_L3P_D27_LC_1<br />

F16<br />

IO_L3N_D26_LC_1<br />

F15<br />

IO_L4P_D25_LC_1<br />

D14<br />

IO_L4N_D24_VREF_LC_1<br />

D13<br />

IO_L5P_D23_LC_1<br />

D15<br />

IO_L5N_D22_LC_1<br />

E14<br />

IO_L6P_D21_LC_1<br />

C11<br />

IO_L6N_D20_LC_1<br />

D11<br />

IO_L7P_D19_LC_1<br />

D16<br />

IO_L7N_D18_LC_1<br />

C16<br />

IO_L8P_D17_CC_LC_1<br />

E13<br />

IO_L8N_D16_CC_LC_1<br />

D12<br />

U1A<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

BANK 2<br />

IO_L1P_D15_CC_LC_2<br />

AA14<br />

IO_L1N_D14_CC_LC_2<br />

AB14<br />

IO_L2P_D13_LC_2<br />

AC12<br />

IO_L2N_D12_LC_2<br />

AC11<br />

IO_L3P_D11_LC_2<br />

AA16<br />

IO_L3N_D10_LC_2<br />

AA15<br />

IO_L4P_D9_LC_2<br />

AB13<br />

IO_L4N_D8_VREF_LC_2<br />

AA13<br />

IO_L5P_D7_LC_2<br />

AC14<br />

IO_L5N_D6_LC_2<br />

AD14<br />

IO_L6P_D5_LC_2<br />

AA12<br />

IO_L6N_D4_LC_2<br />

AA11<br />

IO_L7P_D3_LC_2<br />

AC16<br />

IO_L7N_D2_LC_2<br />

AC15<br />

IO_L8P_D1_LC_2<br />

AC13<br />

IO_L8N_D0_LC_2<br />

AD13<br />

U1B<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

BANK 3<br />

IO_L1P_GC_CC_LC_3<br />

B15<br />

IO_L1N_GC_CC_LC_3<br />

B14<br />

IO_L2P_GC_VRN_LC_3<br />

A12<br />

IO_L2N_GC_VRP_LC_3<br />

A11<br />

IO_L3P_GC_LC_3<br />

C15<br />

IO_L3N_GC_LC_3<br />

C14<br />

IO_L4P_GC_LC_3<br />

B13<br />

IO_L4N_GC_VREF_LC_3<br />

B12<br />

IO_L5P_GC_LC_3<br />

A16<br />

IO_L5N_GC_LC_3<br />

A15<br />

IO_L6P_GC_LC_3<br />

A10<br />

IO_L6N_GC_LC_3<br />

B10<br />

IO_L7P_GC_LC_3<br />

B17<br />

IO_L7N_GC_LC_3<br />

A17<br />

IO_L8P_GC_LC_3<br />

C13<br />

IO_L8N_GC_LC_3<br />

C12<br />

U1C<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

BANK 4<br />

IO_L1P_GC_LC_4<br />

AF12<br />

IO_L1N_GC_LC_4<br />

AE12<br />

IO_L2P_GC_LC_4<br />

AC10<br />

IO_L2N_GC_LC_4<br />

AB10<br />

IO_L3P_GC_LC_4<br />

AB17<br />

IO_L3N_GC_LC_4<br />

AC17<br />

IO_L4P_GC_LC_4<br />

AF11<br />

IO_L4N_GC_VREF_LC_4<br />

AF10<br />

IO_L5P_GC_LC_4<br />

AE14<br />

IO_L5N_GC_LC_4<br />

AE13<br />

IO_L6P_GC_LC_4<br />

AE10<br />

IO_L6N_GC_LC_4<br />

AD10<br />

IO_L7P_GC_VRN_LC_4<br />

AD17<br />

IO_L7N_GC_VRP_LC_4<br />

AD16<br />

IO_L8P_GC_CC_LC_4<br />

AD12<br />

IO_L8N_GC_CC_LC_4<br />

AD11<br />

U1D<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

BANK 5<br />

IO_L1P_5<br />

C17<br />

IO_L1N_5<br />

D17<br />

IO_L2P_5<br />

C20<br />

IO_L2N_5<br />

B20<br />

IO_L3P_5<br />

B18<br />

IO_L3N_5<br />

A18<br />

IO_L4P_5<br />

D20<br />

IO_L4N_VREF_5<br />

D19<br />

IO_L5P_5<br />

E17<br />

IO_L5N_5<br />

F17<br />

IO_L6P_5<br />

C21<br />

IO_L6N_5<br />

B21<br />

IO_L7P_5<br />

C19<br />

IO_L7N_5<br />

D18<br />

IO_L8P_CC_LC_5<br />

A24<br />

IO_L8N_CC_LC_5<br />

A23<br />

IO_L17P_5<br />

G19<br />

IO_L17N_5<br />

F19<br />

IO_L18P_5<br />

E23<br />

IO_L18N_5<br />

E22<br />

IO_L19P_5<br />

F20<br />

IO_L19N_5<br />

E20<br />

IO_L20P_5<br />

C26<br />

IO_L20N_VREF_5<br />

C25<br />

IO_L21P_5<br />

D23<br />

IO_L21N_5<br />

C23<br />

IO_L22P_5<br />

H20<br />

IO_L22N_5<br />

G20<br />

IO_L23P_VRN_5<br />

G22<br />

IO_L23N_VRP_5<br />

G21<br />

IO_L24P_CC_LC_5<br />

F24<br />

IO_L24N_CC_LC_5<br />

F23<br />

IO_L9P_CC_LC_5<br />

G18<br />

IO_L9N_CC_LC_5<br />

G17<br />

IO_L10P_5<br />

B24<br />

IO_L10N_5<br />

B23<br />

IO_L11P_5<br />

F18<br />

IO_L11N_5<br />

E18<br />

IO_L12P_5<br />

E21<br />

IO_L12N_VREF_5<br />

D21<br />

IO_L13P_5<br />

A20<br />

IO_L13N_5<br />

A19<br />

IO_L14P_5<br />

D22<br />

IO_L14N_5<br />

C22<br />

IO_L15P_5<br />

A22<br />

IO_L15N_5<br />

A21<br />

IO_L16P_5<br />

D24<br />

IO_L16N_5<br />

C24<br />

IO_L25P_CC_LC_5<br />

D26<br />

IO_L25N_CC_LC_5<br />

D25<br />

IO_L26P_5<br />

H22<br />

IO_L26N_5<br />

H21<br />

IO_L27P_5<br />

E25<br />

IO_L27N_5<br />

E24<br />

IO_L28P_5<br />

G24<br />

IO_L28N_VREF_5<br />

G23<br />

IO_L29P_5<br />

F26<br />

IO_L29N_5<br />

E26<br />

IO_L30P_5<br />

H24<br />

IO_L30N_5<br />

H23<br />

IO_L31P_5<br />

G26<br />

IO_L31N_5<br />

G25<br />

IO_L32P_5<br />

H26<br />

IO_L32N_5<br />

H25<br />

U1E<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

BANK 6<br />

IO_L1P_6<br />

D10<br />

IO_L1N_6<br />

C10<br />

IO_L2P_6<br />

D9<br />

IO_L2N_6<br />

C8<br />

IO_L3P_6<br />

A8<br />

IO_L3N_6<br />

A7<br />

IO_L4P_6<br />

D8<br />

IO_L4N_VREF_6<br />

D7<br />

IO_L5P_6<br />

F10<br />

IO_L5N_6<br />

E10<br />

IO_L6P_6<br />

A6<br />

IO_L6N_6<br />

A5<br />

IO_L7P_6<br />

E9<br />

IO_L7N_6<br />

F9<br />

IO_L8P_CC_LC_6<br />

B6<br />

IO_L8N_CC_LC_6<br />

C6<br />

IO_L17P_6<br />

E7<br />

IO_L17N_6<br />

D6<br />

IO_L18P_6<br />

E6<br />

IO_L18N_6<br />

E5<br />

IO_L19P_6<br />

F7<br />

IO_L19N_6<br />

G7<br />

IO_L20P_6<br />

C2<br />

IO_L20N_VREF_6<br />

C1<br />

IO_L21P_6<br />

H8<br />

IO_L21N_6<br />

H7<br />

IO_L22P_6<br />

D3<br />

IO_L22N_6<br />

E4<br />

IO_L23P_VRN_6<br />

G6<br />

IO_L23N_VRP_6<br />

G5<br />

IO_L24P_CC_LC_6<br />

E3<br />

IO_L24N_CC_LC_6<br />

E2<br />

IO_L9P_CC_LC_6<br />

G10<br />

IO_L9N_CC_LC_6<br />

G9<br />

IO_L10P_6<br />

F8<br />

IO_L10N_6<br />

G8<br />

IO_L11P_6<br />

B7<br />

IO_L11N_6<br />

C7<br />

IO_L12P_6<br />

C5<br />

IO_L12N_VREF_6<br />

D5<br />

IO_L13P_6<br />

A9<br />

IO_L13N_6<br />

B9<br />

IO_L14P_6<br />

A3<br />

IO_L14N_6<br />

B3<br />

IO_L15P_6<br />

A4<br />

IO_L15N_6<br />

B4<br />

IO_L16P_6<br />

C4<br />

IO_L16N_6<br />

D4<br />

IO_L25P_CC_LC_6<br />

D2<br />

IO_L25N_CC_LC_6<br />

D1<br />

IO_L26P_6<br />

E1<br />

IO_L26N_6<br />

F1<br />

IO_L27P_6<br />

F4<br />

IO_L27N_6<br />

F3<br />

IO_L28P_6<br />

G4<br />

IO_L28N_VREF_6<br />

G3<br />

IO_L29P_6<br />

H6<br />

IO_L29N_6<br />

H5<br />

IO_L30P_6<br />

G2<br />

IO_L30N_6<br />

G1<br />

IO_L31P_6<br />

H4<br />

IO_L31N_6<br />

H3<br />

IO_L32P_6<br />

H2<br />

IO_L32N_6<br />

H1<br />

U1F<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

BANK 7<br />

IO_L25P_CC_SM7_LC_7<br />

AD19<br />

IO_L25N_CC_SM7_LC_7<br />

AC19<br />

IO_L26P_SM6_7<br />

AA19<br />

IO_L26N_SM6_7<br />

AA20<br />

IO_L27P_SM5_7<br />

Y17<br />

IO_L27N_SM5_7<br />

AA17<br />

IO_L28P_7<br />

AB20<br />

IO_L28N_VREF_7<br />

AC20<br />

IO_L29P_SM4_7<br />

AC18<br />

IO_L29N_SM4_7<br />

AB18<br />

IO_L30P_SM3_7<br />

AF21<br />

IO_L30N_SM3_7<br />

AF22<br />

IO_L31P_SM2_7<br />

AF18<br />

IO_L31N_SM2_7<br />

AE18<br />

IO_L32P_SM1_7<br />

AE21<br />

IO_L32N_SM1_7<br />

AD21<br />

IO_L17P_7<br />

AF19<br />

IO_L17N_7<br />

AF20<br />

IO_L18P_7<br />

Y19<br />

IO_L18N_7<br />

W19<br />

IO_L19P_7<br />

AF23<br />

IO_L19N_7<br />

AE23<br />

IO_L20P_7<br />

Y20<br />

IO_L20N_VREF_7<br />

Y21<br />

IO_L21P_7<br />

AA18<br />

IO_L21N_7<br />

Y18<br />

IO_L22P_7<br />

AF24<br />

IO_L22N_7<br />

AE24<br />

IO_L23P_VRN_7<br />

AE20<br />

IO_L23N_VRP_7<br />

AD20<br />

IO_L24P_CC_LC_7<br />

AC21<br />

IO_L24N_CC_LC_7<br />

AB21<br />

IO_L1P_7<br />

V21<br />

IO_L1N_7<br />

V22<br />

IO_L2P_7<br />

W25<br />

IO_L2N_7<br />

W26<br />

IO_L3P_7<br />

W21<br />

IO_L3N_7<br />

W22<br />

IO_L4P_7<br />

W23<br />

IO_L4N_VREF_7<br />

W24<br />

IO_L5P_7<br />

W20<br />

IO_L5N_7<br />

V20<br />

IO_L6P_7<br />

Y25<br />

IO_L6N_7<br />

Y26<br />

IO_L7P_7<br />

AB24<br />

IO_L7N_7<br />

AB25<br />

IO_L8P_CC_LC_7<br />

AA24<br />

IO_L8N_CC_LC_7<br />

Y24<br />

IO_L9P_CC_LC_7<br />

AC25<br />

IO_L9N_CC_LC_7<br />

AC26<br />

IO_L10P_7<br />

AB26<br />

IO_L10N_7<br />

AA26<br />

IO_L11P_7<br />

AD25<br />

IO_L11N_7<br />

AD26<br />

IO_L12P_7<br />

Y22<br />

IO_L12N_VREF_7<br />

Y23<br />

IO_L13P_7<br />

AC22<br />

IO_L13N_7<br />

AB22<br />

IO_L14P_7<br />

AB23<br />

IO_L14N_7<br />

AA23<br />

IO_L15P_7<br />

AD22<br />

IO_L15N_7<br />

AD23<br />

IO_L16P_7<br />

AC23<br />

IO_L16N_7<br />

AC24<br />

U1G<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

BANK 8<br />

IO_L25P_CC_LC_8<br />

AF8<br />

IO_L25N_CC_LC_8<br />

AF7<br />

IO_L26P_8<br />

AA8<br />

IO_L26N_8<br />

Y8<br />

IO_L27P_8<br />

Y10<br />

IO_L27N_8<br />

AA10<br />

IO_L28P_8<br />

AC7<br />

IO_L28N_VREF_8<br />

AB7<br />

IO_L29P_8<br />

AC9<br />

IO_L29N_8<br />

AB9<br />

IO_L30P_8<br />

AE6<br />

IO_L30N_8<br />

AD6<br />

IO_L31P_8<br />

AF9<br />

IO_L31N_8<br />

AE9<br />

IO_L32P_8<br />

AD8<br />

IO_L32N_8<br />

AC8<br />

IO_L17P_8<br />

AF4<br />

IO_L17N_8<br />

AE4<br />

IO_L18P_8<br />

AD3<br />

IO_L18N_8<br />

AC3<br />

IO_L19P_8<br />

AF6<br />

IO_L19N_8<br />

AF5<br />

IO_L20P_8<br />

AA7<br />

IO_L20N_VREF_8<br />

Y7<br />

IO_L21P_8<br />

AA9<br />

IO_L21N_8<br />

Y9<br />

IO_L22P_8<br />

AD5<br />

IO_L22N_8<br />

AD4<br />

IO_L23P_VRN_8<br />

AE7<br />

IO_L23N_VRP_8<br />

AD7<br />

IO_L24P_CC_LC_8<br />

AC6<br />

IO_L24N_CC_LC_8<br />

AB6<br />

IO_L1P_8<br />

W2<br />

IO_L1N_8<br />

W1<br />

IO_L2P_8<br />

V6<br />

IO_L2N_8<br />

V5<br />

IO_L3P_8<br />

W7<br />

IO_L3N_8<br />

V7<br />

IO_L4P_8<br />

W4<br />

IO_L4N_VREF_8<br />

W3<br />

IO_L5P_8<br />

W6<br />

IO_L5N_8<br />

W5<br />

IO_L6P_8<br />

Y2<br />

IO_L6N_8<br />

Y1<br />

IO_L7P_8<br />

AA4<br />

IO_L7N_8<br />

AA3<br />

IO_L8P_CC_LC_8<br />

Y4<br />

IO_L8N_CC_LC_8<br />

Y3<br />

IO_L9P_CC_LC_8<br />

Y6<br />

IO_L9N_CC_LC_8<br />

Y5<br />

IO_L10P_8<br />

AB1<br />

IO_L10N_8<br />

AA1<br />

IO_L11P_8<br />

AC4<br />

IO_L11N_8<br />

AB4<br />

IO_L12P_8<br />

AB3<br />

IO_L12N_VREF_8<br />

AB2<br />

IO_L13P_8<br />

AC5<br />

IO_L13N_8<br />

AB5<br />

IO_L14P_8<br />

AC2<br />

IO_L14N_8<br />

AC1<br />

IO_L15P_8<br />

AF3<br />

IO_L15N_8<br />

AE3<br />

IO_L16P_8<br />

AD2<br />

IO_L16N_8<br />

AD1<br />

U1H<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

BANK 9<br />

IO_L17P_9<br />

N21<br />

IO_L17N_9<br />

N20<br />

IO_L18P_9<br />

P25<br />

IO_L18N_9<br />

P24<br />

IO_L19P_9<br />

P23<br />

IO_L19N_9<br />

P22<br />

IO_L20P_9<br />

R26<br />

IO_L20N_VREF_9<br />

R25<br />

IO_L21P_9<br />

P20<br />

IO_L21N_9<br />

P19<br />

IO_L22P_9<br />

R24<br />

IO_L22N_9<br />

R23<br />

IO_L23P_VRN_9<br />

R22<br />

IO_L23N_VRP_9<br />

R21<br />

IO_L24P_CC_LC_9<br />

T24<br />

IO_L24N_CC_LC_9<br />

T23<br />

IO_L1P_9<br />

J21<br />

IO_L1N_9<br />

J20<br />

IO_L2P_9<br />

J23<br />

IO_L2N_9<br />

J22<br />

IO_L3P_9<br />

K22<br />

IO_L3N_9<br />

K21<br />

IO_L4P_9<br />

J26<br />

IO_L4N_VREF_9<br />

J25<br />

IO_L5P_9<br />

L19<br />

IO_L5N_9<br />

K20<br />

IO_L6P_9<br />

L21<br />

IO_L6N_9<br />

L20<br />

IO_L7P_9<br />

K24<br />

IO_L7N_9<br />

K23<br />

IO_L8P_CC_LC_9<br />

K26<br />

IO_L8N_CC_LC_9<br />

K25<br />

IO_L9P_CC_LC_9<br />

M19<br />

IO_L9N_CC_LC_9<br />

N19<br />

IO_L10P_9<br />

L24<br />

IO_L10N_9<br />

L23<br />

IO_L11P_9<br />

M25<br />

IO_L11N_9<br />

M24<br />

IO_L12P_9<br />

L26<br />

IO_L12N_VREF_9<br />

M26<br />

IO_L13P_9<br />

M21<br />

IO_L13N_9<br />

M20<br />

IO_L14P_9<br />

M23<br />

IO_L14N_9<br />

M22<br />

IO_L15P_9<br />

N25<br />

IO_L15N_9<br />

N24<br />

IO_L16P_9<br />

N23<br />

IO_L16N_9<br />

N22<br />

IO_L25P_CC_LC_9<br />

R20<br />

IO_L25N_CC_LC_9<br />

R19<br />

IO_L26P_9<br />

T26<br />

IO_L26N_9<br />

U26<br />

IO_L27P_9<br />

U23<br />

IO_L27N_9<br />

V23<br />

IO_L28P_9<br />

U25<br />

IO_L28N_VREF_9<br />

U24<br />

IO_L29P_9<br />

U22<br />

IO_L29N_9<br />

U21<br />

IO_L30P_9<br />

T21<br />

IO_L30N_9<br />

T20<br />

IO_L31P_9<br />

U20<br />

IO_L31N_9<br />

T19<br />

IO_L32P_9<br />

V26<br />

IO_L32N_9<br />

V25<br />

U1I<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

BANK 10<br />

IO_L17P_10<br />

N7<br />

IO_L17N_10<br />

M7<br />

IO_L18P_10<br />

P5<br />

IO_L18N_10<br />

P4<br />

IO_L19P_10<br />

P8<br />

IO_L19N_10<br />

N8<br />

IO_L20P_10<br />

R4<br />

IO_L20N_VREF_10<br />

R3<br />

IO_L21P_10<br />

P7<br />

IO_L21N_10<br />

P6<br />

IO_L22P_10<br />

R2<br />

IO_L22N_10<br />

R1<br />

IO_L23P_VRN_10<br />

R6<br />

IO_L23N_VRP_10<br />

R5<br />

IO_L24P_CC_LC_10<br />

U1<br />

IO_L24N_CC_LC_10<br />

T1<br />

IO_L1P_10<br />

J7<br />

IO_L1N_10<br />

J6<br />

IO_L2P_10<br />

J5<br />

IO_L2N_10<br />

J4<br />

IO_L3P_10<br />

K7<br />

IO_L3N_10<br />

K6<br />

IO_L4P_10<br />

J2<br />

IO_L4N_VREF_10<br />

J1<br />

IO_L5P_10<br />

L7<br />

IO_L5N_10<br />

L6<br />

IO_L6P_10<br />

K5<br />

IO_L6N_10<br />

K4<br />

IO_L7P_10<br />

K3<br />

IO_L7N_10<br />

K2<br />

IO_L8P_CC_LC_10<br />

L4<br />

IO_L8N_CC_LC_10<br />

L3<br />

IO_L9P_CC_LC_10<br />

M8<br />

IO_L9N_CC_LC_10<br />

L8<br />

IO_L10P_10<br />

L1<br />

IO_L10N_10<br />

K1<br />

IO_L11P_10<br />

M2<br />

IO_L11N_10<br />

M1<br />

IO_L12P_10<br />

M4<br />

IO_L12N_VREF_10<br />

M3<br />

IO_L13P_10<br />

M6<br />

IO_L13N_10<br />

M5<br />

IO_L14P_10<br />

N3<br />

IO_L14N_10<br />

N2<br />

IO_L15P_10<br />

N5<br />

IO_L15N_10<br />

N4<br />

IO_L16P_10<br />

P3<br />

IO_L16N_10<br />

P2<br />

IO_L25P_CC_LC_10<br />

R8<br />

IO_L25N_CC_LC_10<br />

R7<br />

IO_L26P_10<br />

T4<br />

IO_L26N_10<br />

T3<br />

IO_L27P_10<br />

T7<br />

IO_L27N_10<br />

T6<br />

IO_L28P_10<br />

U3<br />

IO_L28N_VREF_10<br />

U2<br />

IO_L29P_10<br />

V4<br />

IO_L29N_10<br />

U4<br />

IO_L30P_10<br />

V2<br />

IO_L30N_10<br />

V1<br />

IO_L31P_10<br />

T8<br />

IO_L31N_10<br />

U7<br />

IO_L32P_10<br />

U6<br />

IO_L32N_10<br />

U5<br />

U1J<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

To permit DCI (terminated) inputs, the following must be done on each<br />

Bank:<br />

Tie the VRN pin (in each bank) through 50R to 3V3.<br />

Tie the VRP pin (in each bank) through 50R to GND.<br />

Pin Nets labeled "UNUSEDxx" are not used for any function, they are<br />

labeled for the purposes of FPGA pin swapping only.

1<br />

1<br />

2<br />

2<br />

3<br />

3<br />

4<br />

4<br />

D D<br />

C C<br />

B B<br />

A A<br />

9 23<br />

<strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

02<br />

27/11/2008 4:51:04 PM<br />

FPGA_NonIO.SchDoc<br />

Project Title<br />

Size:<br />

Date:<br />

File:<br />

Revision:<br />

Sheet of<br />

Time:<br />

A4<br />

Sheet Title FPGA Power & Programming<br />

Assy: D-820-0031<br />

<strong>Altium</strong> Limited<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

NSW 2086<br />

Australia<br />

TMS<br />

DONE<br />

M1<br />

CCLK<br />

M0<br />

M2<br />

TCK<br />

HSWAP_EN<br />

TDI<br />

PROG_B<br />

TDO<br />

3V3<br />

1V2<br />

2V5<br />

GND GND<br />

DIN<br />

INIT<br />

GND<br />

GND<br />

2V5<br />

HSWAPEN_0<br />

G16<br />

CCLK_0<br />

G14<br />

D_IN_0<br />

G12<br />

PROG_B_0<br />

H15<br />

INIT_B_0<br />

G15<br />

CS_B_0<br />

G11<br />

DONE_0<br />

H14<br />

RDWR_B_0<br />

H12<br />

VBATT_0<br />

Y16<br />

M2_0<br />

W14<br />

PWRDWN_B_0<br />

W13<br />

TMS_0<br />

Y11<br />

M0_0<br />

W15<br />

TDO_0<br />

Y13<br />

TCK_0<br />

W12<br />

M1_0<br />

Y15<br />

DOUT_BUSY_0<br />

Y14<br />

TDI_0<br />

Y12<br />

TDN_0<br />

G13<br />

TDP_0<br />

H13<br />

U1K<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

VCCAUX<br />

M9<br />

VCCAUX<br />

N9<br />

VCCAUX<br />

P9<br />

VCCAUX<br />

W10<br />

VCCAUX<br />

H11<br />

VCCAUX<br />

W11<br />

VCCAUX<br />

J12<br />

VCCAUX<br />

V15<br />

VCCAUX<br />

H16<br />

VCCAUX<br />

W16<br />

VCCAUX<br />

H17<br />

VCCAUX<br />

N18<br />

VCCAUX<br />

P18<br />

VCCAUX<br />

R18<br />

VCCINT<br />

K9<br />

VCCINT<br />

L9<br />

VCCINT<br />

T9<br />

VCCINT<br />

U9<br />

VCCINT<br />

J10<br />

VCCINT<br />

K10<br />

VCCINT<br />

L10<br />

VCCINT<br />

T10<br />

VCCINT<br />

U10<br />

VCCINT<br />

V10<br />

VCCINT<br />

J11<br />

VCCINT<br />

L11<br />

VCCINT<br />

T11<br />

VCCINT<br />

V11<br />

VCCINT<br />

M12<br />

VCCINT<br />

R12<br />

VCCINT<br />

M15<br />

VCCINT<br />

R15<br />

VCCINT<br />

J16<br />

VCCINT<br />

L16<br />

VCCINT<br />

T16<br />

VCCINT<br />

V16<br />

VCCINT<br />

J17<br />

VCCINT<br />

K17<br />

VCCINT<br />

L17<br />

VCCINT<br />

T17<br />

VCCINT<br />

U17<br />

VCCINT<br />

V17<br />

VCCINT<br />

K18<br />

VCCINT<br />

L18<br />

VCCINT<br />

T18<br />

VCCINT<br />

U18<br />

VCCO_1<br />

E11<br />

VCCO_1<br />

E16<br />

VCCO_2<br />

AB11<br />

VCCO_2<br />

AB16<br />

VCCO_3<br />

B11<br />

VCCO_3<br />

B16<br />

VCCO_4<br />

AE11<br />

VCCO_4<br />

AD15<br />

VCCO_5<br />

H18<br />

VCCO_5<br />

B19<br />

VCCO_5<br />

E19<br />

VCCO_5<br />

H19<br />

VCCO_5<br />

J19<br />

VCCO_5<br />

B22<br />

VCCO_5<br />

F22<br />

VCCO_5<br />

F25<br />

VCCO_6<br />

F2<br />

VCCO_6<br />

B5<br />

VCCO_6<br />

F5<br />

VCCO_6<br />

B8<br />

VCCO_6<br />

E8<br />

VCCO_6<br />

J8<br />

VCCO_6<br />

H9<br />

VCCO_6<br />

H10<br />

VCCO_7<br />

W17<br />

VCCO_7<br />

W18<br />

VCCO_7<br />

V19<br />

VCCO_7<br />

AB19<br />

VCCO_7<br />

AE19<br />

VCCO_7<br />

AA22<br />

VCCO_7<br />

AE22<br />

VCCO_7<br />

AA25<br />

VCCO_8<br />

AA2<br />

VCCO_8<br />

AA5<br />

VCCO_8<br />

AE5<br />

VCCO_8<br />

V8<br />

VCCO_8<br />

W8<br />

VCCO_8<br />

AB8<br />

VCCO_8<br />

AE8<br />

VCCO_8<br />

W9<br />

VCCO_9<br />

M18<br />

VCCO_9<br />

K19<br />

VCCO_9<br />

U19<br />

VCCO_9<br />

L22<br />

VCCO_9<br />

T22<br />

VCCO_9<br />

L25<br />

VCCO_9<br />

T25<br />

VCCO_9<br />

P26<br />

VCCO_10<br />

N1<br />

VCCO_10<br />

L2<br />

VCCO_10<br />

T2<br />

VCCO_10<br />

L5<br />

VCCO_10<br />

T5<br />

VCCO_10<br />

K8<br />

VCCO_10<br />

U8<br />

VCCO_10<br />

R9<br />

VCCO_0<br />

V12<br />

VCCO_0<br />

J15<br />

U1L<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

GND<br />

B1<br />

GND<br />

P1<br />

GND<br />

AE1<br />

GND<br />

A2<br />

GND<br />

B2<br />

GND<br />

AE2<br />

GND<br />

AF2<br />

GND<br />

C3<br />

GND<br />

J3<br />

GND<br />

V3<br />

GND<br />

F6<br />

GND<br />

N6<br />

GND<br />

AA6<br />

GND<br />

C9<br />

GND<br />

AD9<br />

GND<br />

M10<br />

GND<br />

N10<br />

GND<br />

P10<br />

GND<br />

R10<br />

GND<br />

K11<br />

GND<br />

M11<br />

GND<br />

N11<br />

GND<br />

P11<br />

GND<br />

R11<br />

GND<br />

U11<br />

GND<br />

E12<br />

GND<br />

K12<br />

GND<br />

L12<br />

GND<br />

N12<br />

GND<br />

P12<br />

GND<br />

T12<br />

GND<br />

U12<br />

GND<br />

AB12<br />

GND<br />

A13<br />

GND<br />

J13<br />

GND<br />

K13<br />

GND<br />

L13<br />

GND<br />

M13<br />

GND<br />

N13<br />

GND<br />

P13<br />

GND<br />

R13<br />

GND<br />

T13<br />

GND<br />

U13<br />

GND<br />

V13<br />

GND<br />

AF13<br />

GND<br />

A14<br />

GND<br />

J14<br />

GND<br />

K14<br />

GND<br />

L14<br />

GND<br />

M14<br />

GND<br />

N14<br />

GND<br />

P14<br />

GND<br />

R14<br />

GND<br />

T14<br />

GND<br />

U14<br />

GND<br />

V14<br />

GND<br />

AF14<br />

GND<br />

E15<br />

GND<br />

K15<br />

GND<br />

L15<br />

GND<br />

N15<br />

GND<br />

P15<br />

GND<br />

T15<br />

GND<br />

U15<br />

GND<br />

AB15<br />

GND<br />

K16<br />

GND<br />

M16<br />

GND<br />

N16<br />

GND<br />

P16<br />

GND<br />

R16<br />

GND<br />

U16<br />

GND<br />

M17<br />

GND<br />

N17<br />

GND<br />

P17<br />

GND<br />

R17<br />

GND<br />

C18<br />

GND<br />

AD18<br />

GND<br />

F21<br />

GND<br />

P21<br />

GND<br />

AA21<br />

GND<br />

J24<br />

GND<br />

V24<br />

GND<br />

AD24<br />

GND<br />

A25<br />

GND<br />

B25<br />

GND<br />

AE25<br />

GND<br />

AF25<br />

GND<br />

B26<br />

GND<br />

N26<br />

GND<br />

AE26<br />

U1M<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong><br />

VREFN_SM<br />

AE15<br />

VREFP_SM<br />

AE16<br />

AVDD_SM<br />

AF17<br />

VN_SM<br />

AF15<br />

VP_SM<br />

AF16<br />

AVSS_SM<br />

AE17<br />

U1N<br />

<strong>XC4VSX35</strong>-<strong>10FFG668C</strong>

1<br />

1<br />

2<br />

A A<br />

1V2<br />

1V2<br />

B C1_FP C2_FP C3_FP<br />

B<br />

10uF 10V 10uF 10V 10uF 10V<br />

1V2<br />

1V2<br />

C5_MB<br />

220uF 10V<br />

C4_FP<br />

0.1uF 16V<br />

C12_FP<br />

10nF 16V<br />

C5_FP<br />

0.1uF 16V<br />

C13_FP<br />

10nF 16V<br />

C6_FP<br />

0.1uF 16V<br />

C14_FP<br />

10nF 16V<br />

C7_FP<br />

0.1uF 16V<br />

C15_FP<br />

10nF 16V<br />

C8_FP<br />

0.1uF 16V<br />

C16_FP<br />

10nF 16V<br />

C C<br />

GND<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 10 of 23<br />

File: Bypass_FPGA_1V2.SCHDOC<br />

2<br />

C9_FP<br />

0.1uF 16V<br />

C17_FP<br />

10nF 16V<br />

C10_FP<br />

0.1uF 16V<br />

C18_FP<br />

10nF 16V<br />

GND<br />

GND<br />

C11_FP<br />

0.1uF 16V<br />

C19_FP<br />

10nF 16V<br />

GND<br />

3<br />

Sheet Title FPGA Bypass Capacitors for 1V2<br />

3<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

2V5<br />

2V5<br />

B<br />

C21_FP<br />

10uF 10V<br />

B<br />

2V5<br />

2V5<br />

C3_MB<br />

220uF 10V<br />

C22_FP<br />

0.1uF 16V<br />

C28_FP<br />

10nF 16V<br />

C23_FP<br />

0.1uF 16V<br />

C29_FP<br />

10nF 16V<br />

C26_FP<br />

0.1uF 16V<br />

C35_FP<br />

10nF 16V<br />

C36_FP<br />

10nF 16V<br />

C C<br />

GND<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 11 of 23<br />

File: Bypass_FPGA_2V5.SCHDOC<br />

2<br />

3<br />

Sheet Title FPGA Bypass Capacitors for 2V5<br />

3<br />

GND<br />

GND<br />

GND<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

3V3<br />

3V3<br />

B B<br />

GND<br />

3V3<br />

3V3<br />

C38_FP<br />

10uF 10V<br />

C50_FP<br />

0.1uF 16V<br />

C62_FP<br />

10nF 16V<br />

C80_FP<br />

10nF 16V<br />

C<br />

GND<br />

C<br />

3V3<br />

C96_FP<br />

10nF 16V<br />

C39_FP<br />

10uF 10V<br />

C53_FP<br />

0.1uF 16V<br />

C63_FP<br />

10nF 16V<br />

C83_FP<br />

10nF 16V<br />

C99_FP<br />

10nF 16V<br />

C40_FP<br />

10uF 10V<br />

C54_FP<br />

0.1uF 16V<br />

C64_FP<br />

10nF 16V<br />

C84_FP<br />

10nF 16V<br />

C100_FP<br />

10nF 16V<br />

C41_FP<br />

10uF 10V<br />

C55_FP<br />

0.1uF 16V<br />

C66_FP<br />

10nF 16V<br />

C85_FP<br />

10nF 16V<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 12 of 23<br />

File: Bypass_FPGA_3V3.SchDoc<br />

2<br />

C42_FP<br />

10uF 10V<br />

C57_FP<br />

0.1uF 16V<br />

C67_FP<br />

10nF 16V<br />

C86_FP<br />

10nF 16V<br />

C43_FP<br />

10uF 10V<br />

C68_FP<br />

10nF 16V<br />

C87_FP<br />

10nF 16V<br />

C44_FP<br />

10uF 10V<br />

C70_FP<br />

10nF 16V<br />

C89_FP<br />

10nF 16V<br />

C45_FP<br />

10uF 10V<br />

C74_FP<br />

10nF 16V<br />

C92_FP<br />

10nF 16V<br />

3<br />

C75_FP<br />

10nF 16V<br />

C94_FP<br />

10nF 16V<br />

Sheet Title FPGA Bypass Capacitors for 3V3<br />

3<br />

C76_FP<br />

10nF 16V<br />

C77_FP<br />

10nF 16V<br />

C78_FP<br />

10nF 16V<br />

GND<br />

GND<br />

GND<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

4<br />

5<br />

1<br />

U1<br />

DS2406<br />

Vcc DATA<br />

NC PIOB<br />

GND PIOA<br />

2<br />

6<br />

3<br />

ID<br />

PIO2<br />

PIO1<br />

ONE_WIRE<br />

B B<br />

C C<br />

GND GND<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 13 of 23<br />

File: 1WB_DS2406_EPROM.SchDoc<br />

2<br />

3V3<br />

GND<br />

3V3<br />

C1<br />

0.1uF 16V<br />

3V3<br />

C2<br />

10nF 16V<br />

3<br />

Sheet Title 1-Wire Bus ID<br />

3<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

B B<br />

U1_SL<br />

LED2_SL<br />

LED1_SL<br />

SN74LVC1G04DBV<br />

GREEN<br />

RED<br />

C STATUS_LED<br />

1<br />

2<br />

3<br />

NC<br />

A<br />

GND<br />

VCC<br />

Y<br />

5<br />

4 LED_PGM<br />

C<br />

GND<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 14 of 23<br />

File: DB_LEDS.SchDoc<br />

2<br />

GND<br />

STATUS LED POWER LED<br />

C1_SL<br />

0.1uF 16V<br />

3V3 3V3<br />

R2_SL<br />

270R 1%<br />

3V3<br />

3<br />

GND<br />

R1_SL<br />

270R 1%<br />

Sheet Title <strong>Daughter</strong> Board LEDs<br />

3<br />

LED_PWR<br />

4<br />

4

1<br />

1<br />

2<br />

A A<br />

HOSTMEMORY<br />

SDRAM<br />

BUS_A[24..1]<br />

BUS_D[31..0]<br />

BUS_A[24..1]<br />

BUS_D[31..0]<br />

BUS_A[16..2]<br />

BUS_D[31..0]<br />

A[16..2]<br />

D[31..0]<br />

BUS_SDRAM_NCS<br />

BUS_SDRAM_NCAS<br />

BUS_SDRAM_NRAS<br />

BUS_SDRAM_CKE<br />

BUS_SDRAM_CLK<br />

BUS_A[24..1]<br />

BUS_D[15..0]<br />

FLASH<br />

A[24..1]<br />

D[15..0]<br />

COM_FLASH<br />

B<br />

MEM<br />

BUS_FLASH_NCS<br />

BUS_FLASH_NRESET<br />

BUS_FLASH_NBUSY<br />

FLASH_NCS<br />

FLASH_NRESET<br />

FLASH_NBUSY<br />

CM_FLASH<br />

FLASH_S29GL256N11FFIV10_16Mx16<br />

FLASH<br />

B<br />

BUS_SRAM_NCS<br />

BUS_NBE[3..0]<br />

BUS_NOE<br />

BUS_NWE<br />

Common-Bus Memory Block<br />

C C<br />

256K x 32-bit SRAM (1 MByte)<br />

16M x 32-Bit SDRAM (64 MByte)<br />

16M x 16-Bit Flash (32 MByte)<br />

D<br />

<strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 15 of 23<br />

File: NB2_CommonMemory.SchDoc<br />

2<br />

BUS_A[20..2]<br />

BUS_D[31..0]<br />

3<br />

SDRAM_NCS<br />

SDRAM_NCAS<br />

SDRAM_NRAS<br />

SDRAM_CKE<br />

SDRAM_CLK<br />

NBE[3..0]<br />

NWE<br />

NOE<br />

NWE<br />

SRAM<br />

A[20..2]<br />

D[31..0]<br />

NCS<br />

NBE[3..0]<br />

NOE<br />

NWE<br />

Sheet Title Common-Bus Memory Block<br />

3<br />

COM_SDRAM<br />

SDRAM_MT48LC16M16A2TG_16Mx32<br />

CM_SDRAM<br />

SDRAM<br />

CM_SRAM<br />

COM_SRAM<br />

SRAM_256Kx32_TSOP44_1<br />

SRAM<br />

4<br />

4

1<br />

1<br />

FLASH<br />

2<br />

D[15..0]<br />

BUS_D[15..0]<br />

A[24..1]<br />

BUS_A[24..1]<br />

A A<br />

B<br />

FLASH_NCS<br />

NOE<br />

NWE<br />

FLASH_NRESET<br />

BUS_A1<br />

BUS_A2<br />

BUS_A3<br />

BUS_A4<br />

BUS_A5<br />

BUS_A6<br />

BUS_A7<br />

BUS_A8<br />

BUS_A9<br />

BUS_A10<br />

BUS_A11<br />

BUS_A12<br />

BUS_A13<br />

BUS_A14<br />

BUS_A15<br />

BUS_A16<br />

BUS_A17<br />

BUS_A18<br />

BUS_A19<br />

BUS_A20<br />

BUS_A21<br />

BUS_A24<br />

B4<br />

WP#/ACC<br />

BUS_D0<br />

BUS_D1<br />

BUS_D2<br />

BUS_D3<br />

BUS_D4<br />

BUS_D5<br />

BUS_D6<br />

BUS_D7<br />

BUS_D8<br />

BUS_D9<br />

BUS_D10<br />

BUS_D11<br />

BUS_D12<br />

BUS_D13<br />

BUS_D14<br />

BUS_D15<br />

3V3<br />

GND<br />

B<br />

WE#<br />

U1<br />

S29GL256N11FFIV10<br />

FLASH<br />

BUS_A22<br />

BUS_A23<br />

E2<br />

D2<br />

C2<br />

A2<br />

B2<br />

D3<br />

C3<br />

A3<br />

B6<br />

A6<br />

C6<br />

D6<br />

B7<br />

A7<br />

C7<br />

D7<br />

E7<br />

B3<br />

C4<br />

D5<br />

D4<br />

C5<br />

B8<br />

C8<br />

F2<br />

G2<br />

A5<br />

B5<br />

A0<br />

A1<br />

A2<br />

A3<br />

A4<br />

A5<br />

A6<br />

A7<br />

A8<br />

A9<br />

A10<br />

A11<br />

A12<br />

A13<br />

A14<br />

A15<br />

A16<br />

A17<br />

A18<br />

A19<br />

A20<br />

A21<br />

A22<br />

A23<br />

CE#<br />

OE#<br />

RESET#<br />

DQ0<br />

DQ1<br />

DQ2<br />

DQ3<br />

DQ4<br />

DQ5<br />

DQ6<br />

DQ7<br />

DQ8<br />

DQ9<br />

DQ10<br />

DQ11<br />

DQ12<br />

DQ13<br />

DQ14<br />

DQ15/A-1<br />

VCC<br />

VIO<br />

VIO<br />

VSS<br />

VSS<br />

VSS<br />

E3<br />

H3<br />

E4<br />

H4<br />

H5<br />

E5<br />

H6<br />

E6<br />

F3<br />

G3<br />

F4<br />

G4<br />

F5<br />

G6<br />

F6<br />

G7<br />

G5<br />

D8<br />

F1<br />

E8<br />

H7<br />

H2<br />

C C<br />

3V3<br />

FLASH_NBUSY<br />

3V3<br />

3V3<br />

D<br />

C3<br />

10nF 16V<br />

C4<br />

10nF 16V<br />

C5<br />

10nF 16V<br />

C6<br />

0.1uF 16V<br />

C1<br />

0.1uF 16V<br />

C2<br />

0.1uF 16V<br />

Sheet Title 16M x 16 Flash Memory (BGA) <strong>Altium</strong> Limited<br />

D<br />

Project Title <strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

Size: A4 Assy: D-820-0031 Revision: 02<br />

NSW 2086<br />

Australia<br />

GND GND GND GND GND GND<br />

Date: 27/11/2008 Time: 4:51:04 PM Sheet 16 of 23<br />

File: FLASH_S29GL256N11FFIV10_16Mx16.SchDoc<br />

2<br />

3V3<br />

3V3<br />

3V3<br />

F7<br />

3V3<br />

BYTE#<br />

NC<br />

NC<br />

NC<br />

NC<br />

NC<br />

NC<br />

NC<br />

NC<br />

NC<br />

NC<br />

NC<br />

A8<br />

F8<br />

G8<br />

H8<br />

A1<br />

B1<br />

C1<br />

D1<br />

E1<br />

G1<br />

H1<br />

3<br />

RY/BY#<br />

3<br />

A4<br />

4<br />

4

1<br />

1<br />

2<br />

2<br />

3<br />

3<br />

4<br />

4<br />

D D<br />

C C<br />

B B<br />

A A<br />

17 23<br />

<strong>DB46</strong> - <strong>Virtex</strong>4 SX35<br />

02<br />

27/11/2008 4:51:04 PM<br />

SDRAM_MT48LC16M16A2TG_16Mx32.SchDoc<br />

Project Title<br />

Size:<br />

Date:<br />

File:<br />

Revision:<br />

Sheet of<br />

Time:<br />

A4<br />

Sheet Title 16M x 32 SDRAM TSOP54 x 2<br />

Assy: D-820-0031<br />

<strong>Altium</strong> Limited<br />

L3, 12A Rodborough Road<br />

Frenchs Forest<br />

NSW 2086<br />

Australia<br />

A[16..2]<br />

D[31..0]<br />

NBE[3..0]<br />

NWE<br />

SDRAM_NCAS<br />

SDRAM_NRAS<br />

SDRAM_CKE<br />

SDRAM_CLK<br />

SDRAM_NCS<br />

SDRAM<br />

BUS_SDRAM_CLK<br />

BUS_SDRAM_CKE<br />

BUS_SDRAM_CLK<br />

BUS_SDRAM_CKE<br />

GND<br />

GND<br />

BUS_A[16..2]<br />

BUS_D[31..0]<br />

BUS_NBE[3..0]<br />

BUS_SDRAM_NCAS<br />

BUS_SDRAM_NRAS<br />

VDD<br />

1<br />

DQ0<br />

2<br />

VDDQ<br />

3<br />

DQ1<br />

4<br />

DQ2<br />

5<br />

VSSQ<br />

6<br />

DQ3<br />

7<br />

DQ4<br />

8<br />

VDDQ<br />

9<br />

DQ5<br />

10<br />

DQ6<br />

11<br />

VSSQ<br />

12<br />

DQ7<br />

13<br />

VDD<br />

14<br />

DQML<br />

15<br />

WE<br />

16<br />

CAS<br />

17<br />

RAS<br />

18<br />

CS<br />

19<br />

BA0<br />

20<br />

BA1<br />

21<br />

A10<br />

22<br />

A0<br />

23<br />

A1<br />

24<br />

A2<br />

25<br />

A3<br />

26<br />

VDD<br />

27<br />

VSS<br />

28<br />

A4<br />

29<br />

A5<br />

30<br />

A6<br />

31<br />

A7<br />

32<br />

A8<br />

33<br />

A9<br />

34<br />

A11<br />

35<br />

A12<br />

36<br />

CKE<br />

37<br />

CLK<br />

38<br />

DQMH<br />

39<br />

NC<br />

40<br />

VSS<br />

41<br />

DQ8<br />

42<br />

VDDQ<br />

43<br />

DQ9<br />

44<br />

DQ10<br />

45<br />

VSSQ<br />

46<br />

DQ11<br />

47<br />

DQ12<br />

48<br />

VDDQ<br />

49<br />

DQ13<br />

50<br />

DQ14<br />

51<br />

VSSQ<br />

52<br />

DQ15<br />

53<br />

VSS<br />

54<br />

U2<br />

SDRAM-16Mx16<br />

VDD<br />

1<br />

DQ0<br />

2<br />

VDDQ<br />

3<br />

DQ1<br />

4<br />

DQ2<br />

5<br />

VSSQ<br />

6<br />

DQ3<br />

7<br />

DQ4<br />

8<br />

VDDQ<br />

9<br />

DQ5<br />

10<br />

DQ6<br />

11<br />

VSSQ<br />

12<br />

DQ7<br />

13<br />

VDD<br />

14<br />

DQML<br />

15<br />

WE<br />

16<br />

CAS<br />

17<br />

RAS<br />

18<br />

CS<br />

19<br />

BA0<br />

20<br />

BA1<br />

21<br />

A10<br />

22<br />

A0<br />

23<br />

A1<br />

24<br />

A2<br />

25<br />

A3<br />

26<br />

VDD<br />

27<br />

VSS<br />

28<br />

A4<br />

29<br />

A5<br />

30<br />

A6<br />

31<br />

A7<br />

32<br />

A8<br />

33<br />

A9<br />

34<br />

A11<br />

35<br />

A12<br />

36<br />

CKE<br />

37<br />

CLK<br />

38<br />

DQMH<br />

39<br />

NC<br />

40<br />

VSS<br />

41<br />

DQ8<br />

42<br />

VDDQ<br />

43<br />

DQ9<br />

44<br />

DQ10<br />

45<br />

VSSQ<br />

46<br />

DQ11<br />

47<br />

DQ12<br />

48<br />

VDDQ<br />

49<br />

DQ13<br />

50<br />

DQ14<br />

51<br />

VSSQ<br />

52<br />

DQ15<br />

53<br />

VSS<br />

54<br />

U1<br />

SDRAM-16Mx16<br />

BUS_SDRAM_CLK<br />

BUS_SDRAM_CKE<br />

BUS_NWE<br />

BUS_A2<br />

BUS_A3<br />

BUS_A4<br />

BUS_A5<br />

BUS_A6<br />

BUS_A7<br />

BUS_A8<br />

BUS_A9<br />

BUS_A10<br />

BUS_A11<br />

BUS_A12<br />

BUS_D0<br />

BUS_D2<br />

BUS_D1<br />

BUS_D4<br />

BUS_D3<br />

BUS_D6<br />

BUS_D5<br />

BUS_D7<br />

BUS_D8<br />

BUS_D9<br />

BUS_D10<br />

BUS_D12<br />

BUS_D11<br />

BUS_D15<br />

BUS_D14<br />

BUS_D13<br />

BUS_A15<br />

BUS_A16<br />

BUS_A2<br />

BUS_A3<br />

BUS_A4<br />

BUS_A5<br />

BUS_A6<br />

BUS_A7<br />

BUS_A8<br />

BUS_A9<br />

BUS_A10<br />

BUS_A11<br />

BUS_A12<br />

BUS_SDRAM_NCS<br />

BUS_NWE<br />

BUS_SDRAM_NCAS<br />

BUS_SDRAM_NRAS<br />

BUS_NBE0<br />

BUS_NBE1<br />

BUS_NBE2<br />

BUS_NBE3<br />

BUS_SDRAM_NCS<br />

BUS_NWE<br />

BUS_SDRAM_NCAS<br />

BUS_SDRAM_NRAS<br />

BUS_A13<br />

BUS_A14<br />

BUS_A13<br />

BUS_A14<br />

BUS_SDRAM_NCS<br />

3V3<br />

C1<br />

0.1uF 16V<br />

C7<br />

10nF 16V<br />

C6<br />

10nF 16V<br />

C5<br />

10nF 16V<br />

C8<br />

10nF 16V<br />

C4<br />

0.1uF 16V<br />

C2<br />

0.1uF 16V<br />

C3<br />

0.1uF 16V<br />

BUS_D16<br />

BUS_D18<br />

BUS_D17<br />

BUS_D20<br />

BUS_D19<br />

BUS_D22<br />

BUS_D21<br />

BUS_D23<br />

BUS_D24<br />

BUS_D25<br />

BUS_D26<br />

BUS_D28<br />

BUS_D27<br />

BUS_D31<br />

BUS_D30<br />

BUS_D29<br />

BUS_A15<br />

BUS_A16<br />

GND<br />

3V3<br />

GND<br />

3V3<br />

GND<br />

3V3<br />

GND<br />

3V3<br />

GND<br />

3V3<br />

GND<br />

3V3<br />

GND<br />

3V3<br />

GND<br />

3V3<br />

3V3<br />

SDRAM

1<br />

1<br />

2<br />

A A<br />

A18 is connected so<br />

that 512KBx16 device<br />

can be fitted<br />

SRAM_A2 1<br />

44 SRAM_A19<br />

SRAM_A2 1<br />

44 SRAM_A19<br />

A0 A17<br />

A0 A17<br />

SRAM_A3 2<br />

43 SRAM_A18<br />

SRAM_A3 2<br />

43 SRAM_A18<br />

A1 A16<br />

A1 A16<br />

SRAM_A4 3<br />

42 SRAM_A17<br />

SRAM_A4 3<br />

42 SRAM_A17<br />

A2 A15<br />

A2 A15<br />

SRAM_A5 4<br />

41 SRAM_NOE<br />

SRAM_A5 4<br />

41 SRAM_NOE<br />

A3 OE<br />

A3 OE<br />

SRAM_A6 5<br />

40 SRAM_NBE1<br />

SRAM_A6 5<br />

40 SRAM_NBE3<br />

A4 BHE<br />

A4 BHE<br />

SRAM_NCS 6<br />

39 SRAM_NBE0<br />