Affirma Spectre DC Device Matching Analysis Tutorial - Cadence ...

Affirma Spectre DC Device Matching Analysis Tutorial - Cadence ...

Affirma Spectre DC Device Matching Analysis Tutorial - Cadence ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Affirma</strong> <strong>Spectre</strong> <strong>DC</strong> <strong>Device</strong> <strong>Matching</strong> <strong>Analysis</strong> <strong>Tutorial</strong><br />

∂<br />

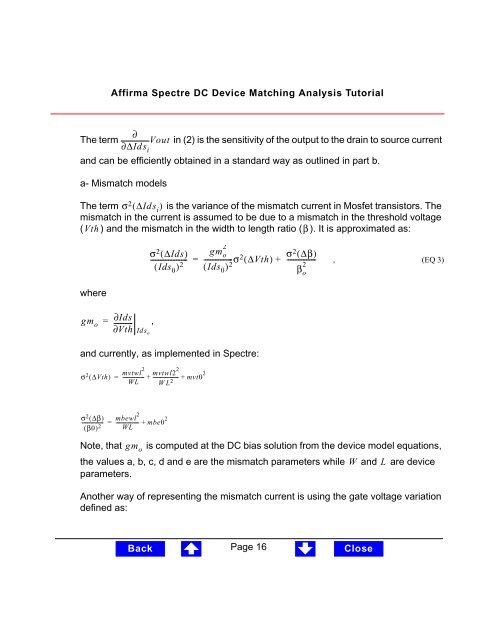

The term Vout in (2) is the sensitivity of the output to the drain to source current<br />

∂ΔIdsi<br />

and can be efficiently obtained in a standard way as outlined in part b.<br />

a- Mismatch models<br />

The term σ is the variance of the mismatch current in Mosfet transistors. The<br />

mismatch in the current is assumed to be due to a mismatch in the threshold voltage<br />

( ) and the mismatch in the width to length ratio ( ). It is approximated as:<br />

2( ΔIdsi) Vth β<br />

where<br />

gm o<br />

= ∂Ids<br />

----------- ,<br />

∂Vth<br />

Idso<br />

2<br />

gmo σ2( ΔIds)<br />

( Ids0) 2<br />

----------------------<br />

( Ids0) 2<br />

-----------------σ 2 σ<br />

( ΔVth)<br />

2( Δβ)<br />

=<br />

+ -----------------<br />

2<br />

βo and currently, as implemented in <strong>Spectre</strong>:<br />

σ2( ΔVth)<br />

σ2( Δβ)<br />

( β0)<br />

2<br />

----------------- =<br />

=<br />

mvtwl 2<br />

-----------------<br />

WL<br />

mvtwl22<br />

WL2 -------------------- mvt0 2<br />

+ +<br />

mbewl 2<br />

------------------ mbe0<br />

WL<br />

2<br />

+<br />

, (EQ 3)<br />

Note, that gmo is computed at the <strong>DC</strong> bias solution from the device model equations,<br />

the values a, b, c, d and e are the mismatch parameters while W and L<br />

are device<br />

parameters.<br />

Another way of representing the mismatch current is using the gate voltage variation<br />

defined as:<br />

Release Date Back Page 16<br />

Close<br />

16