Solutions for Mixed-Signal SoC Implementation - Cadence Design ...

Solutions for Mixed-Signal SoC Implementation - Cadence Design ... Solutions for Mixed-Signal SoC Implementation - Cadence Design ...

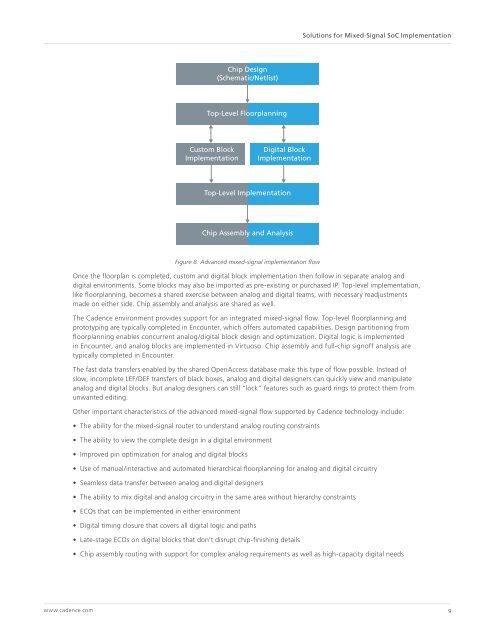

Digital timing verification The verification of digital timing paths inside mixed-signal blocks is problematic in traditional netlist-driven flows. Typically, digital implementation tools extract path parasitics only to the analog IP block’s instance pin, and any loading inside the block is modeled by a .lib file (Figure 7, left). Generating that .lib file amounts to a generally painful experience for analog designers. A better approach provided by the Encounter Digital Implementation system involves extracting full-path parasitics all the way to the digital instance pin (Figure 7, right). The tool models the loading of the digital path inside a mixed-signal block as a distributed RC network. Internal loading is thus appended to the extracted path, and static timing analysis can verify the complete path with no need to generate a .lib file. Digital I1 I2 Path parasitics extracted to AMS instance pin Digital cell library instances AMS AMS Partition .lib Towards a new mixed-signal implementation flow Digital I1 Extract full path parasitics to digital instance pin Figure 7: Extracting full-path parasitics allows timing closure on mixed-signal blocks without requiring generation of a .lib file. Solutions for Mixed-Signal SoC Implementation I2 AMS Partition The schematic-driven and netlist-driven flows are block-based approaches that involve the import of one type of block into a larger analog or digital environment. The emerging mixed-signal flow represents a much more integrated methodology. While the new flow retains separate analog and digital design teams and tools, responsibility for the overall design, verification and chip tapeout is shared. One big advance with this new approach is that analog and digital blocks can be designed concurrently. Floorplanning can be truly mixed-signal, with flexibility to assign or optimize pins. With flexible pinouts, designers do not need to send analog or digital blocks back for rework if they find that fixed pinouts don’t work in a floorplan. Results can include earlier floorplanning, smaller area, less routing congestion, earlier chip finishing, and faster overall turn-around times. Figure 8 shows an advanced mixed-signal implementation flow. Notice how the top-level floorplan becomes a joint exercise between analog and digital design groups. These teams concurrently optimize the floorplan, changing pinouts and locations and routing nets as needed, until they can both sign off on the floorplan. Each team must be aware of the constraints on the other side. www.cadence.com 8

Chip Design (Schematic/Netlist) Top-Level Floorplanning Custom Block Implementation Digital Block Implementation Top-Level Implementation Chip Assembly and Analysis Figure 8: Advanced mixed-signal implementation flow Once the floorplan is completed, custom and digital block implementation then follow in separate analog and digital environments. Some blocks may also be imported as pre-existing or purchased IP. Top-level implementation, like floorplanning, becomes a shared exercise between analog and digital teams, with necessary readjustments made on either side. Chip assembly and analysis are shared as well. The Cadence environment provides support for an integrated mixed-signal flow. Top-level floorplanning and prototyping are typically completed in Encounter, which offers automated capabilities. Design partitioning from floorplanning enables concurrent analog/digital block design and optimization. Digital logic is implemented in Encounter, and analog blocks are implemented in Virtuoso. Chip assembly and full-chip signoff analysis are typically completed in Encounter. The fast data transfers enabled by the shared OpenAccess database make this type of flow possible. Instead of slow, incomplete LEF/DEF transfers of black boxes, analog and digital designers can quickly view and manipulate analog and digital blocks. But analog designers can still “lock” features such as guard rings to protect them from unwanted editing. Other important characteristics of the advanced mixed-signal flow supported by Cadence technology include: • The ability for the mixed-signal router to understand analog routing constraints • The ability to view the complete design in a digital environment • Improved pin optimization for analog and digital blocks • Use of manual/interactive and automated hierarchical floorplanning for analog and digital circuitry • Seamless data transfer between analog and digital designers • The ability to mix digital and analog circuitry in the same area without hierarchy constraints • ECOs that can be implemented in either environment • Digital timing closure that covers all digital logic and paths • Late-stage ECOs on digital blocks that don’t disrupt chip-finishing details Solutions for Mixed-Signal SoC Implementation • Chip assembly routing with support for complex analog requirements as well as high-capacity digital needs www.cadence.com 9

- Page 1 and 2: Solutions for Mixed-Signal SoC Impl

- Page 3 and 4: When analog blocks are imported int

- Page 5 and 6: Chip Design (Schematic) Top-Level F

- Page 7: Floorplanning and prototyping prece

Chip <strong>Design</strong><br />

(Schematic/Netlist)<br />

Top-Level Floorplanning<br />

Custom Block<br />

<strong>Implementation</strong><br />

Digital Block<br />

<strong>Implementation</strong><br />

Top-Level <strong>Implementation</strong><br />

Chip Assembly and Analysis<br />

Figure 8: Advanced mixed-signal implementation flow<br />

Once the floorplan is completed, custom and digital block implementation then follow in separate analog and<br />

digital environments. Some blocks may also be imported as pre-existing or purchased IP. Top-level implementation,<br />

like floorplanning, becomes a shared exercise between analog and digital teams, with necessary readjustments<br />

made on either side. Chip assembly and analysis are shared as well.<br />

The <strong>Cadence</strong> environment provides support <strong>for</strong> an integrated mixed-signal flow. Top-level floorplanning and<br />

prototyping are typically completed in Encounter, which offers automated capabilities. <strong>Design</strong> partitioning from<br />

floorplanning enables concurrent analog/digital block design and optimization. Digital logic is implemented<br />

in Encounter, and analog blocks are implemented in Virtuoso. Chip assembly and full-chip signoff analysis are<br />

typically completed in Encounter.<br />

The fast data transfers enabled by the shared OpenAccess database make this type of flow possible. Instead of<br />

slow, incomplete LEF/DEF transfers of black boxes, analog and digital designers can quickly view and manipulate<br />

analog and digital blocks. But analog designers can still “lock” features such as guard rings to protect them from<br />

unwanted editing.<br />

Other important characteristics of the advanced mixed-signal flow supported by <strong>Cadence</strong> technology include:<br />

• The ability <strong>for</strong> the mixed-signal router to understand analog routing constraints<br />

• The ability to view the complete design in a digital environment<br />

• Improved pin optimization <strong>for</strong> analog and digital blocks<br />

• Use of manual/interactive and automated hierarchical floorplanning <strong>for</strong> analog and digital circuitry<br />

• Seamless data transfer between analog and digital designers<br />

• The ability to mix digital and analog circuitry in the same area without hierarchy constraints<br />

• ECOs that can be implemented in either environment<br />

• Digital timing closure that covers all digital logic and paths<br />

• Late-stage ECOs on digital blocks that don’t disrupt chip-finishing details<br />

<strong>Solutions</strong> <strong>for</strong> <strong>Mixed</strong>-<strong>Signal</strong> <strong>SoC</strong> <strong>Implementation</strong><br />

• Chip assembly routing with support <strong>for</strong> complex analog requirements as well as high-capacity digital needs<br />

www.cadence.com 9