Solutions for Mixed-Signal SoC Implementation - Cadence Design ...

Solutions for Mixed-Signal SoC Implementation - Cadence Design ...

Solutions for Mixed-Signal SoC Implementation - Cadence Design ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

VIRTUOSO<br />

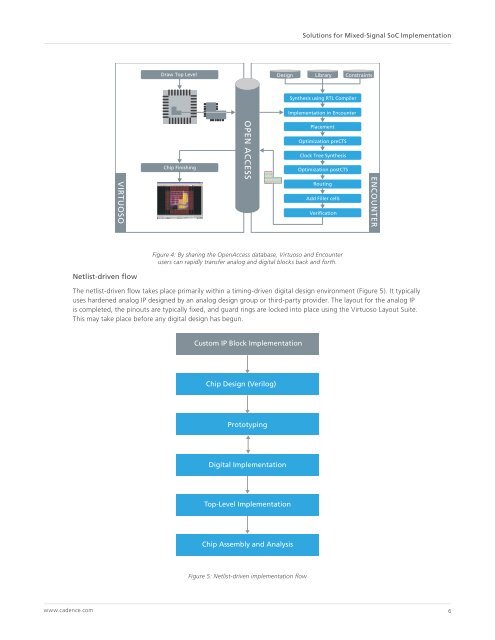

Netlist-driven flow<br />

Draw Top Level<br />

Chip Finishing<br />

OPEN ACCESS<br />

<strong>Design</strong> Library Constraints<br />

Synthesis using RTL Compiler<br />

<strong>Implementation</strong> in Encounter<br />

Placement<br />

Optimization preCTS<br />

Clock Tree Synthesis<br />

Optimization postCTS<br />

Routing<br />

Add Filler cells<br />

Verification<br />

Figure 4: By sharing the OpenAccess database, Virtuoso and Encounter<br />

users can rapidly transfer analog and digital blocks back and <strong>for</strong>th.<br />

The netlist-driven flow takes place primarily within a timing-driven digital design environment (Figure 5). It typically<br />

uses hardened analog IP designed by an analog design group or third-party provider. The layout <strong>for</strong> the analog IP<br />

is completed, the pinouts are typically fixed, and guard rings are locked into place using the Virtuoso Layout Suite.<br />

This may take place be<strong>for</strong>e any digital design has begun.<br />

Custom IP Block <strong>Implementation</strong><br />

Chip <strong>Design</strong> (Verilog)<br />

Prototyping<br />

Digital <strong>Implementation</strong><br />

Top-Level <strong>Implementation</strong><br />

Chip Assembly and Analysis<br />

Figure 5: Netlist-driven implementation flow<br />

<strong>Solutions</strong> <strong>for</strong> <strong>Mixed</strong>-<strong>Signal</strong> <strong>SoC</strong> <strong>Implementation</strong><br />

www.cadence.com 6<br />

ENCOUNTER