Damage formation and annealing studies of low energy ion implants ...

Damage formation and annealing studies of low energy ion implants ...

Damage formation and annealing studies of low energy ion implants ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

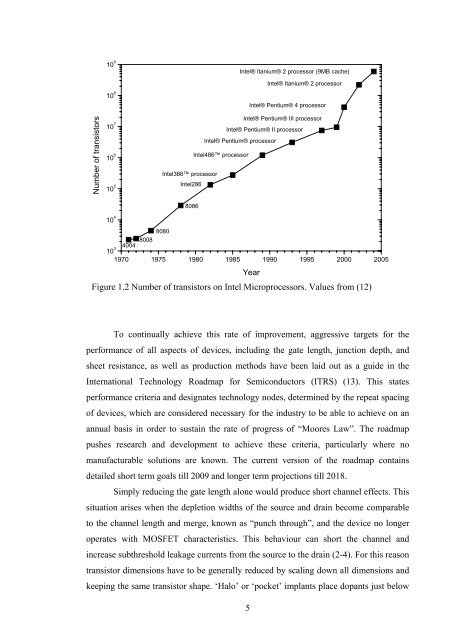

Number <strong>of</strong> transistors<br />

10 9<br />

10 8<br />

10 7<br />

10 6<br />

10 5<br />

10 4<br />

10 3<br />

4004 8008<br />

Intel386 processor<br />

8080<br />

Intel286<br />

8086<br />

Intel486 processor<br />

Intel® Itanium® 2 processor (9MB cache)<br />

Intel® Pentium® processor<br />

Intel® Pentium® III processor<br />

Intel® Pentium® II processor<br />

1970 1975 1980 1985 1990 1995 2000 2005<br />

Year<br />

To continually achieve this rate <strong>of</strong> improvement, aggressive targets for the<br />

performance <strong>of</strong> all aspects <strong>of</strong> devices, including the gate length, junct<strong>ion</strong> depth, <strong>and</strong><br />

sheet resistance, as well as product<strong>ion</strong> methods have been laid out as a guide in the<br />

Internat<strong>ion</strong>al Technology Roadmap for Semiconductors (ITRS) (13). This states<br />

performance criteria <strong>and</strong> designates technology nodes, determined by the repeat spacing<br />

<strong>of</strong> devices, which are considered necessary for the industry to be able to achieve on an<br />

annual basis in order to sustain the rate <strong>of</strong> progress <strong>of</strong> “Moores Law”. The roadmap<br />

pushes research <strong>and</strong> development to achieve these criteria, particularly where no<br />

manufacturable solut<strong>ion</strong>s are known. The current vers<strong>ion</strong> <strong>of</strong> the roadmap contains<br />

detailed short term goals till 2009 <strong>and</strong> longer term project<strong>ion</strong>s till 2018.<br />

Simply reducing the gate length alone would produce short channel effects. This<br />

situat<strong>ion</strong> arises when the deplet<strong>ion</strong> widths <strong>of</strong> the source <strong>and</strong> drain become comparable<br />

to the channel length <strong>and</strong> merge, known as “punch through”, <strong>and</strong> the device no longer<br />

operates with MOSFET characteristics. This behaviour can short the channel <strong>and</strong><br />

increase subthreshold leakage currents from the source to the drain (2-4). For this reason<br />

transistor dimens<strong>ion</strong>s have to be generally reduced by scaling down all dimens<strong>ion</strong>s <strong>and</strong><br />

keeping the same transistor shape. ‘Halo’ or ‘pocket’ <strong>implants</strong> place dopants just be<strong>low</strong><br />

5<br />

Intel® Itanium® 2 processor<br />

Intel® Pentium® 4 processor<br />

Figure 1.2 Number <strong>of</strong> transistors on Intel Microprocessors. Values from (12)