Sable CPU Module Specification

Sable CPU Module Specification

Sable CPU Module Specification

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Copyright © 1993 Digital Equipment Corporation.<br />

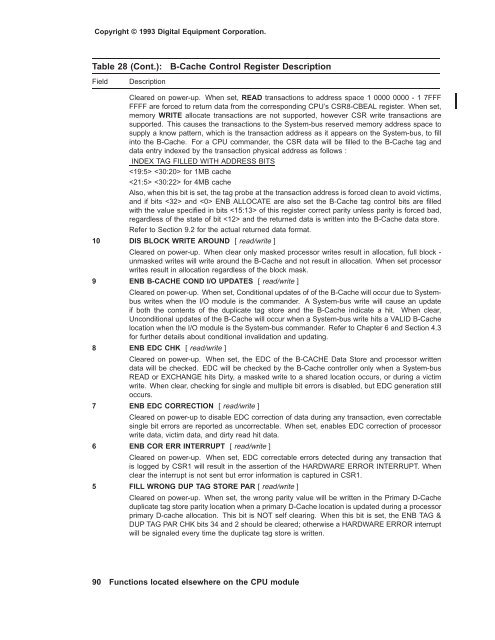

Table 28 (Cont.): B-Cache Control Register Description<br />

Field Description<br />

Cleared on power-up. When set, READ transactions to address space 1 0000 0000 - 1 7FFF<br />

FFFF are forced to return data from the corresponding <strong>CPU</strong>’s CSR8-CBEAL register. When set,<br />

memory WRITE allocate transactions are not supported, however CSR write transactions are<br />

supported. This causes the transactions to the System-bus reserved memory address space to<br />

supply a know pattern, which is the transaction address as it appears on the System-bus, to fill<br />

into the B-Cache. For a <strong>CPU</strong> commander, the CSR data will be filled to the B-Cache tag and<br />

data entry indexed by the transaction physical address as follows :<br />

INDEX TAG FILLED WITH ADDRESS BITS<br />

for 1MB cache<br />

for 4MB cache<br />

Also, when this bit is set, the tag probe at the transaction address is forced clean to avoid victims,<br />

and if bits and ENB ALLOCATE are also set the B-Cache tag control bits are filled<br />

with the value specified in bits of this register correct parity unless parity is forced bad,<br />

regardless of the state of bit and the returned data is written into the B-Cache data store.<br />

Refer to Section 9.2 for the actual returned data format.<br />

10 DIS BLOCK WRITE AROUND [ read/write ]<br />

Cleared on power-up. When clear only masked processor writes result in allocation, full block -<br />

unmasked writes will write around the B-Cache and not result in allocation. When set processor<br />

writes result in allocation regardless of the block mask.<br />

9 ENB B-CACHE COND I/O UPDATES [ read/write ]<br />

Cleared on power-up. When set, Conditional updates of of the B-Cache will occur due to Systembus<br />

writes when the I/O module is the commander. A System-bus write will cause an update<br />

if both the contents of the duplicate tag store and the B-Cache indicate a hit. When clear,<br />

Unconditional updates of the B-Cache will occur when a System-bus write hits a VALID B-Cache<br />

location when the I/O module is the System-bus commander. Refer to Chapter 6 and Section 4.3<br />

for further details about conditional invalidation and updating.<br />

8 ENB EDC CHK [ read/write ]<br />

Cleared on power-up. When set, the EDC of the B-CACHE Data Store and processor written<br />

data will be checked. EDC will be checked by the B-Cache controller only when a System-bus<br />

READ or EXCHANGE hits Dirty, a masked write to a shared location occurs, or during a victim<br />

write. When clear, checking for single and multiple bit errors is disabled, but EDC generation still<br />

occurs.<br />

7 ENB EDC CORRECTION [ read/write ]<br />

Cleared on power-up to disable EDC correction of data during any transaction, even correctable<br />

single bit errors are reported as uncorrectable. When set, enables EDC correction of processor<br />

write data, victim data, and dirty read hit data.<br />

6 ENB COR ERR INTERRUPT [ read/write ]<br />

Cleared on power-up. When set, EDC correctable errors detected during any transaction that<br />

is logged by CSR1 will result in the assertion of the HARDWARE ERROR INTERRUPT. When<br />

clear the interrupt is not sent but error information is captured in CSR1.<br />

5 FILL WRONG DUP TAG STORE PAR [ read/write ]<br />

Cleared on power-up. When set, the wrong parity value will be written in the Primary D-Cache<br />

duplicate tag store parity location when a primary D-Cache location is updated during a processor<br />

primary D-cache allocation. This bit is NOT self clearing. When this bit is set, the ENB TAG &<br />

DUP TAG PAR CHK bits 34 and 2 should be cleared; otherwise a HARDWARE ERROR interrupt<br />

will be signaled every time the duplicate tag store is written.<br />

90 Functions located elsewhere on the <strong>CPU</strong> module

![Volume 3: Instruction Set Reference [pdf]](https://img.yumpu.com/5683779/1/190x252/volume-3-instruction-set-reference-pdf.jpg?quality=85)