- Page 1 and 2:

Sable CPU Module Specification This

- Page 3 and 4:

CONTENTS Preface ..................

- Page 5 and 6:

3.9.6 Data Cache Address Register (

- Page 7 and 8:

7.1.1 Exception Handling ..........

- Page 9 and 10:

11.4 Environmental Specifications -

- Page 11 and 12:

25 MM_CSR .........................

- Page 13 and 14:

27 Base Addresses for CSRs . . . ..

- Page 15 and 16:

Preface Scope and Organization of t

- Page 17 and 18:

Copyright © 1993 Digital Equipment

- Page 19 and 20:

CHAPTER 1 CPU MODULE COMPONENTS AND

- Page 21 and 22:

Copyright © 1993 Digital Equipment

- Page 23 and 24:

1.2 The Alpha AXP Architecture Copy

- Page 25 and 26:

Copyright © 1993 Digital Equipment

- Page 27 and 28:

Copyright © 1993 Digital Equipment

- Page 29 and 30:

Copyright © 1993 Digital Equipment

- Page 31 and 32:

Copyright © 1993 Digital Equipment

- Page 33 and 34:

Copyright © 1993 Digital Equipment

- Page 35 and 36:

Copyright © 1993 Digital Equipment

- Page 37 and 38:

Copyright © 1993 Digital Equipment

- Page 39 and 40:

Copyright © 1993 Digital Equipment

- Page 41 and 42:

Copyright © 1993 Digital Equipment

- Page 43 and 44:

Copyright © 1993 Digital Equipment

- Page 45 and 46:

Copyright © 1993 Digital Equipment

- Page 47 and 48:

Copyright © 1993 Digital Equipment

- Page 49 and 50:

Copyright © 1993 Digital Equipment

- Page 51 and 52: Copyright © 1993 Digital Equipment

- Page 53 and 54: Copyright © 1993 Digital Equipment

- Page 55 and 56: Copyright © 1993 Digital Equipment

- Page 57 and 58: Copyright © 1993 Digital Equipment

- Page 59 and 60: Copyright © 1993 Digital Equipment

- Page 61 and 62: Copyright © 1993 Digital Equipment

- Page 63 and 64: Copyright © 1993 Digital Equipment

- Page 65 and 66: Copyright © 1993 Digital Equipment

- Page 67 and 68: Copyright © 1993 Digital Equipment

- Page 69 and 70: Copyright © 1993 Digital Equipment

- Page 71 and 72: Copyright © 1993 Digital Equipment

- Page 73 and 74: Copyright © 1993 Digital Equipment

- Page 75 and 76: Copyright © 1993 Digital Equipment

- Page 77 and 78: Copyright © 1993 Digital Equipment

- Page 79 and 80: Copyright © 1993 Digital Equipment

- Page 81 and 82: Copyright © 1993 Digital Equipment

- Page 83 and 84: Copyright © 1993 Digital Equipment

- Page 85 and 86: Copyright © 1993 Digital Equipment

- Page 87 and 88: Copyright © 1993 Digital Equipment

- Page 89 and 90: Copyright © 1993 Digital Equipment

- Page 91 and 92: Copyright © 1993 Digital Equipment

- Page 93 and 94: Copyright © 1993 Digital Equipment

- Page 95 and 96: Copyright © 1993 Digital Equipment

- Page 97 and 98: Copyright © 1993 Digital Equipment

- Page 99 and 100: CHAPTER 4 FUNCTIONS LOCATED ELSEWHE

- Page 101: Copyright © 1993 Digital Equipment

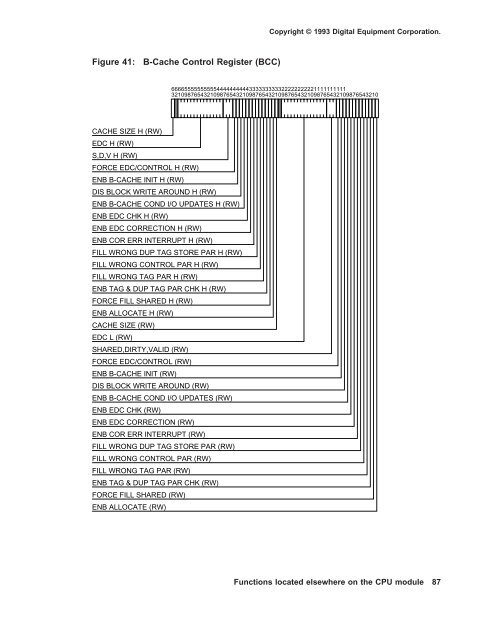

- Page 105 and 106: Table 28 (Cont.): B-Cache Control R

- Page 107 and 108: Table 28 (Cont.): B-Cache Control R

- Page 109 and 110: Copyright © 1993 Digital Equipment

- Page 111 and 112: Copyright © 1993 Digital Equipment

- Page 113 and 114: Copyright © 1993 Digital Equipment

- Page 115 and 116: Copyright © 1993 Digital Equipment

- Page 117 and 118: Copyright © 1993 Digital Equipment

- Page 119 and 120: Copyright © 1993 Digital Equipment

- Page 121 and 122: 4.3.1 Duplicate Tag Error Register

- Page 123 and 124: 4.5 Lack of Cache Block Prefetch Co

- Page 125 and 126: Table 37: System-bus Control Regist

- Page 127 and 128: 4.7.2 System-bus Error Register - C

- Page 129 and 130: Table 38: System-bus Error Register

- Page 131 and 132: Table 38 (Cont.): System-bus Error

- Page 133 and 134: 4.7.3 System-bus Error Address Low

- Page 135 and 136: Copyright © 1993 Digital Equipment

- Page 137 and 138: 4.8 Multiprocessor Configuration CS

- Page 139 and 140: 4.9 System Interrupt Clear Register

- Page 141 and 142: 4.10 Address Lock Register - CSR13

- Page 143 and 144: 4.11 Miss Address Register - CSR14

- Page 145 and 146: Table 46 (Cont.): C4 Revision Regis

- Page 147 and 148: Table 48 (Cont.): Interval Timer In

- Page 149 and 150: Table 50: D-bus Microcontroller Clo

- Page 151 and 152: Figure 58: Granting Order rule 4 CP

- Page 153 and 154:

Copyright © 1993 Digital Equipment

- Page 155 and 156:

Table 54 (Cont.): BIU_CTL Field Des

- Page 157 and 158:

Table 57: CPU EEPROM Defaults Locat

- Page 159 and 160:

Copyright © 1993 Digital Equipment

- Page 161 and 162:

Copyright © 1993 Digital Equipment

- Page 163 and 164:

Copyright © 1993 Digital Equipment

- Page 165 and 166:

Copyright © 1993 Digital Equipment

- Page 167 and 168:

Copyright © 1993 Digital Equipment

- Page 169 and 170:

Copyright © 1993 Digital Equipment

- Page 171 and 172:

Copyright © 1993 Digital Equipment

- Page 173 and 174:

Copyright © 1993 Digital Equipment

- Page 175 and 176:

Copyright © 1993 Digital Equipment

- Page 177 and 178:

Copyright © 1993 Digital Equipment

- Page 179 and 180:

Copyright © 1993 Digital Equipment

- Page 181 and 182:

Copyright © 1993 Digital Equipment

- Page 183 and 184:

Copyright © 1993 Digital Equipment

- Page 185 and 186:

Copyright © 1993 Digital Equipment

- Page 187 and 188:

Copyright © 1993 Digital Equipment

- Page 189 and 190:

Copyright © 1993 Digital Equipment

- Page 191 and 192:

Copyright © 1993 Digital Equipment

- Page 193 and 194:

Copyright © 1993 Digital Equipment

- Page 195 and 196:

Copyright © 1993 Digital Equipment

- Page 197 and 198:

Copyright © 1993 Digital Equipment

- Page 199 and 200:

Copyright © 1993 Digital Equipment

- Page 201 and 202:

Copyright © 1993 Digital Equipment

- Page 203 and 204:

Copyright © 1993 Digital Equipment

- Page 205 and 206:

Copyright © 1993 Digital Equipment

- Page 207 and 208:

Copyright © 1993 Digital Equipment

- Page 209 and 210:

Copyright © 1993 Digital Equipment

- Page 211 and 212:

CHAPTER 11 PHYSICAL AND ELECTRICAL

- Page 213 and 214:

Table 81 (Cont.): MCA240 J5 SIDE 1

- Page 215 and 216:

Table 82 (Cont.): MCA44 J1 Side 1 S

- Page 217 and 218:

11.3 CPU Module Max DC Power Requir

- Page 219 and 220:

Copyright © 1993 Digital Equipment

- Page 221 and 222:

Figure 68: module clocks Cobra - b

- Page 223 and 224:

Table 85 (Cont.): System bus AC and

- Page 225 and 226:

APPENDIX A ALPHA ARCHITECTURE OPTIO

- Page 227 and 228:

Copyright © 1993 Digital Equipment

- Page 229 and 230:

Copyright © 1993 Digital Equipment

- Page 231 and 232:

Copyright © 1993 Digital Equipment

- Page 233 and 234:

Copyright © 1993 Digital Equipment

- Page 235 and 236:

Copyright © 1993 Digital Equipment

- Page 237 and 238:

Copyright © 1993 Digital Equipment

- Page 239 and 240:

Copyright © 1993 Digital Equipment

- Page 241 and 242:

Copyright © 1993 Digital Equipment

- Page 243 and 244:

Copyright © 1993 Digital Equipment

- Page 245 and 246:

Copyright © 1993 Digital Equipment

- Page 247 and 248:

Copyright © 1993 Digital Equipment

- Page 249 and 250:

Copyright © 1993 Digital Equipment

- Page 251 and 252:

Copyright © 1993 Digital Equipment

- Page 253 and 254:

Copyright © 1993 Digital Equipment

- Page 255 and 256:

Copyright © 1993 Digital Equipment

- Page 257 and 258:

INDEX 21064 IEEE floating point con

- Page 259 and 260:

Icache, 59 ICCSR, 19 IEEE Floating

- Page 261:

STQC cycle, 144 STxC cycle, 144 STx

![Volume 3: Instruction Set Reference [pdf]](https://img.yumpu.com/5683779/1/190x252/volume-3-instruction-set-reference-pdf.jpg?quality=85)