24531904_j

24531904_j 24531904_j

FXRSTOR—Restore FP and Intel ® MMX ® State and Streaming SIMD Extension State オペコード 命令 説明 0F,AE,/1 FXRSTOR m512byte 浮動小数点状態、インテル MMX テクノロジ状態、ストリーミング SIMD 拡張命令状態を m512byte からロードする。 操作 FP and MMX state and Streaming SIMD Extension state = m512byte; 説明 FXRSTOR 命令は、 m512byte に よ っ て定義 さ れる メ モ リ ・ エ リ アか ら 、 浮動小数点状態、 MMX テ ク ノ ロ ジ状態、 ス ト リ ー ミ ン グ SIMD 拡張命令状態 ( 環境 と レ ジ ス タ ) を再ロ ー ドする。 このデータは、 以前にFXSAVE によって書き込まれたものである。 浮動小数点命令、 MMX テ ク ノ ロ ジ命令、 ス ト リ ー ミ ング SIMD 拡張命令の環境 と レ ジ ス タ は、 次の よ う なデー タ構造を持つ ( メモリの構造に従ってリ ト ル ・ エンディアン ・ バイ ト を使用し、 各行のバイ ト ・ オ フ セ ッ ト を右の欄に示す )。 3:906 第 3 巻 : IA-32 ストリーミング SIMD 拡張命令リファレンス

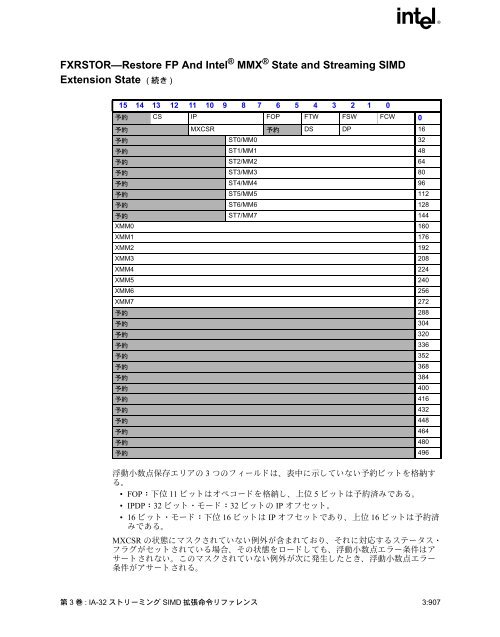

FXRSTOR—Restore FP And Intel ® MMX ® State and Streaming SIMD Extension State ( 続き ) 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 予約 CS IP FOP FTW FSW FCW 0 予約 MXCSR 予約 DS DP 16 予約 ST0/MM0 32 予約 ST1/MM1 48 予約 ST2/MM2 64 予約 ST3/MM3 80 予約 ST4/MM4 96 予約 ST5/MM5 112 予約 ST6/MM6 128 予約 ST7/MM7 144 XMM0 160 XMM1 176 XMM2 192 XMM3 208 XMM4 224 XMM5 240 XMM6 256 XMM7 272 予約 予約 予約 予約 予約 予約 予約 予約 予約 予約 予約 予約 予約 予約 浮動小数点保存エ リ アの 3 つの フ ィ ー ル ド は、 表中に示していない予約ビ ッ ト を格納す る。 • FOP :下位11 ビ ッ ト は オペ コ ー ド を格納し、 上位 5 ビッ トは予約済みである。 • IPDP : 32 ビッ ト ・モード :32 ビッ トのIP オフセッ ト。 • 16 ビッ ト ・モード :下位16 ビッ トはIP オフセッ トであり、 上位16 ビッ トは予約済 みである。 MXCSR の状態にマス ク されていない例外が含まれてお り 、 それに対応する ステ ー タ ス ・ フ ラ グがセ ッ ト されている場合、 その状態を ロ ー ド して も 、 浮動小数点エ ラ ー条件はア サ ー ト さ れない。 こ のマス ク さ れていない例外が次に発生した と き、 浮動小数点エラ ー 条件がアサー ト される。 第 3 巻 : IA-32 ストリーミング SIMD 拡張命令リファレンス 3:907 288 304 320 336 352 368 384 400 416 432 448 464 480 496

- Seite 868 und 869: MASKMOVQ (Non-temporal byte mask st

- Seite 870 und 871: 3.7.1 実数体系 図 3-8 に示

- Seite 872 und 873: て異なる。 バイアス定数

- Seite 874 und 875: 極端な場合には、 先頭の

- Seite 876 und 877: 3.8 データ・フォーマット

- Seite 878 und 879: 3.10 命令プリフィックス

- Seite 880 und 881: •xmm/m64: 128 ビット ・マル

- Seite 882 und 883: ADDPS—Packed Single-FP Add ( 続

- Seite 884 und 885: ADDSS—Scalar Single-FP Add ( 続

- Seite 886 und 887: ANDNPS—Bit-wise Logical And Not F

- Seite 888 und 889: ANDPS—Bit-wise Logical And for Si

- Seite 890 und 891: CMPPS—Packed Single-FP Compare (

- Seite 892 und 893: CMPPS—Packed Single-FP Compare (

- Seite 894 und 895: CMPSS—Scalar Single-FP Compare (

- Seite 896 und 897: CMPSS—Scalar Single-FP Compare (

- Seite 898 und 899: COMISS—Scalar Ordered Single-FP C

- Seite 900 und 901: CVTPI2PS—Packed Signed INT32 to P

- Seite 902 und 903: CVTPS2PI—Packed Single-FP to Pack

- Seite 904 und 905: CVTPS2PI—Packed Single-FP to Pack

- Seite 906 und 907: CVTSI2SS—Scalar Signed INT32 to S

- Seite 908 und 909: CVTSS2SI—Scalar Single-FP to Sign

- Seite 910 und 911: CVTTPS2PI—Packed Single-FP to Pac

- Seite 912 und 913: CVTTSS2SI—Scalar Single-FP to Sig

- Seite 914 und 915: DIVPS—Packed Single-FP Divide オ

- Seite 916 und 917: DIVSS—Scalar Single-FP Divide オ

- Seite 920 und 921: FXRSTOR—Restore FP And Intel ® M

- Seite 922 und 923: FXSAVE—Store FP and Intel ® MMX

- Seite 924 und 925: FXSAVE—Store FP and Intel ® MMX

- Seite 926 und 927: FXSAVE—Store FP and Intel ® MMX

- Seite 928 und 929: LDMXCSR—Load Streaming SIMD Exten

- Seite 930 und 931: MAXPS—Packed Single-FP Maximum

- Seite 932 und 933: MAXSS—Scalar Single-FP Maximum

- Seite 934 und 935: MINPS—Packed Single-FP Minimum

- Seite 936 und 937: MINSS—Scalar Single-FP Minimum

- Seite 938 und 939: MOVAPS—Move Aligned Four Packed S

- Seite 940 und 941: MOVHLPS—Move High to Low Packed S

- Seite 942 und 943: MOVHPS—Move High Packed Single-FP

- Seite 944 und 945: MOVLHPS—Move Low to High Packed S

- Seite 946 und 947: MOVLPS—Move Low Packed Single-FP

- Seite 948 und 949: MOVMSKPS—Move Mask To Integer オ

- Seite 950 und 951: MOVSS—Move Scalar Single-FP オ

- Seite 952 und 953: MOVUPS—Move Unaligned Four Packed

- Seite 954 und 955: MOVUPS—Move Unaligned Four Packed

- Seite 956 und 957: MULPS—Packed Single-FP Multiply (

- Seite 958 und 959: MULSS—Scalar Single-FP Multiply (

- Seite 960 und 961: ORPS—Bit-wise Logical OR for Sing

- Seite 962 und 963: RCPPS—Packed Single-FP Reciprocal

- Seite 964 und 965: RCPSS—Scalar Single-FP Reciprocal

- Seite 966 und 967: RSQRTPS—Packed Single-FP Square R

FXRSTOR—Restore FP And Intel ® MMX ® State and Streaming SIMD<br />

Extension State ( 続き )<br />

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br />

予約 CS IP FOP FTW FSW FCW 0<br />

予約 MXCSR 予約 DS DP 16<br />

予約 ST0/MM0 32<br />

予約 ST1/MM1 48<br />

予約 ST2/MM2 64<br />

予約 ST3/MM3 80<br />

予約 ST4/MM4 96<br />

予約 ST5/MM5 112<br />

予約 ST6/MM6 128<br />

予約 ST7/MM7 144<br />

XMM0 160<br />

XMM1 176<br />

XMM2 192<br />

XMM3 208<br />

XMM4 224<br />

XMM5 240<br />

XMM6 256<br />

XMM7 272<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

予約<br />

浮動小数点保存エ リ アの 3 つの フ ィ ー ル ド は、 表中に示していない予約ビ ッ ト を格納す<br />

る。<br />

• FOP :下位11 ビ ッ ト は オペ コ ー ド を格納し、 上位 5 ビッ トは予約済みである。<br />

• IPDP : 32 ビッ ト ・モード :32 ビッ トのIP オフセッ ト。<br />

• 16 ビッ ト ・モード :下位16 ビッ トはIP オフセッ トであり、 上位16 ビッ トは予約済<br />

みである。<br />

MXCSR の状態にマス ク されていない例外が含まれてお り 、 それに対応する ステ ー タ ス ・<br />

フ ラ グがセ ッ ト されている場合、 その状態を ロ ー ド して も 、 浮動小数点エ ラ ー条件はア<br />

サ ー ト さ れない。 こ のマス ク さ れていない例外が次に発生した と き、 浮動小数点エラ ー<br />

条件がアサー ト される。<br />

第 3 巻 : IA-32 ストリーミング SIMD 拡張命令リファレンス 3:907<br />

288<br />

304<br />

320<br />

336<br />

352<br />

368<br />

384<br />

400<br />

416<br />

432<br />

448<br />

464<br />

480<br />

496