24531904_j

24531904_j 24531904_j

ANDNPS—Bit-wise Logical And Not For Single-FP ( 続き ) 追加の Itanium ベース・システム環境例外 Itanium アーキテクチャ ・ レジスタ ・ フォルト Itanium アーキテクチャ ・ メモリ ・ フォル ト 浮動小数点レ ジ ス タ無効フ ォ ル ト (PSR.dfl が 1 の場合 )、 NaT レ ジ ス タ参照フ ォ ル ト 。 VHPT データ ・ フォル ト、 データ TLB フォルト、 代替 データ TLB フォルト、 データ・ページ不在フォルト、 データ NaT ページ参照アボー ト、 データ ・ キー ・ ミ ス ・ フォルト、 データ・キー許可フォルト、 データ・アクセス 権フォルト、 データ・アクセス・ビット ・フォルト。 コメント ANDNPS での リ ピー ト ・ プ リ フ ィ ッ クス (F2H,F3H) の使用は予約済みである。 このプ リ フ ィ ッ ク スの処理は、 プ ロ セ ッ サに よ っ て変わ る可能性があ る。 ANDNPS でこのプリ フ ィ ッ ク ス を使用す る と 、 将来のプ ロ セ ッ サ と の互換性を損な う おそれがある。 3:874 第 3 巻 : IA-32 ストリーミング SIMD 拡張命令リファレンス

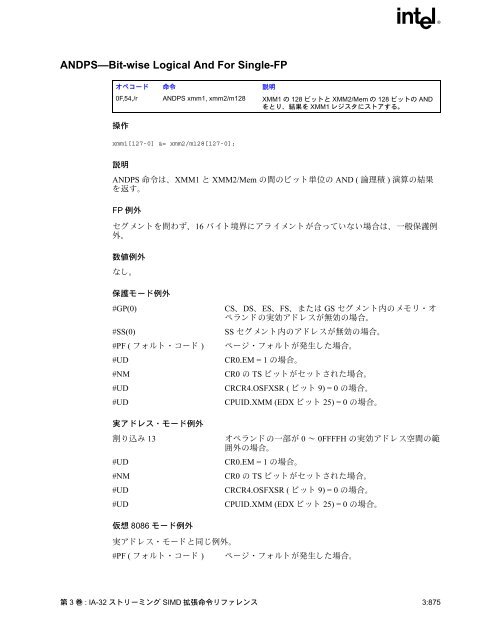

ANDPS—Bit-wise Logical And For Single-FP オペコード 命令 説明 0F,54,/r ANDPS xmm1, xmm2/m128 XMM1 の 128 ビットと XMM2/Mem の 128 ビットの AND をとり、結果を XMM1 レジスタにストアする。 操作 xmm1[127-0] &= xmm2/m128[127-0]; 説明 ANDPS 命令は、 XMM1 と XMM2/Mem の間の ビ ッ ト 単位の AND ( 論理積 ) 演算の結果 を返す。 FP 例外 セグメン ト を問わず、 16 バイ ト 境界にアラ イ メ ン ト が合 っ ていない場合は、 一般保護例 外。 数値例外 なし。 保護モード例外 #GP(0) CS、 DS、 ES、 FS、 または GS セグメン ト 内のメモ リ ・ オ ペラン ドの実効アドレスが無効の場合。 #SS(0) SS セグメン ト 内のアド レスが無効の場合。 #PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。 #UD CR0.EM = 1 の場合。 #NM CR0 の TS ビ ッ ト がセ ッ ト さ れた場合。 #UD CRCR4.OSFXSR ( ビッ ト 9) = 0 の場合。 #UD CPUID.XMM (EDX ビッ ト 25) = 0 の場合。 実アドレス・モード例外 割り込み 13 オペラン ド の一部が 0 ~ 0FFFFH の実効ア ド レス空間の範 囲外の場合。 #UD CR0.EM = 1 の場合。 #NM CR0 の TS ビ ッ ト がセ ッ ト さ れた場合。 #UD CRCR4.OSFXSR ( ビッ ト 9) = 0 の場合。 #UD CPUID.XMM (EDX ビッ ト 25) = 0 の場合。 仮想 8086 モード例外 実ア ド レ ス ・ モー ド と 同じ例外。 #PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。 第 3 巻 : IA-32 ストリーミング SIMD 拡張命令リファレンス 3:875

- Seite 836 und 837: PSRAW/PSRAD—Packed Shift Right Ar

- Seite 838 und 839: PSRLW/PSRLD/PSRLQ—Packed Shift Ri

- Seite 840 und 841: PSRLW/PSRLD/PSRLQ—Packed Shift Ri

- Seite 842 und 843: PSUBB/PSUBW/PSUBD—Packed Subtract

- Seite 844 und 845: PSUBSB/PSUBSW—Packed Subtract wit

- Seite 846 und 847: PSUBSB/PSUBSW—Packed Subtract wit

- Seite 848 und 849: PSUBUSB/PSUBUSW—Packed Subtract U

- Seite 850 und 851: PUNPCKHBW/PUNPCKHWD/PUNPCKHDQ—Unp

- Seite 852 und 853: PUNPCKHBW/PUNPCKHWD/PUNPCKHDQ—Unp

- Seite 854 und 855: PUNPCKLBW/PUNPCKLWD/PUNPCKLDQ—Unp

- Seite 856 und 857: PXOR—Logical Exclusive OR オペ

- Seite 858 und 859: 3:846 第 3 巻 : IA-32 MMX ® テ

- Seite 860 und 861: 令テ ク ノ ロジを組み込

- Seite 862 und 863: 図 3-3. パックド操作 図 3-4

- Seite 864 und 865: COMISS (Compare scalar single-preci

- Seite 866 und 867: scalar 32-bit integer) 命令は、

- Seite 868 und 869: MASKMOVQ (Non-temporal byte mask st

- Seite 870 und 871: 3.7.1 実数体系 図 3-8 に示

- Seite 872 und 873: て異なる。 バイアス定数

- Seite 874 und 875: 極端な場合には、 先頭の

- Seite 876 und 877: 3.8 データ・フォーマット

- Seite 878 und 879: 3.10 命令プリフィックス

- Seite 880 und 881: •xmm/m64: 128 ビット ・マル

- Seite 882 und 883: ADDPS—Packed Single-FP Add ( 続

- Seite 884 und 885: ADDSS—Scalar Single-FP Add ( 続

- Seite 888 und 889: ANDPS—Bit-wise Logical And for Si

- Seite 890 und 891: CMPPS—Packed Single-FP Compare (

- Seite 892 und 893: CMPPS—Packed Single-FP Compare (

- Seite 894 und 895: CMPSS—Scalar Single-FP Compare (

- Seite 896 und 897: CMPSS—Scalar Single-FP Compare (

- Seite 898 und 899: COMISS—Scalar Ordered Single-FP C

- Seite 900 und 901: CVTPI2PS—Packed Signed INT32 to P

- Seite 902 und 903: CVTPS2PI—Packed Single-FP to Pack

- Seite 904 und 905: CVTPS2PI—Packed Single-FP to Pack

- Seite 906 und 907: CVTSI2SS—Scalar Signed INT32 to S

- Seite 908 und 909: CVTSS2SI—Scalar Single-FP to Sign

- Seite 910 und 911: CVTTPS2PI—Packed Single-FP to Pac

- Seite 912 und 913: CVTTSS2SI—Scalar Single-FP to Sig

- Seite 914 und 915: DIVPS—Packed Single-FP Divide オ

- Seite 916 und 917: DIVSS—Scalar Single-FP Divide オ

- Seite 918 und 919: FXRSTOR—Restore FP and Intel ® M

- Seite 920 und 921: FXRSTOR—Restore FP And Intel ® M

- Seite 922 und 923: FXSAVE—Store FP and Intel ® MMX

- Seite 924 und 925: FXSAVE—Store FP and Intel ® MMX

- Seite 926 und 927: FXSAVE—Store FP and Intel ® MMX

- Seite 928 und 929: LDMXCSR—Load Streaming SIMD Exten

- Seite 930 und 931: MAXPS—Packed Single-FP Maximum

- Seite 932 und 933: MAXSS—Scalar Single-FP Maximum

- Seite 934 und 935: MINPS—Packed Single-FP Minimum

ANDPS—Bit-wise Logical And For Single-FP<br />

オペコード 命令 説明<br />

0F,54,/r ANDPS xmm1, xmm2/m128 XMM1 の 128 ビットと XMM2/Mem の 128 ビットの AND<br />

をとり、結果を XMM1 レジスタにストアする。<br />

操作<br />

xmm1[127-0] &= xmm2/m128[127-0];<br />

説明<br />

ANDPS 命令は、 XMM1 と XMM2/Mem の間の ビ ッ ト 単位の AND ( 論理積 ) 演算の結果<br />

を返す。<br />

FP 例外<br />

セグメン ト を問わず、 16 バイ ト 境界にアラ イ メ ン ト が合 っ ていない場合は、 一般保護例<br />

外。<br />

数値例外<br />

なし。<br />

保護モード例外<br />

#GP(0) CS、 DS、 ES、 FS、 または GS セグメン ト 内のメモ リ ・ オ<br />

ペラン ドの実効アドレスが無効の場合。 #SS(0) SS セグメン ト 内のアド レスが無効の場合。<br />

#PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。<br />

#UD CR0.EM = 1 の場合。<br />

#NM CR0 の TS ビ ッ ト がセ ッ ト さ れた場合。<br />

#UD CRCR4.OSFXSR ( ビッ ト 9) = 0 の場合。<br />

#UD CPUID.XMM (EDX ビッ ト 25) = 0 の場合。<br />

実アドレス・モード例外<br />

割り込み 13 オペラン ド の一部が 0 ~ 0FFFFH の実効ア ド レス空間の範<br />

囲外の場合。<br />

#UD CR0.EM = 1 の場合。<br />

#NM CR0 の TS ビ ッ ト がセ ッ ト さ れた場合。<br />

#UD CRCR4.OSFXSR ( ビッ ト 9) = 0 の場合。<br />

#UD CPUID.XMM (EDX ビッ ト 25) = 0 の場合。<br />

仮想 8086 モード例外<br />

実ア ド レ ス ・ モー ド と 同じ例外。<br />

#PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。<br />

第 3 巻 : IA-32 ストリーミング SIMD 拡張命令リファレンス 3:875