24531904_j

24531904_j 24531904_j

MOV—Move ( 続き ) #GP( セレクタ ) セグメン ト ・ セレ ク タ ・ インデッ クスがデ ィ スク リ プタ ・ テーブルの範囲外の場合。 SS レジスタがロード され、 セグメント ・セレクタのRPL およびセグメント ・ディスク リプタの DPL が CPL に等し くない場合。 SS レ ジ ス タ がロ ー ド さ れ、 指示先のセグ メ ン ト が書き込 み不可能なデー タ ・ セグメン ト である場合。 DS、 ES、 FS、 または GS レジスタがロード され、 指示先 のセグメン ト がデータ ・ セグメン ト または書き込み可能な コード ・セグメントでない場合。 DS、 ES、 FS、 または GS レジスタがロード され、 指示先 のセグメン ト がデータ ・ セグメン ト または非コ ンフ ォ ー ミ ング ・ コー ド ・ セグメン ト であるが、 RPL と CPL の両方 ともDPL よ り 大き い場合。 #SS(0) メモリ ・ オペランドの実効アドレスが SS セグメン ト の範 囲外の場合。 #SS( セレクタ ) SS レ ジ ス タ がロ ー ド さ れ、 指示先のセグ メ ン ト が存在し ないとマー ク されている場合。 #NP DS、 ES、 FS、 または GS レジスタがロード され、 指示先 のセグメン ト が存在しないと マー ク されている場合。 #PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。 #AC(0) 現行特権レベルが 3 のときに、 アライメント ・チェックが イネーブルにされていて、 アライメントが合わないメモリ 参照が行われた場合。 #UD CS レ ジ ス タ を ロ ー ド し よ う と した場合。 実アドレス・モード例外 #GP メモリ ・ オペランドの実効アドレスが CS、 DS、 ES、 FS、 または GS セグ メ ン ト の範囲外の場合。 #SS メモリ ・ オペランドの実効アドレスが SS セグメン ト の範 囲外の場合。 #UD CS レ ジ ス タ を ロ ー ド し よ う と した場合。 仮想 8086 モード例外 #GP(0) メモリ ・ オペランドの実効アドレスが CS、 DS、 ES、 FS、 または GS セグ メ ン ト の範囲外の場合。 #SS(0) メモリ ・ オペランドの実効アドレスが SS セグメン ト の範 囲外の場合。 #PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。 #AC(0) アライメン ト ・ チェ ッ クがイネーブルにされていて、 アラ イ メン ト が合わないメモ リ 参照が行われた場合。 #UD CS レ ジ ス タ を ロ ー ド し よ う と した場合。 3:658 第 3 巻 : IA-32 基本命令リファレンス

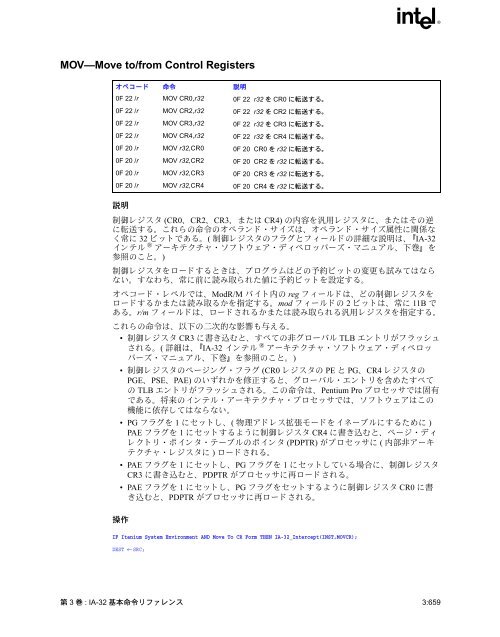

MOV—Move to/from Control Registers オペコード 命令 説明 0F 22 /r MOV CR0,r32 0F 22 r32 を CR0 に転送する。 0F 22 /r MOV CR2,r32 0F 22 r32 を CR2 に転送する。 0F 22 /r MOV CR3,r32 0F 22 r32 を CR3 に転送する。 0F 22 /r MOV CR4,r32 0F 22 r32 を CR4 に転送する。 0F 20 /r MOV r32,CR0 0F 20 CR0 を r32 に転送する。 0F 20 /r MOV r32,CR2 0F 20 CR2 を r32 に転送する。 0F 20 /r MOV r32,CR3 0F 20 CR3 を r32 に転送する。 0F 20 /r MOV r32,CR4 0F 20 CR4 を r32 に転送する。 説明 制御レ ジ ス タ (CR0、 CR2、 CR3、 または CR4) の内容を汎用レ ジス タに、 ま たはその逆 に転送す る。 こ れ ら の命令のオペラ ン ド ・ サイ ズは、 オペラ ン ド ・ サイ ズ属性に関係な く常に32 ビッ トである。 ( 制御レ ジ ス タ の フ ラ グ と フ ィ ー ル ド の詳細な説明は、 『IA-32 インテル ® アーキテクチャ ・ ソフ ト ウェア ・ディベロッパーズ ・マニュアル、 下巻』 を 参照の こ と 。 ) 制御レ ジ ス タ を ロ ー ド する と き は、 プ ロ グ ラ ム は ど の予約ビ ッ ト の変更 も 試みてはな ら ない。 すなわ ち、 常に前に読み取られた値に予約ビ ッ ト を設定する。 オペコ ー ド ・ レベルでは、 ModR/M バイ ト内の reg フィールドは、 どの制御レジスタを ロー ドするかまたは読み取るかを指定する。 mod フィールドの2 ビッ トは、 常に11B で ある。 r/m フ ィ ールドは、 ロー ド されるかまたは読み取られる汎用レジスタを指定する。 こ れ ら の命令は、 以下の二次的な影響 も 与え る。 • 制御レ ジ ス タ CR3 に書き込むと、 すべての非グローバル TLB エン ト リがフラ ッ シュ される。 ( 詳細は、 『IA-32 インテル ® アーキテクチャ・ソフトウェア・ディベロッ パーズ ・ マニュアル、 下巻』 を参照のこ と。 ) • 制御レジスタのページング ・ フラグ (CR0 レジスタのPE と PG、 CR4 レジスタの PGE、 PSE、 PAE) のいずれかを修正す る と 、 グ ロ ー バル ・ エン ト リ を含めたすべて の TLB エン ト リがフラ ッ シュ される。 この命令は、 Pentium Pro プロセッサでは固有 である。 将来のインテル・アーキテクチャ・プロセッサでは、 ソフトウェアはこの 機能に依存してはな ら ない。 • PG フラグを 1 にセッ ト し、 ( 物理ア ド レ ス拡張モー ド を イ ネ ー ブルにするために ) PAE フラグを1 にセッ ト する よ う に制御レジスタ CR4 に書き込む と、 ページ ・ デ ィ レクト リ ・ポインタ ・テーブルのポインタ (PDPTR) がプロセッサに ( 内部非アー キ テクチャ ・ レジスタに) ロード される。 • PAE フラグを1 にセッ ト し、 PG フラグを 1 にセ ッ ト してい る場合に、 制御レ ジ ス タ CR3 に書き込む と、 PDPTR がプロセッサに再ロー ド される。 • PAE フラグを1 にセッ ト し、 PG フラグをセットするように制御レジスタCR0 に書 き込むと、 PDPTR がプロセッサに再ロー ド される。 操作 IF Itanium System Environment AND Move To CR Form THEN IA-32_Intercept(INST,MOVCR); DEST ← SRC; 第 3 巻 : IA-32 基本命令リファレンス 3:659

- Seite 620 und 621: Jcc—Jump if Condition Is Met オ

- Seite 622 und 623: Jcc—Jump if Condition Is Met (

- Seite 624 und 625: JMP—Jump オペコード 命令

- Seite 626 und 627: JMP—Jump ( 続き ) 操作 IF nea

- Seite 628 und 629: JMP—Jump ( 続き ) END; TASK-GAT

- Seite 630 und 631: JMP—Jump ( 続き ) #PF ( フォ

- Seite 632 und 633: JMPE—Jump to Intel ® Itanium ®

- Seite 634 und 635: LAR—Load Access Rights Byte オ

- Seite 636 und 637: LAR—Load Access Rights Byte ( 続

- Seite 638 und 639: LDS/LES/LFS/LGS/LSS—Load Far Poin

- Seite 640 und 641: LEA—Load Effective Address オペ

- Seite 642 und 643: LEAVE—High Level Procedure Exit

- Seite 644 und 645: LES—Load Full Pointer 「LDS/LES/

- Seite 646 und 647: LGDT/LIDT—Load Global/Interrupt D

- Seite 648 und 649: LGS—Load Full Pointer 「LDS/LES/

- Seite 650 und 651: LLDT—Load Local Descriptor Table

- Seite 652 und 653: LMSW—Load Machine Status Word オ

- Seite 654 und 655: LOCK—Assert LOCK# Signal Prefix

- Seite 656 und 657: LODS/LODSB/LODSW/LODSD—Load Strin

- Seite 658 und 659: LODS/LODSB/LODSW/LODSD—Load Strin

- Seite 660 und 661: LOOP/LOOPcc—Loop According to ECX

- Seite 662 und 663: LSL—Load Segment Limit ( 続き )

- Seite 664 und 665: LSS—Load Full Pointer 「LDS/LES/

- Seite 666 und 667: LTR—Load Task Register ( 続き )

- Seite 668 und 669: MOV—Move ( 続き ) デスティ

- Seite 672 und 673: MOV—Move to/from Control Register

- Seite 674 und 675: MOV—Move to/from Debug Registers

- Seite 676 und 677: MOVS/MOVSB/MOVSW/MOVSD—Move Data

- Seite 678 und 679: MOVSX—Move with Sign-Extension

- Seite 680 und 681: MOVZX—Move with Zero-Extend オ

- Seite 682 und 683: MUL—Unsigned Multiplication of AL

- Seite 684 und 685: NEG—Two's Complement Negation オ

- Seite 686 und 687: NOP—No Operation オペコード

- Seite 688 und 689: NOT—One's Complement Negation (

- Seite 690 und 691: OR—Logical Inclusive OR ( 続き

- Seite 692 und 693: OUT—Output to Port ( 続き ) 操

- Seite 694 und 695: OUTS/OUTSB/OUTSW/OUTSD—Output Str

- Seite 696 und 697: OUTS/OUTSB/OUTSW/OUTSD—Output Str

- Seite 698 und 699: POP—Pop a Value from the Stack

- Seite 700 und 701: POP—Pop a Value from the Stack (

- Seite 702 und 703: POP—Pop a Value from the Stack (

- Seite 704 und 705: POPA/POPAD—Pop All General-Purpos

- Seite 706 und 707: POPF/POPFD—Pop Stack into EFLAGS

- Seite 708 und 709: PUSH—Push Word or Doubleword onto

- Seite 710 und 711: PUSH—Push Word or Doubleword onto

- Seite 712 und 713: PUSHA/PUSHAD—Push All General-Pur

- Seite 714 und 715: PUSHF/PUSHFD—Push EFLAGS Register

- Seite 716 und 717: RCL/RCR/ROL/ROR-—Rotate ( 続き

- Seite 718 und 719: RCL/RCR/ROL/ROR-—Rotate ( 続き

MOV—Move to/from Control Registers<br />

オペコード 命令 説明<br />

0F 22 /r MOV CR0,r32 0F 22 r32 を CR0 に転送する。<br />

0F 22 /r MOV CR2,r32 0F 22 r32 を CR2 に転送する。<br />

0F 22 /r MOV CR3,r32 0F 22 r32 を CR3 に転送する。<br />

0F 22 /r MOV CR4,r32 0F 22 r32 を CR4 に転送する。<br />

0F 20 /r MOV r32,CR0 0F 20 CR0 を r32 に転送する。<br />

0F 20 /r MOV r32,CR2 0F 20 CR2 を r32 に転送する。<br />

0F 20 /r MOV r32,CR3 0F 20 CR3 を r32 に転送する。<br />

0F 20 /r MOV r32,CR4 0F 20 CR4 を r32 に転送する。<br />

説明<br />

制御レ ジ ス タ (CR0、 CR2、 CR3、 または CR4) の内容を汎用レ ジス タに、 ま たはその逆<br />

に転送す る。 こ れ ら の命令のオペラ ン ド ・ サイ ズは、 オペラ ン ド ・ サイ ズ属性に関係な<br />

く常に32 ビッ トである。 ( 制御レ ジ ス タ の フ ラ グ と フ ィ ー ル ド の詳細な説明は、 『IA-32<br />

インテル ® アーキテクチャ ・ ソフ ト ウェア ・ディベロッパーズ ・マニュアル、 下巻』 を<br />

参照の こ と 。 )<br />

制御レ ジ ス タ を ロ ー ド する と き は、 プ ロ グ ラ ム は ど の予約ビ ッ ト の変更 も 試みてはな ら<br />

ない。 すなわ ち、 常に前に読み取られた値に予約ビ ッ ト を設定する。<br />

オペコ ー ド ・ レベルでは、 ModR/M バイ ト内の reg フィールドは、 どの制御レジスタを<br />

ロー ドするかまたは読み取るかを指定する。 mod フィールドの2 ビッ トは、 常に11B で<br />

ある。 r/m フ ィ ールドは、 ロー ド されるかまたは読み取られる汎用レジスタを指定する。<br />

こ れ ら の命令は、 以下の二次的な影響 も 与え る。<br />

• 制御レ ジ ス タ CR3 に書き込むと、 すべての非グローバル TLB エン ト リがフラ ッ シュ<br />

される。 ( 詳細は、 『IA-32 インテル ® アーキテクチャ・ソフトウェア・ディベロッ<br />

パーズ ・ マニュアル、 下巻』 を参照のこ と。 )<br />

• 制御レジスタのページング ・ フラグ (CR0 レジスタのPE と PG、 CR4 レジスタの<br />

PGE、 PSE、 PAE) のいずれかを修正す る と 、 グ ロ ー バル ・ エン ト リ を含めたすべて<br />

の TLB エン ト リがフラ ッ シュ される。 この命令は、 Pentium Pro プロセッサでは固有<br />

である。 将来のインテル・アーキテクチャ・プロセッサでは、 ソフトウェアはこの<br />

機能に依存してはな ら ない。<br />

• PG フラグを 1 にセッ ト し、 ( 物理ア ド レ ス拡張モー ド を イ ネ ー ブルにするために )<br />

PAE フラグを1 にセッ ト する よ う に制御レジスタ CR4 に書き込む と、 ページ ・ デ ィ<br />

レクト リ ・ポインタ ・テーブルのポインタ (PDPTR) がプロセッサに ( 内部非アー キ<br />

テクチャ ・ レジスタに) ロード される。<br />

• PAE フラグを1 にセッ ト し、 PG フラグを 1 にセ ッ ト してい る場合に、 制御レ ジ ス タ<br />

CR3 に書き込む と、 PDPTR がプロセッサに再ロー ド される。<br />

• PAE フラグを1 にセッ ト し、 PG フラグをセットするように制御レジスタCR0 に書<br />

き込むと、 PDPTR がプロセッサに再ロー ド される。<br />

操作<br />

IF Itanium System Environment AND Move To CR Form THEN IA-32_Intercept(INST,MOVCR);<br />

DEST ← SRC;<br />

第 3 巻 : IA-32 基本命令リファレンス 3:659