24531904_j

24531904_j 24531904_j

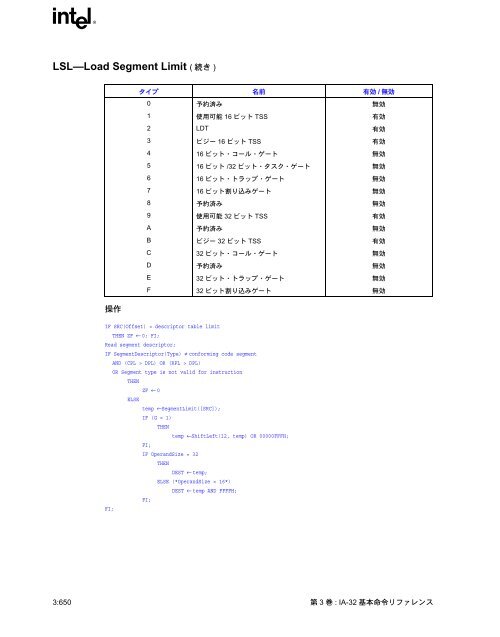

LSL—Load Segment Limit ( 続き ) 操作 タイプ 名前 有効 / 無効 0 予約済み 無効 1 使用可能 16 ビット TSS 有効 2 LDT 有効 3 ビジー 16 ビット TSS 有効 4 16 ビット・コール・ゲート 無効 5 16 ビット /32 ビット・タスク・ゲート 無効 6 16 ビット・トラップ・ゲート 無効 7 16 ビット割り込みゲート 無効 8 予約済み 無効 9 使用可能 32 ビット TSS 有効 A 予約済み 無効 B ビジー 32 ビット TSS 有効 C 32 ビット・コール・ゲート 無効 D 予約済み 無効 E 32 ビット・トラップ・ゲート 無効 F 32 ビット割り込みゲート 無効 IF SRC(Offset) > descriptor table limit THEN ZF ← 0; FI; Read segment descriptor; IF SegmentDescriptor(Type) ≠ conforming code segment AND (CPL > DPL) OR (RPL > DPL) OR Segment type is not valid for instruction THEN ZF ← 0 ELSE temp ← SegmentLimit([SRC]); IF (G = 1) THEN temp ← ShiftLeft(12, temp) OR 00000FFFH; FI; IF OperandSize = 32 THEN DEST ← temp; ELSE (*OperandSize = 16*) DEST ← temp AND FFFFH; FI; FI; 3:650 第 3 巻 : IA-32 基本命令リファレンス

LSL—Load Segment Limit ( 続き ) 影響を受けるフラグ セグメン ト範囲が正常にロー ド された場合は ZF フラグが1 にセッ ト され、 ロー ド でき なか っ た場合は 0 にク リアされる。 追加の Itanium ベース・システム環境例外 Itanium アーキテクチャ ・ レジスタ ・ フォルト Itanium アーキテクチャ ・ メモリ ・ フォル ト 保護モード例外 #GP(0) メモリ ・ オペランドの実効アドレスが CS、 DS、 ES、 FS、 または GS セグ メ ン ト の範囲外の場合。 DS、 ES、 FS、 または GS レジスタを使用してメモリがア クセスされ、 レジスタの内容が NULL セグメン ト ・ セレ クタであった場合。 #SS(0) メモリ ・ オペランドの実効アドレスが SS セグメン ト の範 囲外の場合。 #PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。 #AC(0) 現行特権レベルが 3 のときに、 アライメント ・チェックが イネーブルにされていて、 アライメントが合わないメモリ 参照が行われた場合。 実アドレス・モード例外 #UD LSL 命令は実ア ド レ ス ・ モ ー ド では認識 さ れない。 仮想 8086 モード例外 NaT レ ジ ス タ参照アボ ー ト 。 VHPT データ ・ フォル ト、 ネス ト された TLB フォルト、 データ TLB フォルト、 代替データTLB フォルト、 デー タ・ページ不在フォルト、 データNaT ページ参照アボー ト、 データ・キー・ ミス・フォルト、 データ・キー許可 フォルト、 データ・アクセス権フォルト、 データ・アクセ ス・ビット ・フォルト、 データ・ダーティ ・ビット ・フォ ルト。 #UD LSL 命令は仮想 8086 モー ドでは認識されない。 第 3 巻 : IA-32 基本命令リファレンス 3:651

- Seite 612 und 613: IRET/IRETD—Interrupt Return オ

- Seite 614 und 615: IRET/IRETD—Interrupt Return ( 続

- Seite 616 und 617: IRET/IRETD—Interrupt Return ( 続

- Seite 618 und 619: IRET/IRETD—Interrupt Return ( 続

- Seite 620 und 621: Jcc—Jump if Condition Is Met オ

- Seite 622 und 623: Jcc—Jump if Condition Is Met (

- Seite 624 und 625: JMP—Jump オペコード 命令

- Seite 626 und 627: JMP—Jump ( 続き ) 操作 IF nea

- Seite 628 und 629: JMP—Jump ( 続き ) END; TASK-GAT

- Seite 630 und 631: JMP—Jump ( 続き ) #PF ( フォ

- Seite 632 und 633: JMPE—Jump to Intel ® Itanium ®

- Seite 634 und 635: LAR—Load Access Rights Byte オ

- Seite 636 und 637: LAR—Load Access Rights Byte ( 続

- Seite 638 und 639: LDS/LES/LFS/LGS/LSS—Load Far Poin

- Seite 640 und 641: LEA—Load Effective Address オペ

- Seite 642 und 643: LEAVE—High Level Procedure Exit

- Seite 644 und 645: LES—Load Full Pointer 「LDS/LES/

- Seite 646 und 647: LGDT/LIDT—Load Global/Interrupt D

- Seite 648 und 649: LGS—Load Full Pointer 「LDS/LES/

- Seite 650 und 651: LLDT—Load Local Descriptor Table

- Seite 652 und 653: LMSW—Load Machine Status Word オ

- Seite 654 und 655: LOCK—Assert LOCK# Signal Prefix

- Seite 656 und 657: LODS/LODSB/LODSW/LODSD—Load Strin

- Seite 658 und 659: LODS/LODSB/LODSW/LODSD—Load Strin

- Seite 660 und 661: LOOP/LOOPcc—Loop According to ECX

- Seite 664 und 665: LSS—Load Full Pointer 「LDS/LES/

- Seite 666 und 667: LTR—Load Task Register ( 続き )

- Seite 668 und 669: MOV—Move ( 続き ) デスティ

- Seite 670 und 671: MOV—Move ( 続き ) #GP( セレ

- Seite 672 und 673: MOV—Move to/from Control Register

- Seite 674 und 675: MOV—Move to/from Debug Registers

- Seite 676 und 677: MOVS/MOVSB/MOVSW/MOVSD—Move Data

- Seite 678 und 679: MOVSX—Move with Sign-Extension

- Seite 680 und 681: MOVZX—Move with Zero-Extend オ

- Seite 682 und 683: MUL—Unsigned Multiplication of AL

- Seite 684 und 685: NEG—Two's Complement Negation オ

- Seite 686 und 687: NOP—No Operation オペコード

- Seite 688 und 689: NOT—One's Complement Negation (

- Seite 690 und 691: OR—Logical Inclusive OR ( 続き

- Seite 692 und 693: OUT—Output to Port ( 続き ) 操

- Seite 694 und 695: OUTS/OUTSB/OUTSW/OUTSD—Output Str

- Seite 696 und 697: OUTS/OUTSB/OUTSW/OUTSD—Output Str

- Seite 698 und 699: POP—Pop a Value from the Stack

- Seite 700 und 701: POP—Pop a Value from the Stack (

- Seite 702 und 703: POP—Pop a Value from the Stack (

- Seite 704 und 705: POPA/POPAD—Pop All General-Purpos

- Seite 706 und 707: POPF/POPFD—Pop Stack into EFLAGS

- Seite 708 und 709: PUSH—Push Word or Doubleword onto

- Seite 710 und 711: PUSH—Push Word or Doubleword onto

LSL—Load Segment Limit ( 続き )<br />

操作<br />

タイプ 名前 有効 / 無効<br />

0 予約済み 無効<br />

1 使用可能 16 ビット TSS 有効<br />

2 LDT 有効<br />

3 ビジー 16 ビット TSS 有効<br />

4 16 ビット・コール・ゲート 無効<br />

5 16 ビット /32 ビット・タスク・ゲート 無効<br />

6 16 ビット・トラップ・ゲート 無効<br />

7 16 ビット割り込みゲート 無効<br />

8 予約済み 無効<br />

9 使用可能 32 ビット TSS 有効<br />

A 予約済み 無効<br />

B ビジー 32 ビット TSS 有効<br />

C 32 ビット・コール・ゲート 無効<br />

D 予約済み 無効<br />

E 32 ビット・トラップ・ゲート 無効<br />

F 32 ビット割り込みゲート 無効<br />

IF SRC(Offset) > descriptor table limit<br />

THEN ZF ← 0; FI;<br />

Read segment descriptor;<br />

IF SegmentDescriptor(Type) ≠ conforming code segment<br />

AND (CPL > DPL) OR (RPL > DPL)<br />

OR Segment type is not valid for instruction<br />

THEN<br />

ZF ← 0<br />

ELSE<br />

temp ← SegmentLimit([SRC]);<br />

IF (G = 1)<br />

THEN<br />

temp ← ShiftLeft(12, temp) OR 00000FFFH;<br />

FI;<br />

IF OperandSize = 32<br />

THEN<br />

DEST ← temp;<br />

ELSE (*OperandSize = 16*)<br />

DEST ← temp AND FFFFH;<br />

FI;<br />

FI;<br />

3:650 第 3 巻 : IA-32 基本命令リファレンス